# Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

# DESIGN ALTERNATIVES FOR RECURSIVE DIGITAL FILTERS USING ON-LINE ARITHMETIC

J. S. Fernando

November 1993 CSD-930040

# UNIVERSITY OF CALIFORNIA Los Angeles

# Design Alternatives for Recursive Digital Filters Using On-Line Arithmetic

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

John Susantha Fernando

© Copyright by John Susantha Fernando 1993

# TABLE OF CONTENTS

| 1 | Intr | oduction                                       | 1          |

|---|------|------------------------------------------------|------------|

|   | 1.1  | Problem Statement                              | 3          |

|   | 1.2  | Research Objectives                            | 3          |

|   | 1.3  | Dissertation Outline                           | 4          |

|   | 1.4  | Related Work                                   | 5          |

|   | 1.5  | Contributions                                  | 6          |

| 2 | Sch  | emes Based on Multipliers, Recoders and Adders | 8          |

|   | 2.1  | MSDF Multiplication Algorithm                  | 9          |

|   | 2.2  | Recoder Design                                 | 12         |

|   | 2.3  | Separate Multiplier (SM) Scheme                | 15         |

|   | 2.4  | Combined Multiplier (CM) Scheme                | 21         |

| 3 | AC   | Composite On-Line Scheme                       | 24         |

|   | 3.1  | Specification and Derivation of Recurrence     | 24         |

|   | 3.2  | Expression for On-Line Delay                   | 26         |

|   | 3.3  | Second-Order Radix-4 Implementations           | 28         |

|   | 3.4  | Performance and Cost                           | 31         |

| 4 | Sch  | emes Using On-Line Multiply-Add Modules        | 38         |

|   | 4.1  | Design of MA Module                            | 38         |

|   | 4.2  | Implementation of MA Module                    | 39         |

|   | 4.3  | Performance and Cost                           | 40         |

| 5 | Mu   | lti-Module Arrays                              | <b>4</b> 4 |

|   | 5.1  | Array of Composite Word Modules                | 44         |

|   | 5.2  | Array of MA Word Modules                       | 48         |

|   | 5.3  | Array of Composite Digit Stages                | 48         |

|   | 5.4  | Array of MA Digit Stages                       | 50         |

|   | 55   | Performance and Cost                           | 51         |

| 6  | Alg  | orithmic Transformations for Higher Performance 56        |  |

|----|------|-----------------------------------------------------------|--|

|    | 6.1  | Recursive Unfolding Method                                |  |

|    | 6.2  | Scattered Lookahead Method                                |  |

|    | 6.3  | Multi-Module Arrays with Lookahead                        |  |

| 7  | Lim  | it Cycle Oscillations                                     |  |

|    | 7.1  | Roundoff Error in On-Line Modules                         |  |

|    | 7.2  | Bound on Limit Cycle Amplitude                            |  |

|    | 7.3  | Comparison of Limit Cycle Amplitude Bounds                |  |

|    | 7.4  | Theoretical Bounds and Simulation Results                 |  |

| 8  | Dyr  | namic Scaling Scheme for Eliminating Oscillations 81      |  |

|    | 8.1  | Basis for DS Scheme                                       |  |

|    | 8.2  | Scaling Operations                                        |  |

|    | 8.3  | The Dynamic Scaling Algorithm                             |  |

|    | 8.4  | Implementation of DS scheme                               |  |

|    | 8.5  | Performance and Cost                                      |  |

| 9  | Eva  | luation                                                   |  |

|    | 9.1  | Evaluation of Implementations                             |  |

|    | 9.2  | Previous Implementations                                  |  |

|    | 9.3  | Non-Linear Oscillations: Bounds and Solutions             |  |

| 10 | Con  | clusion and Further Research                              |  |

|    |      | ventional Design of a Second-Order IIR Section with Scat- |  |

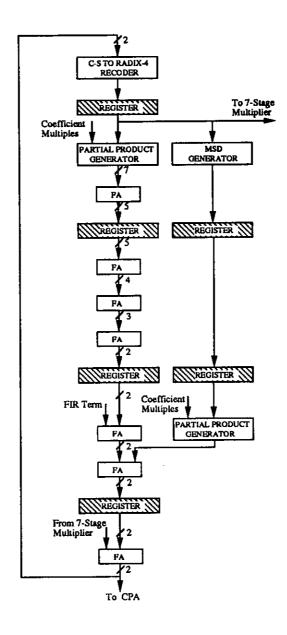

|    | A.1  | Architecture of 4-Stage Multiply-Add                      |  |

|    |      | Implementation                                            |  |

|    |      | Performance and Cost                                      |  |

| В  | Free | quency Responses of Filter Examples                       |  |

| R. | foro | 128                                                       |  |

# LIST OF FIGURES

| 2.1 | Scheme Using On-Line Units                                                                                  | 9  |

|-----|-------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Recurrence for Multiplication                                                                               | 11 |

| 2.3 | Multiplier Output $(Z_j)$ Computation                                                                       | 11 |

| 2.4 | Multiplier Implementation Schemes                                                                           | 13 |

| 2.5 | Recoder for [-3,9] to [-3,3]                                                                                | 16 |

| 2.6 | Recoder for [-9,9] to [-3,3]                                                                                | 17 |

| 2.7 | Signed-Digit Adder Implementation Schemes                                                                   | 19 |

| 2.8 | Separate Multiplier (SM) Scheme $(\delta_{imp} = 7) \dots \dots \dots$                                      | 20 |

| 2.9 | Combined Multiplier Scheme $(\delta_{imp} = 6) \dots \dots \dots$                                           | 23 |

| 3.1 | Composite 2-Stage On-Line Scheme $(\delta_{imp} = 4) \dots \dots$                                           | 32 |

| 3.2 | Optimizing Composite On-Line Scheme                                                                         | 33 |

| 3.3 | Optimized 2-Stage Composite On-Line Scheme $(\delta_{imp}=4)$                                               | 34 |

| 3.4 | Optimized 3-Stage Composite On-Line Scheme $(\delta_{imp}=4)$                                               | 35 |

| 4.1 | Optimizing Multiply-Add (MA) Scheme                                                                         | 41 |

| 4.2 | Optimized On-Line Multiply-Add (MA) Scheme $(\delta_{imp} = 4) \dots$                                       | 42 |

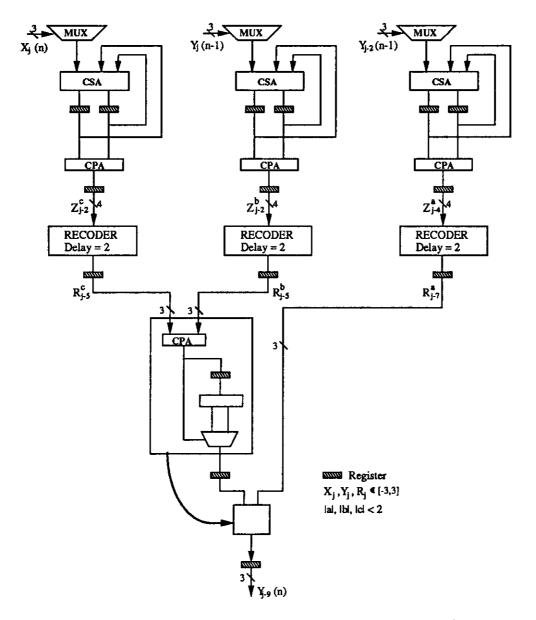

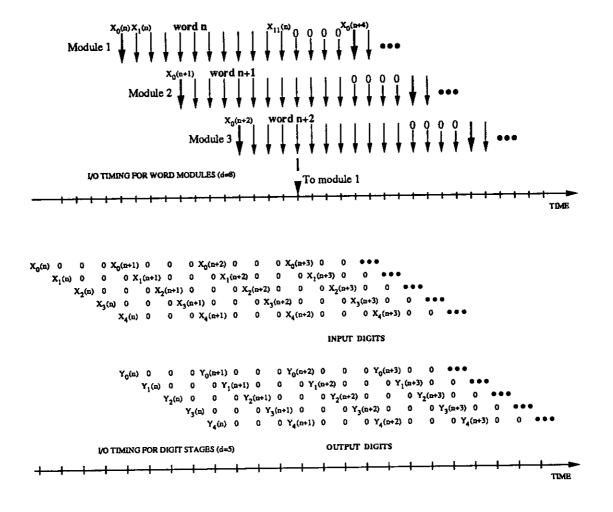

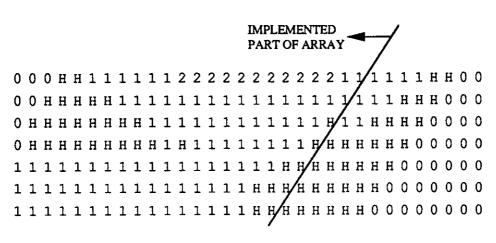

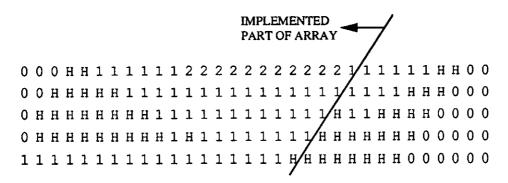

| 5.1 | Array of 2-Stage Composite Word Modules $(d = 8)$                                                           | 46 |

| 5.2 | I/O Timing for Array of 2-Stage Composite Word Modules $(d = 8)$                                            |    |

|     | and for Array of Composite Digit Stages $(d = 5) \dots \dots$                                               | 47 |

| 5.3 | Array of MA Word Modules $(d = 8) \dots \dots \dots$                                                        | 53 |

| 5.4 | Array of Composite Digit Stages $(d = 5)$                                                                   | 54 |

| 5.5 | Array of MA Digit Stages $(d = 5)$                                                                          | 55 |

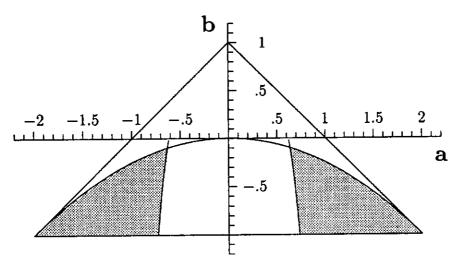

| 7.1 | Triangle of Stability and Region (shaded) of Complex Roots with Reduced Limit Cycle Amplitude Bounds for SL | 75 |

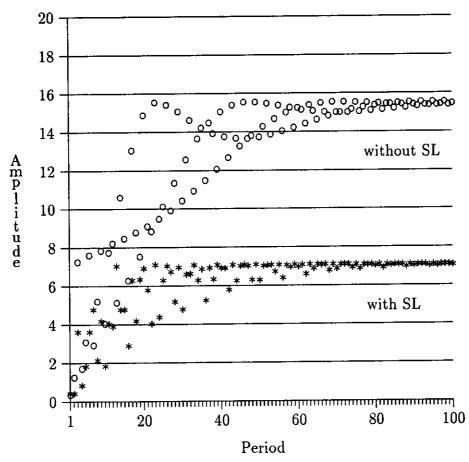

| 7.2 | Effect of SL on Limit Cycle Amplitude Bounds for F1 ( $a = -1.09$ , $b = -0.9$ )                            | 79 |

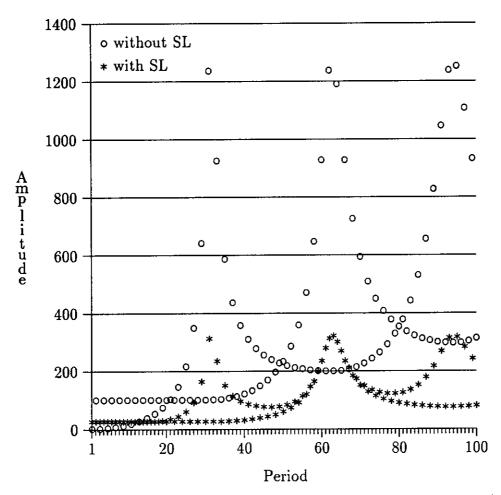

| 7.3 | Effect of SL on Limit Cycle Amplitude Bounds for F2 ( $a = -1.98$ , $b = -0.99$ )                           | 80 |

|     |                                                                                                             |    |

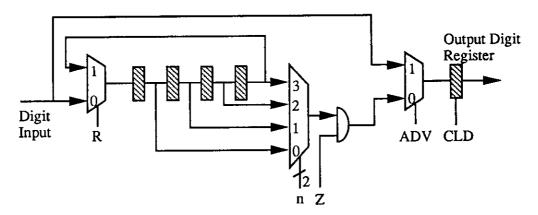

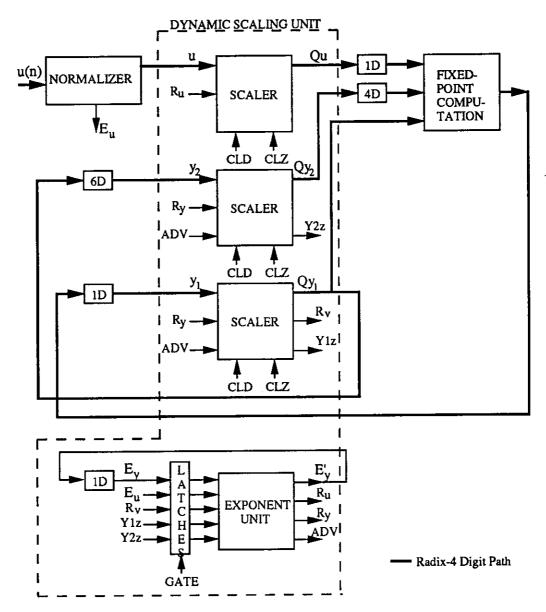

| 8.1         | Scaler Data Path for 8-digit On-line Operands                                                                                        | 85  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.2         | Block Diagram of DS Implementation                                                                                                   | 89  |

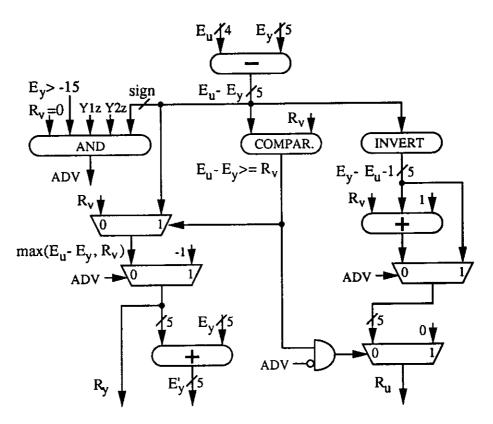

| 8.3         | Exponent Unit Computations                                                                                                           | 93  |

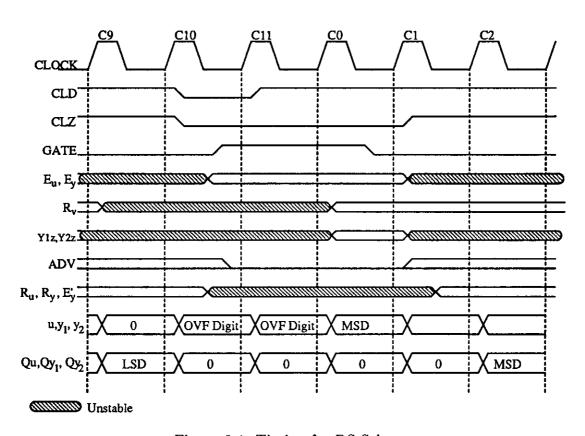

| 8.4         | Timing for DS Scheme                                                                                                                 | 94  |

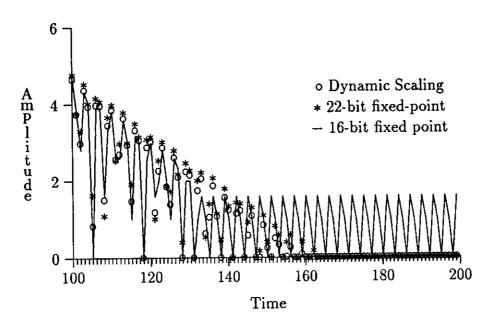

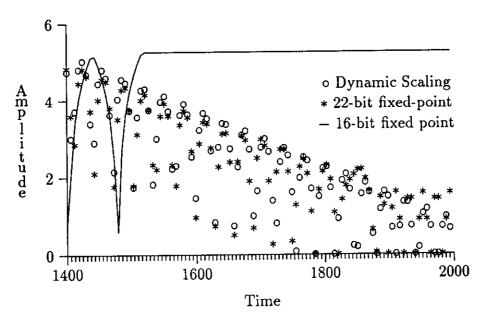

| 8.5         | Amplitude Response for F1 ( $a = -1.09$ , $b = -0.9$ ), amplitude= $log_2(16\text{-bit output}) \dots \dots \dots \dots \dots \dots$ | 95  |

| 8.6         | Amplitude Response for F2 ( $a = -1.98$ , $b = -0.99$ ), amplitude= $log_2(16\text{-bit output})$                                    | 95  |

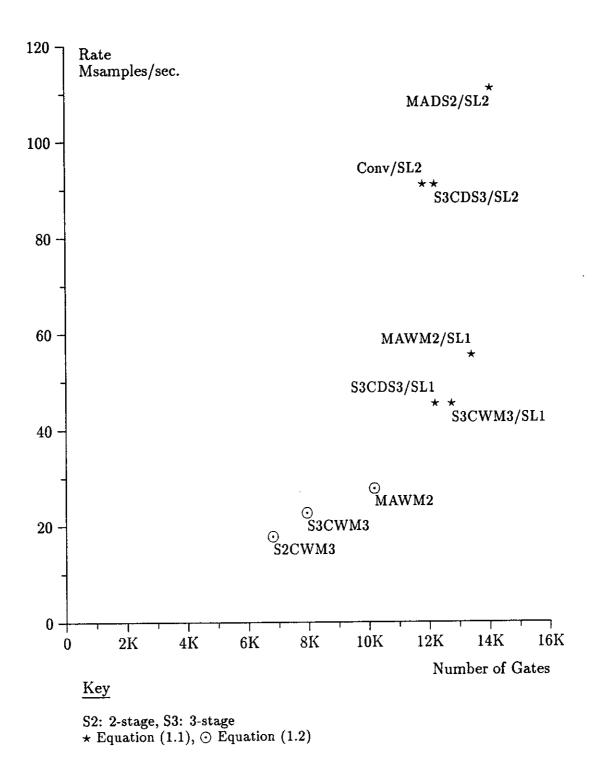

| 9.1         | Comparison of On-line and Conventional Implementations $(d = 8)$                                                                     | 99  |

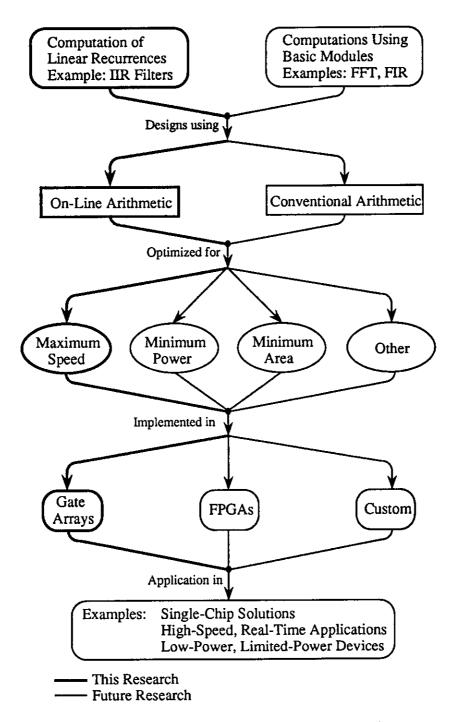

| 10.1        | Suggestions for Future Research                                                                                                      | 108 |

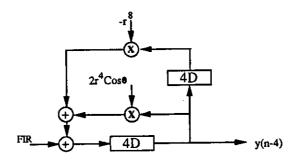

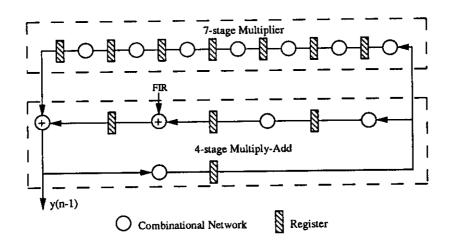

| <b>A.</b> 1 | IIR Computation with 2 Levels of Scattered Lookahead                                                                                 | 115 |

| A.2         | Slice of 4-Stage Multiply-Add (16 bits)                                                                                              | 116 |

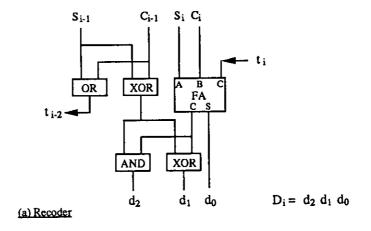

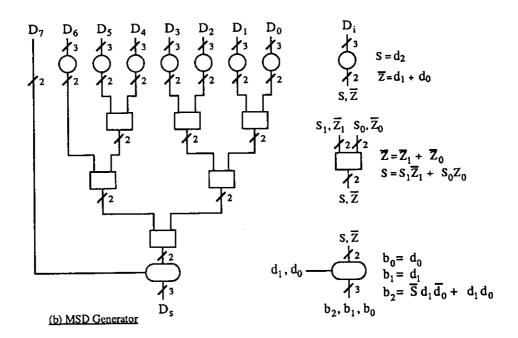

| A.3         | (a)Carry-Save to Radix-4 Recoder (b) MSD Generator                                                                                   | 117 |

| A.4         | Arrays for Reducing Partial Products                                                                                                 | 118 |

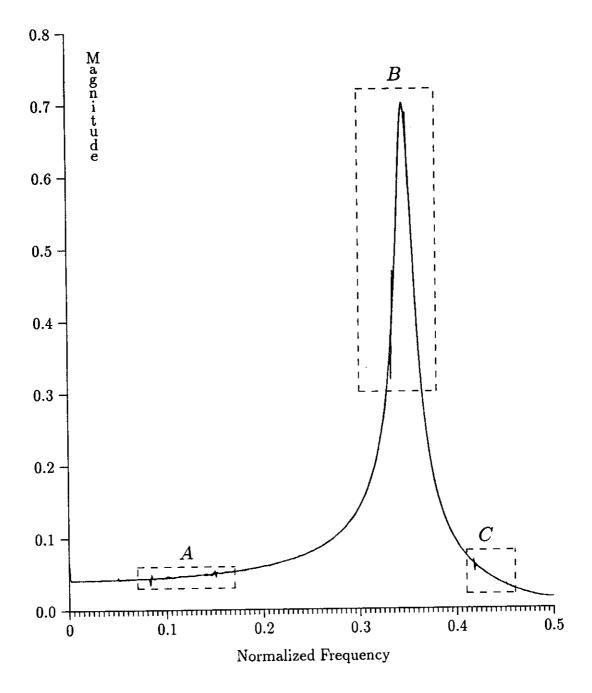

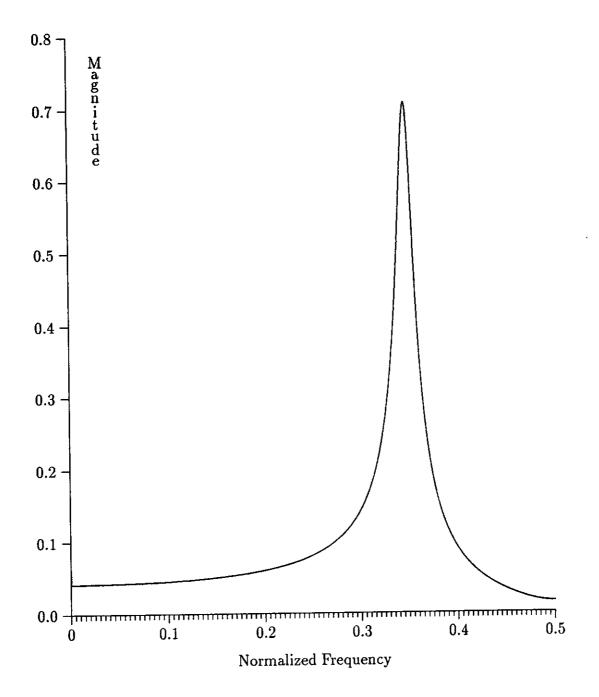

| B.1         | Frequency Response of F1 ( $a = -1.09$ , $b = -0.90$ )                                                                               | 121 |

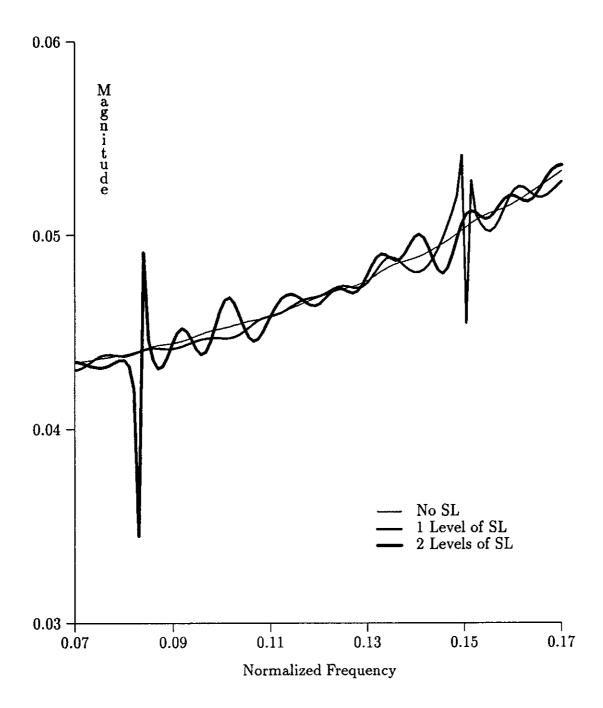

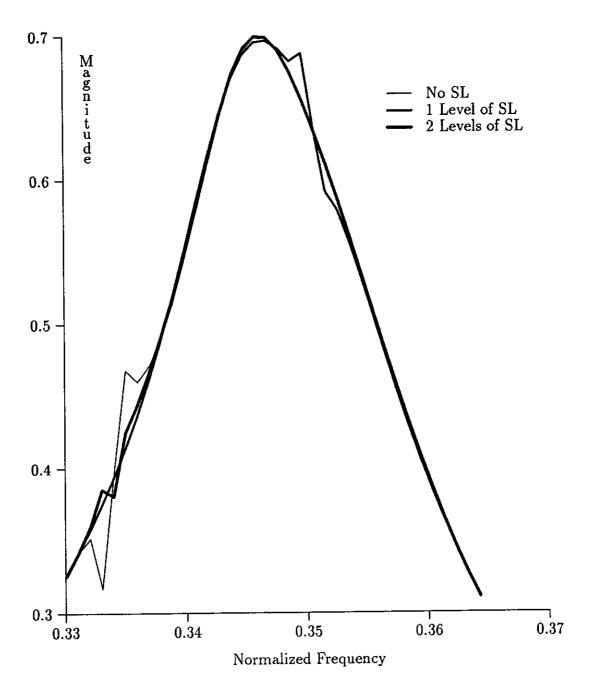

| <b>B.2</b>  | Region A of Frequency Response of F1 $(a = -1.09, b = -0.90)$ .                                                                      | 122 |

| <b>B.3</b>  | Region B of Frequency Response of F1 $(a = -1.09, b = -0.90)$ .                                                                      | 123 |

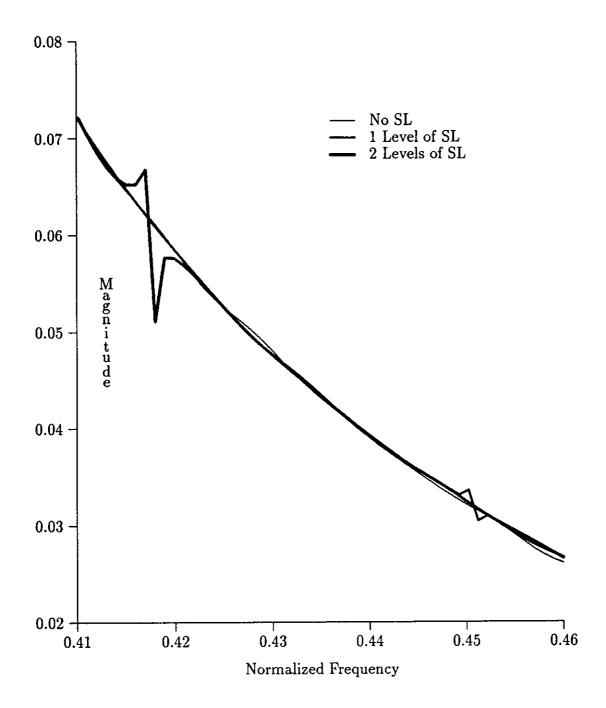

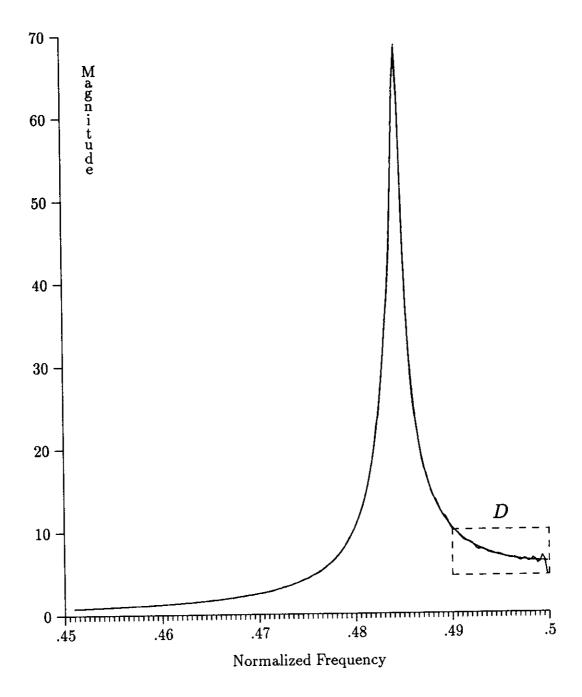

| <b>B.4</b>  | Region C of Frequency Response of F1 $(a = -1.09, b = -0.90)$ .                                                                      | 124 |

| <b>B.5</b>  | Frequency Response of F2 $(a = -1.98, b = -0.99)$                                                                                    | 125 |

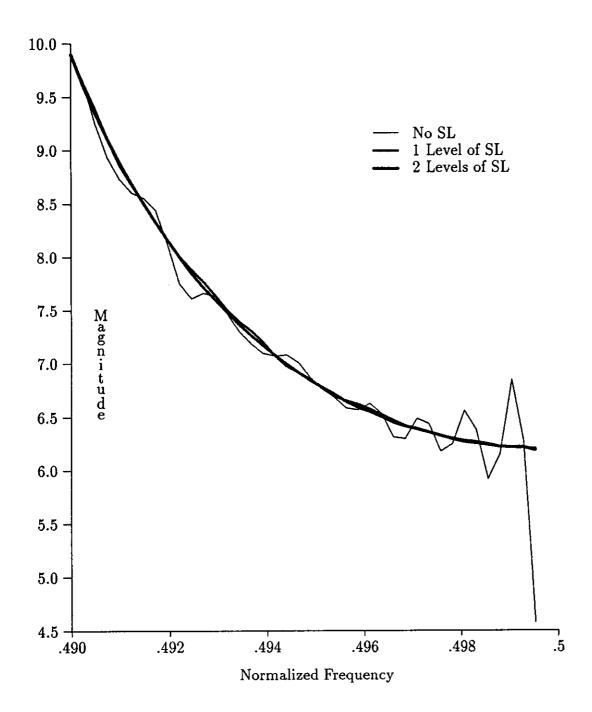

| B.6         | Region D of Frequency Response of F2 $(a = -1.98, b = -0.99)$ .                                                                      | 126 |

| B.7         | Frequency Response of F1 with Dynamic Scaling ( $a = -1.09$ , $b = -0.90$ )                                                          | 127 |

# LIST OF TABLES

| 2.1 | Variation of Multiplier Output Digit $Z_j$                                                   | 18  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | Variation of Combined Multiplier Output $Z_j$                                                | 22  |

| 3.1 | Variation of On-Line Delay                                                                   | 28  |

| 3.2 | Performance/Cost for Composite Word Modules $(d = 8)$                                        | 37  |

| 4.1 | Variation of On-Line Delay for MA Module $(s = 3) \ldots \ldots$                             | 39  |

| 4.2 | Performance/Cost for MA Modules $(d = 8) \dots \dots \dots$                                  | 43  |

| 4.3 | Comparison of Performance/Cost of Word Modules $(d=8)$                                       | 43  |

| 5.1 | Performance/Cost for Array of Composite Digit Stages $(d=8)$                                 | 50  |

| 5.2 | Comparison of Performance/Cost of Arrays $(d = 8) \dots \dots$                               | 52  |

| 6.1 | Latency of Modules for Lookahead Computation                                                 | 60  |

| 6.2 | Coefficient Ranges and Max. Rate for SL and RU                                               | 61  |

| 6.3 | Comparison of Performance/Cost of IIR section with Lookahead $(d=8)$                         | 63  |

| 7.1 | Limit Cycle Amplitudes: Theoretical Bounds and Simulation Results                            | 78  |

| 8.1 | Precision (bits) Required for DS and Precision Extension Schemes                             | 84  |

| 8.2 | Scaling Operations: Advance and Retard                                                       | 86  |

| 8.3 | Performance/Cost for DS Scheme (16-bit)                                                      | 90  |

| 8.4 | DS Scheme vs. Fixed Point Scheme                                                             | 91  |

| 9.1 | Parhi and Hatamian Design                                                                    | 100 |

| 9.2 | Design by McNally et al                                                                      | 02  |

| 9.3 | Comparison of On-Line MA Modules                                                             |     |

| A.1 | Delays and Costs of Components of 4-Stage Multiply-Add                                       | 112 |

| A.2 | Performance/Cost for Conventional IIR Section (16 bits) with 2 levels of Scattered Lookahead | 114 |

| R 1 | Deviation of Frequency Response due to SL                                                    | 120 |

#### LIST OF SYMBOLS

```

a, b, c

coefficients in linear expression

number of bits used to represent coefficients in 2's complement

m

d

number of digits in input and output samples

number of fraction bits used in implementation

i, j, k

iteration or digit indices

sample number

n

N

order of recursion

r

radix (also used for magnitude of a complex number)

sum of maximum magnitudes of coefficients

\boldsymbol{s}

FIR inputs

u, v

w[j]

residual in digit-recurrence algorithm

x, y

sample values of input, output

bounds of Z_i

\overline{z},\underline{z}

R

absolute value of a complex number

R_i

recoder output digit

S, C

sum, carry

X, Y, U

digits of words denoted x, y, u

multiplier output digit

Z_{j}

t_j, s_j

transfer digit, sum digit

delay (ns) of fan-out buffer for digit multiplexers,

t_{buf}

multiplexer delay (ns)

t_{mux}

delay of a full adder (ns)

t_{fa}

delay of a half adder (ns)

t_{ha}

clock period (ns)

t_{clk}

clock-to-output delay for flip-flops (ns)

t_{clkQ}

set-up time for flip-flops (ns)

t_{set}

delay caused by 4-bit CPA

t_{cpa}

\beta

number of fraction bits used for digit selection

δ

on-line delay (clocks)

latency (clocks) between y(n) and y(n-i), y(n) and y(n-j)

\delta_i, \delta_i

on-line delay of an implementation (clocks)

\delta_{imp}

factor by which SL reduces the amplitude bound of

\gamma

zero-input limit cycles

maximum rate of an array (Msamples/sec)

\mu

maximum value of a digit in a redundant number system

\xi, \overline{\xi}

bounds of w[j] - Y_j or w[j] - D_j r^{d-1}

```

#### LIST OF ACRONYMS

CMCombined Multiplier CPA Carry Propagate Adder CSA Carry Save Adder or Carry Save Array DS Digit Stage or Dynamic Scaling FA Full Adder Finite Impulse Response FIR HA Half Adder IIR Infinite Impulse Response Least Significant Digit LSD MA Multiply-Add Most Significant Digit MSD RURecursive Unfolding SM Separate Multiplier SLScattered Lookahead WM Word Module

#### ACKNOWLEDGMENTS

I like to thank the numerous individuals and institutions for their contributions to my education. I owe much to my parents for fostering a love for learning and for the opportunities they provided. I am grateful to the dedicated staff of my high school, St. Joseph's, and also to the University of Sri Lanka for a state-funded undergraduate education. I am also grateful to the University of California, Los Angeles, for the educational opportunities it has provided.

For their encouragement and support I thank my friends and colleagues: Joe Miro-Julia, Paul Tu, Raffi Dionysian, James Liu, Marianne Louie, John Harding, Edwin Tisdale and Dinh Le. Thanks are also due to Prof. Tomas Lang, Verra Morgan, and others too numerous to mention.

I take great pleasure in expressing my gratitude and thanks to my advisor Prof. Miloš Ercegovac for many things. First, for introducing me to computer arithmetic, on-line in particular, and to the dissertation topic. Second, for advice and guidance in research. Third, for having me as a research assistant. Finally, for being available for consultation, often without appointment, during working hours.

I am deeply grateful and thankful to my wife Rasanjali for her patience and encouragement, and for readily assuming much of the burden of supporting us during this endeavor.

This research has been supported in part by NSF grant No. MIP-8813340 Composite Operations Using On-Line Arithmetic for Application-Specific Parallel Architectures: Algorithms, Design and Experimental Studies and by the State of California MICRO Program and Rockwell International.

#### VITA

| 1978 | B.Sc. in Engineering (Honors) University of Sri Lanka, Moratuwa |

|------|-----------------------------------------------------------------|

| 1983 | M.S. in Electrical Engineering<br>University of Texas at Austin |

#### **Publications**

John S. Fernando and Miloš D. Ercegovac, Conventional and On-Line Arithmetic Designs for High-Speed Recursive Digital Filters, VLSI Signal Processing, V, IEEE Press, K. Yao, R. Jain, W. Przytula, J. Rabaey Eds., 1992, pp. 81-90.

John S. Fernando and Miloš D. Ercegovac, On-Line Arithmetic Modules For Recursive Digital Filters, Proc. 26th Annual Asilomar Conference on Signals, Systems and Computers, 1992, pp. 681-685.

#### ABSTRACT OF THE DISSERTATION

# Design Alternatives for Recursive Digital Filters Using On-Line Arithmetic

by

#### John Susantha Fernando

Doctor of Philosophy in Computer Science University of California, Los Angeles, 1993 Professor Miloš Ercegovac, Chair

Design alternatives for fixed-point recursive computations of a second-order direct form filter using on-line arithmetic are analyzed. On-line implementations consume inputs and produce outputs digit serially, beginning with the most significant digit. Digit-level pipelining of on-line filters result in high sampling rates independent of word length. Designs are implemented in a gate array technology to compare performance and costs. Since technology, word length, and function are identical for all designs, the impact of different arithmetic algorithms on performance and cost is easily compared. On-line modules can be used unmodified to implement recursions with scattered lookahead (SL), a transformation that speeds up both on-line and conventional designs. With 2 levels of SL, arrays composed of on-line multiply-add modules implemented in a 0.7-micron gate array, deliver 128Msamples/second. For words exceeding 12 bits, such on-line arrays are faster than a conventional design implemented in an identical gate array. For 16-bit words, on-line arrays are 20% faster. Theoretical bounds derived show that undesirable limit cycle oscillations are reduced in amplitude for most useful filters when SL is applied. The Dynamic Scaling (DS) scheme is proposed to eliminate all undesirable oscillations. Implementation shows that the DS scheme is twice as cost effective as the precision extension method of eliminating oscillations. For single modules with 8-bit I/O words, the DS scheme has a rate 80% higher than the precision extension method and is 13% smaller. The DS scheme requires no modifications of on-line modules.

#### CHAPTER 1

## Introduction

The usual method of speeding up a computation exploits inherent parallelism. Thus, several computational units may be used, and each unit can be pipelined to achieve high clock rates. For a recursive computation of a sequence of values, the rate cannot be increased by simple pipelining, particularly when conventional (right to left evaluation) arithmetic is used. To extract parallelism, and speed up the solution of a general class of linear recurrence equations, a transformation technique called recursive doubling was used by Kogge [Kog73], [Kog81]. The technique transforms a function into two subfunctions of equal complexity, allowing parallel computation of the subfunctions. Successive application of the transform doubles the number of subfunctions. Recursive doubling solutions for second-order linear recurrences were known as early as 1853 to J.J. Sylvester [Kog73]. Two methods of increasing the throughput (rate) of recursive and non-recursive digital filters were proposed by Hayashi et al. [HDSH86]. For a given transfer function, H(z), an N-fold rate increase is obtained by transforming H(z) into component transfer functions. A similar transformation called scattered lookahead (SL) was proposed by Parhi and Messerschmitt to speed-up first-order and second-order transfer functions [PrMs87a], [PrMs87b], [Ms88]. SL allows limited pipelining of the recursive loop in conventional implementations [PrHt88], [HtPr92]. The transformations referred to above achieve speed-up by exposing parallelism at the algorithm level.

Independent of any algorithmic transformations, the rate of recursive computations can be increased at the arithmetic level by using the on-line or most-significant-digit-first (MSDF) method of computation [Erc84], [ErLn88], [ErLn89], or by using the MSDF systolic array approach [KnMc88], [KnMc89], [KnMc90], [KnMc91]. On-line implementations are described in [Bra89a] and [Bra89b].

#### On-line Arithmetic

On-line arithmetic algorithms, proposed by Trivedi and Ercegovac [TrEc77], are a class of digit-serial algorithms that compute the most significant digit first (MSDF). On-line algorithms have been developed for the basic operations like

addition, multiplication, division and square root [ErLn88], [Tu90]. On-line algorithms have also been developed for more complex operations like computing rotation factors, solving classes of linear equations, and singular value decomposition [TuEr91].

Characteristics of on-line algorithms are summarized below.

- Inputs are consumed and outputs are produced, digit by digit, beginning with the most significant.

- The output digits are selected from a redundant digit set. The input digits are usually from the same digit set. This allows the cascading of on-line units.

- The first output digit becomes available only after a few input digits have been consumed. This delay is called the *on-line delay* and is an important characteristic of an on-line algorithm.

- A systematic methodology exists for developing on-line algorithms [ErLn88].

Two essential components of an on-line algorithm are the residual recurrence evaluation and the output digit selection. In each iteration, or step, input digits are consumed, a new residual (an internal state) is computed and an output digit is selected. To enable fast computation, the residual is usually maintained in redundant form (carry-save or signed-digit). Benefits of on-line computation are:

- Digit-level parallelism, which allows the next computation to begin in another module after the on-line delay.

- Low interconnection overhead, because routing between on-line units is on a digit basis.

- Clock rate independent of word length.

- Variable precision operation: at step j, the on-line result produced corresponds to the j most significant digits of the conventional result.

In general, due to digit-level parallelism, on-line algorithms can speed-up computations consisting of a sequence of basic operations. Since recursive computations are an infinite sequence of a few basic operations, the on-line approach is well suited for such computations.

#### 1.1 Problem Statement

The central problem in this dissertation is how to use on-line arithmetic to speed-up computation of a second-order linear recurrence given by (1.1) or (1.2). Considering second-order recurrences is sufficient because higher order filters are implemented by compositions of second-order sections [PrMn88].

$$y(n) = a \cdot y(n-1) + b \cdot y(n-2) + c \cdot x(n)$$

(1.1)

OF

$$y(n) = a \cdot y(n-1) + b \cdot y(n-2) + u(n)$$

(1.2)

The term u(n), also called the finite impulse response (FIR) term, is a non-recursive linear function of x(n), x(n-1), and x(n-2). These expressions correspond to direct form filter structures. The direct form filter structures have been shown to be best suited for high sampling rates [Sam88]. Unfortunately, the direct form filter suffers from undesirable non-linear oscillations. The oscillations must be eliminated without compromising much of the sampling rate and with minimum added cost.

# 1.2 Research Objectives

The few designs and implementations described in recent publications cannot be compared because of differences in technology, word length, coefficient magnitude, order of output function, and features like testability. Key questions remain:

- 1. Given a performance level or cost constraint, what is the most appropriate architecture for implementing a second-order direct form recursive digital filter?

- 2. At what word length does on-line arithmetic payoff, compared to conventional?

- 3. How does the scattered lookahead transformation, used to increase sampling rate, affect non-linear oscillations?

- 4. How can non-linear oscillations be eliminated from on-line implementations?

Currently, the only method of eliminating non-linear oscillations in on-line modules is to extend working precision [Bra89b]. The method does not reduce the clock rate, but requires a costly increase of working precision. A more cost-effective solution is developed in Chapter 8.

#### 1.3 Dissertation Outline

The emphasis in this dissertation is on the recursive part of the computation, since the FIR part of the computation is easily performed at the desired rate. Simple schemes based on on-line multipliers, on-line adders, and on-line recoders, are analyzed in Chapter 2. These schemes are easy to develop but have excessive on-line delay. On-line composite modules [ErLn88], which perform the computation as a whole, are developed in Chapter 3. An expression for the on-line delay is derived for a N-order linear recurrence. Algorithms with small on-line delay are implemented. Composite modules are more cost-effective and faster than the simple schemes. On-line multiply-add (MA) modules, which can be cascaded to realize (1.1) or (1.2), are developed in Chapter 4. MA modules are faster than composite modules. Chapter 5 describes two types of multi-module maximum rate arrays based on composite and MA modules. The rate of the array depends on the clock rate of the basic module, and the size of the array depends mainly on the word length.

Composite modules and MA modules with different digit sets and different levels of pipelining are implemented in a LCA10000<sup>1</sup> Series Compacted Array<sup>2</sup> [LSI87]. Schematic capture and simulation of designs was done using Workview<sup>3</sup> CAD tools. Performance is measured by the fastest clock rates achievable in simulation. The number of equivalent gates is used as a cost measure. Each gate is considered to be equivalent to two n-channel and two p-channel transistors. Arithmetic models and netlists of the on-line implementations are used for functional simulation to verify results.

Chapter 6 discusses algorithmic transformations, sometimes called lookahead schemes, that produce higher sampling rates. Applied to (1.1) or (1.2), such transformations produce equivalent linear recurrences of higher order. Scattered lookahead (SL) is one such transformation proposed to speed-up conventional implementations [PrMs87a], [PrHt88]. Arrays of on-line modules using SL are designed. A new conventional design with two levels of SL, described in appendix

<sup>&</sup>lt;sup>1</sup>LCA10000 is a gate array using a 1.5-Micron HCMOS technology.

<sup>&</sup>lt;sup>2</sup>Compacted Array is a trademark of LSI Logic Corporation.

<sup>&</sup>lt;sup>3</sup>Workview is a trademark of VIEW logic Systems Inc..

A, is implemented to find the word length at which on-line implementations outperform the conventional. The effect of SL on the frequency response of two filters is shown in appendix B.

Chapters 7 and 8 investigate non-linear oscillations. Overflow oscillations are caused by limited precision, and zero-input limit-cycle oscillations are caused by roundoff errors [Sam88]. Absolute value bounds for the magnitude of zero-input limit cycle oscillations, similar to [LnTr73], are derived for the SL transformation in Chapter 7. It is shown that SL reduces the bound for the most useful filters. Chapter 8 describes the proposed dynamic scaling scheme which eliminates oscillations in filters composed of on-line modules. Implementation shows that it is twice as cost effective as the precision extension scheme. Chapter 9 compares the designs developed here with others. The dissertation concludes with Chapter 10 which discusses the applicability of the results to other technologies and directions for further research.

#### 1.4 Related Work

Recent publications have shown that digit-serial computation, using the most significant digit first (MSDF), can produce high sampling rates for recursive digital filters. The MSDF approach reduces the recursive bottleneck form the word level to the digit level. Lookahead transformations can be used for doubling or quadrupling sampling rates. The related work is outlined below.

- 1. In an overview of on-line arithmetic, Ercegovac describes an on-line algorithm computing y = ax + b for solving an *m*th order linear recurrence system [Erc84].

- 2. Ercegovac and Lang describe MSDF and on-line approaches for the design of recursive digital filters [ErLn89].

- 3. Knowles et al. use a MSDF approach for digital filtering, implementing a systolic array for a first-order and second-order recursions [KnMc88], [KnMc89], [KnMc90], [KnMc91].

- 4. Parhi and Hatamian describe a high speed conventional implementation which uses two levels of scattered lookahead [PrHt88], [HtPr92].

- 5. Brackert et al. design and implement an on-line multiply-add (MA) module and a direct form II filter composed of MA modules [Bra89a]. This is the first application of on-line arithmetic to implement high speed filters.

- 6. Cha describes in detail a CMOS chip implementing a direct form II second-order structure using four on-line MAs with programmable coefficients [Cha91]. The implementation uses the MA design described in [Bra89a].

- 7. McCanny et al. describe a 40MHz IIR filter chip for second-order recursions using a MSDF systolic array architecture with one level of SL [KnMc91]. The architecture is similar to that proposed by Knowles et al. [KnMc88].

Recent implementations of recursive filters fall into three categories: on-line, MSDF systolic arrays, and conventional. On-line designs are described in [Bra89a], [Bra89b], [Cha91], and [FnEr92b]. The MSDF systolic arrays are described in [KnMc88], [KnMc90], [KnMc91] and [LFH90]. Conventional implementations are described in [PrHt88], [HtPr92], and [FnEr92a]. Chapter 9 evaluates some of these implementations in more detail.

#### 1.5 Contributions

Answers to the questions posed in Section 1.2 have been obtained. The main contributions are:

- 1. Design and implementation of composite on-line modules. Composite on-line modules compute the recursion expressed by (1.1) or (1.2) as a whole. Composite modules have not been designed and implemented before.

- Design and implementation of a MA module (much faster than [Bra89a]).

MA modules are used to implement the recursion as a series of multiply-adds.

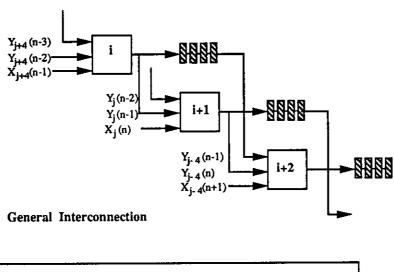

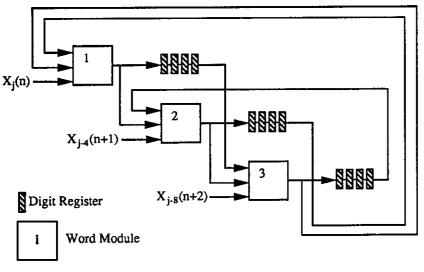

- 3. Development of word module arrays and digit stage arrays based on composite modules and MA modules.

- 4. New conventional design to implement (1.2) with two levels of scattered lookahead. The design uses a carry-free recursive loop to speed-up computation. It is suited for multiplication of words of about 16 bits or more, depending on the technology. Comparison shows that for precisions of more than 12 bits, the on-line designs are faster.

- 5. Derivation of new absolute bounds for zero-input limit cycles for the scattered lookahead case. For second-order recursions with distinct complex roots, SL reduces the amplitude bound of zero-input limit cycle oscillations

- for most recursions. The recursions for which the amplitude is reduced by SL are those most used in practice. The bounds are verified by simulation.

- 6. The dynamic scaling (DS) scheme for on-line designs is proposed and implemented. The DS scheme eliminates overflow oscillations and zero-input limit cycle oscillations at half the cost of the precision extension method proposed by Brackert [Bra89b]. Moreover, the DS scheme requires no modification of on-line modules used in the computation.

The contributions can be summarized as follows. Given word length and other constraints, this research shows how to determine the appropriate design: i.e., conventional or on-line, type of on-line module or array, whether to use DS. In addition, theoretical bounds are derived for the absolute bound on limit cycles for second-order sections with SL.

#### CHAPTER 2

# Schemes Based on Multipliers, Recoders and Adders

This chapter describes two simple schemes for realizing Equation (1.1) using a most-significant-digit-first (MSDF) multiplication algorithm described in [Erc87]. This algorithm produces the product in a 2's complement form without using a carry propagate adder and without extra delay. Analysis of these simple schemes provides the insight and the motivation for faster designs described in later chapters.

The first section of this chapter describes the multiplication algorithm, the basis for all modules described in this dissertation. Section 2.2 develops a recurrence-based recoder to convert the over-redundant digit produced by the multiplication. The Separate Mutiplier (SM) scheme and the Combined Multiplier (CM) scheme are described in Sections 2.3 and 2.4. Performance (sampling rate) estimates for each scheme show how performance is influenced by the design, the range of coefficients and the choice of radix and digit sets.

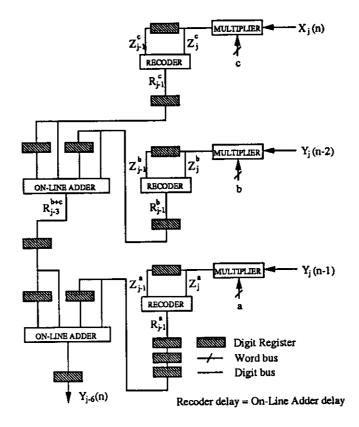

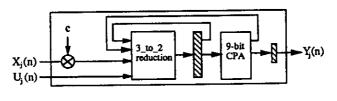

The SM scheme, described in Section 2.3, is the most intuitive implementation of (1.1). The scheme uses three separate MSDF sequential multipliers and two on-line adders as shown in Figure 2.1. This scheme is a result of directly mapping simple arithmetic operations to units which execute these operations in a MSDF manner. The recoders shown in Figure 2.1 convert the output of the multipliers into a digit-set acceptable to the adders. The choice of this scheme as the starting point of the analysis is also justified by the following. First, the use of dedicated units for multiplication, recoding and adding contributes to efficient and fast designs for each unit. Second, having chosen the scheme, a delay analysis reveals the modifications necessary for improved designs.

The CM scheme, described in Section 2.4, combines the three multipliers and computes in fewer clocks than the SM scheme. The combining of the three multiplications into one carry-save adder array eliminates the delays caused by the addition required when the multipliers are separate. The combining also lowers the hardware required for the CM scheme. However, the larger carry-save adder array reduces the clock rate of the CM scheme.

Figure 2.1: Scheme Using On-Line Units

# 2.1 MSDF Multiplication Algorithm

The selected multiplier uses a MSDF residual recurrence algorithm described in [Erc87]. All multiplications in (1.1) have a constant coefficient as the multiplicand. The multiplier is in an on-line form. The essential features of the multiplication algorithm are summarized below.

- The residual recurrence uses the digits of the multiplier from left to right, producing the most significant digit of the result first. This is well suited to the filter application, because the computation of y(n+1) may begin in another module as soon as the most significant digit of y(n) is produced.

- The partial product is maintained as a signed-digit integer part and a carry-save fraction part. The carry-save form enables a fast recurrence step because carry propagation is avoided in the recurrence loop. However, each iteration produces an over-redundant signed-digit as the output of the multiplier.

- It is assumed, without loss of generality, that the *mutiplicand* is represented in two's complement, and that the *multiplier* is represented in a radix-4 signed-digit system with the digit set  $\{-\rho, \ldots, \rho\}$  where  $\rho \in \{2, 3\}$ . The algorithm is easily modified for a different radix and digit set. Changing the radix or the digit set produces implementations with different performance and cost.

- The mutiplicands in all three multipliers are constant coefficients, a, b, c, as defined in (1.1). This allows multiples of the coefficients to be precomputed, permitting the use of digit sets with  $\rho > 2$ . Stability of the second-order filter requires |a| < 2 and |b| < 1 [PrMn88].

#### Residual Recurrence for Multiplication

Consider the multiplication  $x \cdot y$ , where the multiplicand x is represented in 2's complement and the multiplier y is represented in radix-4 signed-digit form (x and y are used here in a generic sense and do not refer to Equation (1.1)). The values x and y can be expressed as follows.

$$x = -2X_{-1} + \sum_{i=0}^{m-2} X_i 2^{-i}, \quad X_i \in \{0,1\}, \quad |x| < 2$$

(2.1)

$$y = \sum_{i=0}^{d-1} Y_i 4^{-i}, \quad Y_i \in \{-\rho, \dots, \rho\}, \quad |y| < 1$$

(2.2)

The multiplication algorithm uses a recurrence which produces the sequence of over-redundant signed-digits  $Z_j$  and partial products w[j] specified by:

$$w[0] = 0 (2.3)$$

$$w[j+1] = 4fraction(w[j] + xY_j), j = 0,...,d-1$$

(2.4)

$$Z_j = integer(w[j] + xY_j) (2.5)$$

A fast implemention of this recurrence maintains the partial product w[j] in carry-save form, as shown below. The carry-save form allows the use of a carry-save adder which eliminates carry propagation in the recurrence loop.

$$w[j] = S[j] + C[j] \tag{2.6}$$

$$w[j] \geq 0 \tag{2.7}$$

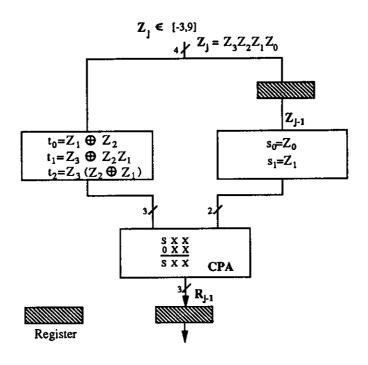

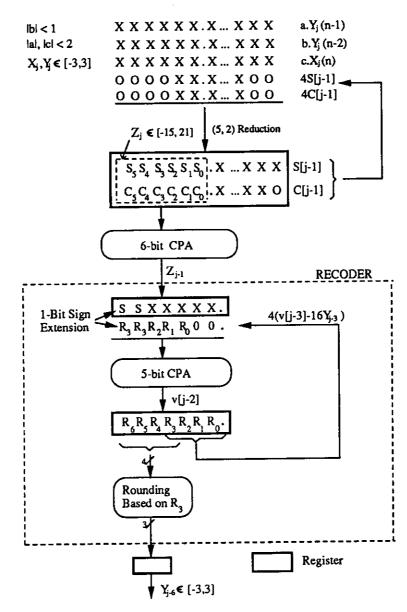

Figure 2.2 shows the residual recurrence step, and Figure 2.3 shows how  $Z_j \in \{-4, ..., 10\}$  is computed by a small CPA for r = 4 and  $\rho = 2$ . The range of  $Z_j$  for different radices, digit sets and coefficient bounds are discussed later (Table 2.1).

Figure 2.2: Recurrence for Multiplication

Figure 2.3: Multiplier Output  $(Z_i)$  Computation

## Implementation Schemes for Multiplication

The critical path of the second-order filter shown in Figure 2.1 consists of a multiplier, a recoder, and an on-line adder. Except for the multiplier, all other units can be pipelined further. Speed of multiplication is limited by the the residual recurrence loop which cannot be pipelined. Therefore, the first stage of the filter is the slowest stage. The radix and the digit-set chosen for the multiplier influence cost and performance of the filter.

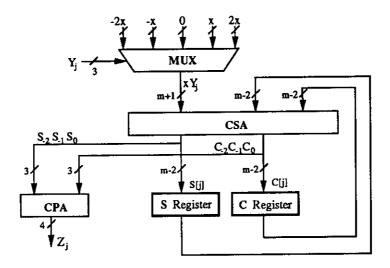

The three multiplication schemes shown in Figure 2.4 illustrate the cost and performance trade-offs. Scheme M1 has the minimum clock period because the CPA for producing  $Z_j$  is included in the second stage. Scheme M2 has one stage and the slowest clock period. Scheme M3 is a compromise where the CPA for producing  $Z_j$  is pipelined into two stages with balanced delays. Scheme M3 is useful only if the CPA delay is larger than the delay for the residual recurrence. The delays  $t1_{mul}$  and  $t2_{mul}$ , for the first stage of schemes M1 and M2, are:

$$t1_{mul} = t_{buf} + t_{mux} + t_{fa} + t_{clkQ} + t_{set}$$

$$t2_{mul} = t_{buf} + t_{mux} + t_{fa} + t_{cpa} + t_{clkQ} + t_{set}$$

where

$t_{buf}$  Delay of fan-out buffer for the digit multiplexers,

$t_{mux}$  Multiplexer delay,

$t_{fa}$  Delay caused by a full adder,

$t_{clkQ}$  Clock-to-output delay for flip-flops,

$t_{set}$  Set-up time for flip-flops.

$t_{cpa}$  Delay caused by 4-bit CPA;  $t_{cpa} = t_{mux} + t_{fa} + t_{ha}$

The speed of the multiplier decreases with the size of the digit set, since larger multiplexers have larger values of  $t_{mux}$ . For small radices, 2 or 4, the change in  $t_{mux}$  caused by the digit set is small and depends on the technology. For example, in LCA10000 technology, the delays for the first five components listed above are (in same order), 1.5ns, 2.5ns, 2.3ns, 1.7ns and 0.8ns [LSI87]. If the 5-to-1 multiplexer is replaced by a 3-to-1 multiplexer, required for a radix-2 scheme, the multiplexer delay drops from 2.5ns to 1.3ns. This represents a speedup of 13.6% with respect to the radix-4 scheme. Note that delays associated with wire lengths were not included, since such delays depend on the layout. If wire length delays are included, the difference between radix-4 and radix-2 speeds may be smaller.

# 2.2 Recoder Design

For a computation that produces an over-redundant result, a recoder is required to represent the result in an acceptable digit set. The multiplication algorithm described previously and the addition of signed-digits are examples of such computations. Recoding can be performed in two ways:

1. A series of successive recodings, producing intermediate digit sets that become smaller. Each recoder reduces the digit set by a relatively small amount. An example of such a recoder is shown in Figure 2.5. The recoding table shows the transfer digits  $t_j$  and the sum digits  $s_j$  for possible values of the input digit. The residual in this implicit recurrence is  $s_j$ .

Figure 2.4: Multiplier Implementation Schemes

2. An explicit recurrence that produces output digits in the desired range without intermediate digits.

The design of a recoder using an explicit recurrence is described next. The recoder is specified by:

- The radix r.

- The range of the over-redundant input integer  $Z_j$  (2's complement),  $\underline{z} \leq Z_j \leq \overline{z}$ .

- The digit set,  $\{-\rho, \ldots, \rho\}$ , of the output digit  $Y_j$ .

• The minimum precision, N, in digits, required for the recurrence. Consequently, the recoding delay is N-1 clocks. The value of N depends on the other specifications.

The recurrence for the recoder is given by

$$v[j+1] = r(v[j] - Y_i r^{N-1}) + Z_i, \quad v[0] = 0, \quad j = 0, 1, 2, \dots$$

(2.8)

All values in the recurrence are integers. A recoder for r=4 and N=3 is shown as part of a module in Figure 2.9. It illustrates the recurrence step and the selection of the output digit,  $Y_j$ , based on the residual v[j]. In the  $j^{th}$  iteration, the over-redundant value  $Z_j$  is added to  $v[j] - Y_j r^{N-1}$  to form v[j+1].

An expression for the delay is obtained by considering the bounds on the shifted residual. Let the range of the shifted residual be defined by:  $\underline{\xi} \leq v[j] - Y_j r^{N-1} \leq \overline{\xi}$ . Since v[j+1] must be contained in N digits for all values of residuals and all values  $Z_j$ , consider the case of the maximum residual and maximum  $Z_j$ . This is expressed by (2.9). Similarly, expression (2.10) considers the case of the minimum residual and minimum  $Z_j$ .

$$\overline{z} + r\overline{\xi} \leq \rho r^{N-1} + \overline{\xi} \tag{2.9}$$

$$\underline{z} + r\underline{\xi} \geq -\rho r^{N-1} + \underline{\xi} \tag{2.10}$$

Now consider the selection function to obtain expressions for  $\overline{\xi}$  and  $\underline{\xi}$ . For a rounding selection function  $\overline{\xi}$  and  $\underline{\xi}$  are given by (2.11) and (2.12). A rounding selection function selects an output digit by rounding the residual to the nearest integer.

$$\overline{\xi} = \frac{1}{2}r^{N-1} - 1 \tag{2.11}$$

$$\underline{\xi} = -\frac{1}{2}r^{N-1} \tag{2.12}$$

Two values of N are obtained: Equations (2.9) and (2.11) give one, and Equations (2.10) and (2.12) give the other. The larger value of N satisfies both bounds and is expressed by:

$$N = 1 + \left[ \log_r \frac{2 \max(\overline{z} + 1 - r, -\underline{z})}{2\rho + 1 - r} \right]$$

(2.13)

The recoding delay, N-1, is defined as the number of clocks between a input digit and the output digit of *identical weight*. Given the radix, the input digit range, and the output digit set, the precision of the residual can be calculated to complete the design of the recoder.

#### 2.3 Separate Multiplier (SM) Scheme

Figure 2.1 shows, the SM scheme to evaluate (1.1). The multiplier was discussed in Section 2.1. This section describes the recoder, the signed-digit adder and the performance of the scheme. Performance is measured by the sampling rate, given by the clock period times the number of clocks required for the critical loop. The critical loop consists of the multiplication  $a \cdot y(n-1)$ , the recoding of the output of the multiplication and the addition of  $R_j^{b+c}$ . The clock period is determined by the multiplier (Section 2.1). The number of clocks is determined primarily by the recoder and signed-digit adder. Given a digit set, the magnitude of the range of  $Z_j$  affects delays of the recoder and the adder, as described next.

#### Recoding Multiplier Output $Z_j$

The recoder converts the over-redundant integer  $Z_j$  into a smaller digit set acceptable to the input of the adder. The recoder described here uses a recoding table.

Figure 2.5 shows the recoding table for [-3,9] to [-3,3]. The table is implemented by a simple combinational network specified in Figure 2.5. Each digit,  $Z_j$ , input to the recoder, is converted to a transfer digit  $t_{j-1}$  and a sum digit  $s_j$ . The recoded digit  $R_{j-1}$  is produced by adding the current transfer digit  $t_{j-1}$  to the previous sum digit  $s_{j-1}$ .

The transfer digit  $t_{j-1}$  depends only on the value of  $Z_j$ . Thus, the on-line delay for recoding, called the recoding delay, is one clock. Since the recoded value must be registered after recoding (Figure 2.5), the total delay caused by inserting the recoder is two clocks.

As Table 2.1 shows, for a coefficient |x| < 1, the digit set [-3,3] has the minimum recoding delay. For |x| < 2, radices 4 and 8 cause less recoding delay than radix-2. The choice of radix-4 results in faster recoding, since radix-8 takes a longer clock period. Figure 2.6 shows the scheme for recoding from a digit set of [-9,9] to a digit set of [-3,3]. The recoding delay is three clocks. The signed-digit adder is considered next.

#### Signed-Digit Adder

Figure 2.7 shows two schemes for adding the recoded digits. The recoder outputs  $R_j^a$ ,  $R_j^b$ , and  $R_j^c$ , are added and recoded again to produce  $Y_j$  in the appropriate digit set. The choice of radix-4 leads to fewer clocks for the addition. Equation

| $Z_{j}$                              | -3 | -2 | -1 | 0 | 1 | 2  | 3  | 4 | 5 | 6  | 7  | 8 | 9  |

|--------------------------------------|----|----|----|---|---|----|----|---|---|----|----|---|----|

| t <sub>i-1</sub>                     | -1 | 0  | 0  | 0 | 0 | 1  | 1  | 1 | 1 | 2  | 2  | 2 | 21 |

| $\left  \mathbf{s}_{j}^{-1} \right $ | 1  | -2 | -1 | 0 | 1 | -2 | -1 | 0 | 1 | -2 | -1 | 0 | 1  |

Figure 2.5: Recoder for [-3,9] to [-3,3]

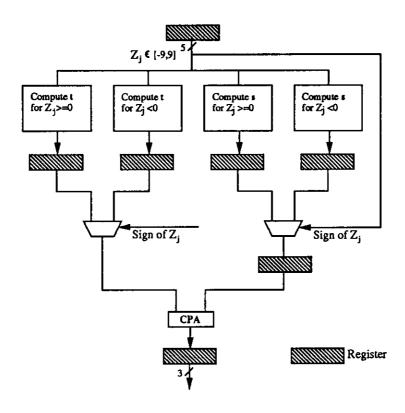

(2.13) indicates that a digit set of [-2,2] incurs a larger recoding delay in the adder than a digit set of [-3,3]. Thus a digit set of [-3,3] is chosen to reduce the delay for the entire module.

Scheme A1, shown in Figure 2.7, uses two adders, each adding two digits. For a digit set of [-3,3] both adders are identical, producing a digit in range [-3,3] (i.e., recoding from [-6,6] to [-3,3]) with a recoding delay of 1 clock. The total delay is four clocks as shown in Figure 2.7.

|                       | $Z_{j}$                            | -9       | -8      | -7      | -6       | -5       | -4      | -3      | -2      | -1      | 0      | 1      | 2       | 3       | 4      | 5      | 6       | 7       | 8      | 9      |

|-----------------------|------------------------------------|----------|---------|---------|----------|----------|---------|---------|---------|---------|--------|--------|---------|---------|--------|--------|---------|---------|--------|--------|

| $Z_{j+1} \geqslant 0$ | t <sub>j-1</sub><br>Sj             | -2<br>-1 | -2<br>0 | -2<br>1 | -1<br>-2 | -1<br>-1 | -1<br>0 | -1<br>1 | 0<br>-2 | 0<br>-1 | 0<br>0 | 0<br>1 | 1<br>-2 | 1<br>-1 | 1<br>0 | 1<br>1 | 2<br>-2 | 2<br>-1 | 2<br>0 | 2<br>1 |

| Z <sub>j+1</sub> <0   | t <sub>j-1</sub><br>S <sub>j</sub> | -2<br>-1 | -2<br>0 | -2<br>1 | -2<br>2  | -1<br>-1 | -1<br>0 | -1<br>1 | -1<br>2 | 0<br>-1 | 0      | 0      | 0<br>2  | 1<br>-1 | 1<br>0 | 1      | 1<br>2  | 2<br>-1 | 2      | 2      |

Figure 2.6: Recoder for [-9,9] to [-3,3]

Table 2.1: Variation of Multiplier Output Digit  $Z_j$

| $Z_j$    | Radix | Digit Set | Coefficient | Recoding Delay |

|----------|-------|-----------|-------------|----------------|

| [-1, 3]  | 2     | [-1, 1]   | <1          | 2              |

| [-2, 4]  | 2     | [-1, 1]   | <2          | 3              |

| [-2, 8]  | 4     | [-2,2]    | <1          | 2              |

| [-4, 10] | 4     | [-2, 2]   | <2          | 2              |

| [-3, 9]  | 4     | [-3, 3]   | <1          | 1              |

| [-6, 12] | 4     | [-3, 3]   | <2          | 2              |

| [-4, 18] | 8     | [-4, 4]   | <1          | 2              |

| [-8, 22] | 8     | [-4,4]    | <2          | 2              |

Scheme A2 adds all three digits in one stage, then recodes in the second and third stages. Scheme A2 requires a larger clock period due to the larger adder. Figure 2.6 shows the table for recoding from a digit set of [-9,9] to a digit set of [-3,3].

#### Performance

Figure 2.8 shows the block diagram of the radix-4 filter with digits in the set [-3,3] and coefficients with absolute value less than 2. The total delay is 9 clocks.

The estimated clock period for an implementation in a LCA10000 Array [LSI87] is 10ns. The maximum rate for this computation is determined by the delay of the critical loop. The critical loop consists of the path from the input y(n-1) to the output y(n). The critical loop delay is 7 clocks, for coefficients with magnitude < 2, because the two registers before the final adder can be eliminated. Thus, the estimated maximum rate is 14.3 Msamples/sec. The relatively low performance of this design is caused by excessive recoding delays. The next section describes a scheme which reduces the recoding delay.

Figure 2.7: Signed-Digit Adder Implementation Schemes

Figure 2.8: Separate Multiplier (SM) Scheme ( $\delta_{imp} = 7$ )

# 2.4 Combined Multiplier (CM) Scheme

The implementation outlined in Figure 2.8 shows that the on-line addition of the three signed digits  $R_j^a$ ,  $R_j^b$  and  $R_j^c$ , takes 4 clocks. This section describes an implementation which performs the multiplication and addition in one carry-save adder array. The scheme has a delay of 6 clocks and requires fewer registers than the SM scheme. The combined multiply-add recurrence is derived by combining the three separate multiplication recurrences. The over-redundant digit produced by the multiply-add is recoded to obtain the output digit.

### The Combined Multiply-Add Recurrence

The scheme shown in Figure 2.8 has three separate multipliers based on the recurrence defined by Equations (2.3) through (2.5). The three multiplication recurrences are given below.

$$w^{a}[0] = 0$$

$w^{a}[j+1] = 4fraction(w^{a}[j] + aY_{j}(n-1)), j = 0,...,d-1$

$Z^{a}_{j} = integer(w^{a}[j] + aY_{j}(n-1))$

$w^{b}[0] = 0$

$w^{b}[j+1] = 4fraction(w^{b}[j] + bY_{j}(n-2)), j = 0,...,d-1$

$Z^{b}_{j} = integer(w^{b}[j] + bY_{j}(n-2))$

$$w^{c}[0] = 0$$

$w^{c}[j+1] = 4fraction(w^{c}[j] + cX_{j}(n)), j = 0,...,d-1$

$Z_{j}^{c} = integer(w^{c}[j] + cX_{j}(n))$

The three recurrences shown above are combined to produce a single recurrence:

$$w[0] = 0 (2.14)$$

$$w[j+1] = 4fraction(w[j] + aY_j(n-1) + bY_j(n-2) + cX_j(n)), \quad j = 0, ..., d-1$$

(2.15)

$$Z_{j} = integer(w[j] + aY_{j}(n-1)) + bY_{j}(n-2) + cX_{j}(n))$$

$$(2.16)$$

This recurrence is implemented by maintaining the partial product w[j] in carry-save form, shown below, to allow the use of a carry-save adder.

$$w[j] = S[j] + C[j] (2.17)$$

$$w[j] \geq 0 \tag{2.18}$$

Figure 2.9 shows the combined multiplier and the recoder. The range of the output digit of the combined multiplier,  $Z_j$ , is greater than for the case where the multipliers were separate. Table 2.2 shows the range of values of  $Z_j$ , and the resulting recoding delays, for different ranges of coefficients. The coefficients' ranges are expressed by s, defined as the sum of the maximum magnitudes of the coefficients. For example, s = 4 for |a| < 2, |b| < 1 and |c| < 1, and s = 5 for |a| < 2, |b| < 1 and |c| < 2. The delay of the recoder is obtained from expression (2.13). Table 2.2 shows that the minimum recoding delay is obtained for radix-4 with digit set [-3,3].

Table 2.2: Variation of Combined Multiplier Output  $Z_j$

| Radix | Digit Set | s | $Z_{j}$  | Recoding Delay |

|-------|-----------|---|----------|----------------|

| 2     | [-1,1]    | 4 | [-4,6]   | 4              |

| 2     | [-1,1]    | 5 | [-5,7]   | 4              |

| 4     | [-2,2]    | 4 | [-8,14]  | 3              |

| 4     | [-2,2]    | 5 | [-10,16] | 3              |

| 4     | [-3,3]    | 4 | [-12,18] | 2              |

| 4     | [-3,3]    | 5 | [-15,21] | 2              |

#### Performance

The total delay is 6 clocks for s=4 and s=5. The clock period is determined by the first stage. For a LCA10000 Array [LSI87] the first stage takes 14ns. The CM scheme shown in Figure 2.9 may be pipelined at the first stage, i.e., the multiples  $c \cdot X_j(n)$  and  $b \cdot Y_j(n-2)$  are generated in the first stage. The second stage generates  $a \cdot Y_j(n-1)$  and reduces 5 rows to 2. The clock period is reduced

to 11ns and the maximum rate remains at 1 sample every 6 clocks, a sampling rate of 15Msamples/second.

The maximum rate of the CM scheme is about the same as that of the SM scheme. However, the CM scheme has a lower cost due to the fewer registers required for sum and carry.

Figure 2.9: Combined Multiplier Scheme ( $\delta_{imp} = 6$ )

## CHAPTER 3

# A Composite On-Line Scheme

The schemes analyzed in Chapter 2 were composed of separate on-line units. The CM scheme described in Section 2.4 is an example. The scheme has long on-line delays caused by recoding stages. This chapter begins with a development of a composite on-line scheme based on a digit recurrence, similar to [Bra89a]. The entire computation expressed by (1.1) is carried out as a single operation in the composite on-line scheme.

An expression for the on-line delay of the composite scheme is derived for a N-order linear recurrence in Section 3.1. Section 3.3 describes how the parameters and architecture for a fast implementation of a second-order recurrence are selected. Performance and cost comparisons for four second-order radix-4 implementations are presented in Section 3.4.

# 3.1 Specification and Derivation of Recurrence

The notation used to specify a linear recurrence is introduced first. Expressions for input and output are derived in terms of the input digits, the on-line delay and the output digits. These expressions are used in the derivation of the digit recurrence. The notation adopted is as follows.

- Output expression for a linear N-order recurrence is given by  $y(n) = cx(n) + a_1y(n-1) + a_2y(n-2) + \ldots + a_Ny(n-N)$

- Radix, r.

- Digit set  $\{-\rho, \ldots, \rho\}$ , for input,  $X_j$ , and output,  $Y_j$ .

- Number of radix-r digits per word, d.

- On-line delay for the recurrence,  $\delta$ .

- Sum of the maximum absolute values of coefficients  $a_i$  and c denoted by s.

Definition 1 ( $\delta$ ) The on-line delay,  $\delta$ , of a digit recurrence algorithm is the delay measured in recurrence steps (or clocks), between an input digit and the output digit of identical weight.

**Definition 2** (s) The sum of the bounds of the magnitude of coefficients in a digit recurrence is defined as:

$$s = \sum_{i=1}^{N} A_i + C, |a_i| < A_i, |c| < C$$

(3.1)

The bounds on coefficient magnitudes are defined by stability criteria for recursive filters [PrMn88]. For a stable linear time-invariant system, the output, y(n), must be bounded for every bounded input x(n). Without loss of generality, x(n) is assumed to be < 1. The stability of (1.1) and (3.1) is assured for coefficients inside the triangle shown in Figure 7.1. For a composite module implementing (1.1), with |a| < 2 and |b| < 1 for stability, s = C + 3. To derive a digit recurrence for the composite on-line scheme, the ouput and input values must be expressed in terms of their digits and the on-line delay. Consider first the output of the on-line computation. The output contains  $\delta$  leading zeros. Expressed as a full-precision scaled result, the output is given by:

$$y(n) = r^{-\delta}(cx(n) + \sum_{k=1}^{N} a_k y(n-k))$$

(3.2)

The input values x(n) and y(n-k) are expressed in terms of their digits as follows.

$$x(n) = \sum_{j=0}^{d+\delta-1} X_j(n) r^{-j}, \quad X_j = 0 \text{ for } j \ge d$$

(3.3)

$$y(n-k) = \sum_{j=0}^{d+\delta-1} Y_j(n-k)r^{-j}, \quad Y_j(n-k) = 0 \text{ for } j \ge d$$

(3.4)

Note that  $d + \delta$  digits of x(n) and y(n - k) are required to produce  $\delta$  zeros and d digits of y(n). Consequently  $\delta$  zero digits have to be appended after the least significant input digit. At the end of the  $j^{th}$  iteration, j + 1 of the most significant digits of each input term have been consumed. The values of the inputs, represented by the j + 1 most significant digits, are given by:

$$x(n)[j] = x(n)[j-1] + r^{-j}X_j(n), \quad x(n)[-1] = 0$$

(3.5)

$$y(n-k)[j] = y(n-k)[j-1] + r^{-j}Y_j(n-k), \quad y[-1] = 0$$

(3.6)

#### Deriving a Recurrence

At the end of each iteration, one output digit  $Y_j$  is produced based on the value of the scaled residual w[j]. The scaled residual at the end of the  $j^{th}$  iteration is defined as the difference between the scaled actual sum (obtained by using the j+1 most significant digits of the inputs) and the scaled computed sum (based on the j output digits produced thus far). The scaled residual is expressed as follows.

$$w[-1] = 0 (3.7)$$

$$w[j] = r^{j} \{ r^{-\delta}(cx(n)[j] + \sum_{k=1}^{N} a_{k}y(n-k)[j] \}$$

-y(n)[j-1]\}, j = 0, 1, 2... (3.8)

Using Equations (3.5), (3.6) and (3.8), a recurrence in terms of the residual w[j] is formed.

$$w[-1] = 0$$

$$w[j] = r\{w[j-1] - Y_{j-1}(n)\} +$$

$$r^{-\delta}\{cX_{j}(n) + \sum_{k=1}^{N} a_{k}Y_{j}(n-k)\}, \quad j = 0, 1, 2...$$

(3.10)

## Digit Selection and Residual Bounds

The output digit  $Y_j$  is selected based on the value of w[j], i.e.,  $Y_j = sel(w[j])$ . The selection function maps w[j] into the digit set  $\{-\rho, \ldots, \rho\}$  such that the residual is bounded as follows.

$$\underline{\xi} \le (w[j] - Y_j(n)) \le \overline{\xi} \tag{3.11}$$

The values of  $\overline{\xi}$  and  $\underline{\xi}$  depend on the representation of the residual and the selection function. In general  $\overline{\xi} \neq -\underline{\xi}$ . For a rounding selection function with a non-redundant representation of the residual,  $\overline{\xi} = -\underline{\xi}$ .

## 3.2 Expression for On-Line Delay

The on-line delay is obtained from (3.10) by calculating the maximum and minimum values of w[j], which guarantee a bounded residual. The maximum value of w[j] occurs when the maximum residual is added to the maximum values of

the coefficients' multiples. The minimum value of w[j] occurs when the minimum residual is added to the minimum values of the coefficients' multiples. The maximum and minimum value cases may be expressed as follows, using the bounds specified in (3.11) and the definition of s in (3.1).

$$\overline{\xi} + \rho = r\overline{\xi} + s\rho r^{-\delta} \tag{3.12}$$

$$\underline{\xi} - \rho = r\underline{\xi} - s\rho r^{-\delta} \tag{3.13}$$

To obtain an expression for  $\delta$ ,  $\overline{\xi}$  and  $\underline{\xi}$  must be evaluated by considering the residual and the selection function. The residual w[j] is maintained in carry-save form for a fast recurrence step. To reduce  $\overline{\xi}$  and  $-\underline{\xi}$ , and perform digit selection, the integer part and  $\beta$  fraction bits of the sum and carry words (representing w[j]) are added by a CPA. Thus w[j] is represented in the partial carry-save form shown below.

If rounding selection is based on this partial carry-save representation of w[j], then  $\overline{\xi}$  and  $\xi$  are given by (3.14) and (3.15).

$$\overline{\xi} = 0.5 + 2^{-\beta} + \varepsilon \tag{3.14}$$

$$\underline{\xi} = -0.5 \tag{3.15}$$

The small value  $\varepsilon$  depends on the precision of the partial carry-save form. If f is the number of fraction bits in the partial carry-save form,  $\varepsilon = -2^{1-f}$ .

Consider the maximum values of the two sides of (3.10):

$$\max(w[j]) \leq \max(r\{w[j-1] - Y_{j-1}(n)\}) + \max(r^{-\delta}\{cX_j(n) + \sum_{k=1}^{N} a_k Y_j(n-k)\})$$

(3.16)

The maximum values in (3.16) can be substituted using (3.11) and (3.14) to get:

$$0.5 + 2^{-\beta} + \rho + \varepsilon \leq r(0.5 + 2^{-\beta} + \varepsilon) + r^{-\delta} s \rho \tag{3.17}$$

Solving 3.14 yields an expression for  $\delta$ :

$$\delta = \left\lceil \log_r \frac{s\rho}{\rho - (r-1)(0.5 + 2^{-\beta} + \varepsilon)} \right\rceil$$

(3.18)

A slightly different expression for  $\delta$  can be derived by considering the minimum values of (3.10) and Equations (3.11) and (3.15). This value of  $\delta$  may not satisfy the maximum bound on the residual.

Thus  $\delta$  may be calculated using Equation (3.18) given the digit set, the radix, the filter expression and  $\beta$ . For a second-order recurrence, Table 3.1 shows the on-line delays for different maximum magnitudes of coefficients, radices and digit sets. The minimum value of  $\delta$  is obtained when  $\beta$  is infinite, which requires all fraction bits to be included in the CPA. A higher value of  $\delta$  may result if  $\beta$  is small. Thus  $\beta$  is chosen to minimize the clock period, by making a suitable compromise between CPA length and  $\delta$ . For a given digit set and radix, the on-line delay is decremented once every time s is scaled down by the radix. This trade-off between coefficient magnitudes and  $\delta$  is seen in (3.18).

| s     | 4 | 5 | 6 | 4 | 5 | 6 | 4 | 5 | 6 | 4 | 5 | 6 | 4 | 5 | 6 | 4 | 5 | 6 |

|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Radix |   | 2 |   |   | 4 |   |   | 4 |   |   | 8 |   |   | 8 |   |   | 8 |   |

| ρ     |   | 1 |   |   | 2 |   |   | 3 |   |   | 4 |   |   | 5 |   |   | 6 |   |

| β     | 2 | 3 | 3 | 3 | 4 | 4 | 2 | 3 | 3 | 5 | 6 | 6 | 3 | 3 | 3 | 2 | 2 | 2 |

| δ     |   | 4 |   |   | 3 |   |   | 2 |   |   | 2 |   |   | 2 |   |   | 2 |   |

Table 3.1: Variation of On-Line Delay

# 3.3 Second-Order Radix-4 Implementations

This section outlines four implementations based on design parameters selected from Table 3.1. The problem of selecting the architecture that yields the fastest rate is discussed first. Circuit-level improvements that minimize critical path delay and reduce the number of gates are described later. The on-line delay of an implementation,  $\delta_{imp}$ , is defined next.

Definition 3 ( $\delta_{imp}$ ) For a digit recurrence implementation,  $\delta_{imp}$  is the minimum number of clocks between an input digit and the output digit of identical weight. For any digit recurrence implementation,  $\delta_{imp} \geq 1 + \delta$ .

For the architectures described here,  $\delta_{imp} = \delta + 2$ . The 2 added to  $\delta$  corresponds to the number of stages: one for implementing the digit recurrence and

one for latching the selected output digit.

## Choosing a Maximum Rate Architecture

A maximum rate architecture minimizes  $\delta_{imp}t_{clk}$ . Since  $\delta_{imp}$  is the sum of  $\delta$  and the number of stages, digit recurrence parameters must be chosen to minimize  $\delta$  and  $t_{clk}$ . In addition, the architecture must be designed to minimize  $t_{clk}$  and the number of stages. The choice of parameters is discussed first and the architecture is discussed next.

The parameters of the recurrence are expressed in (3.18). Given s, the task is to determine  $\delta$ ,  $\beta$ , r and  $\rho$  such that  $t_{clk}$  is minimized. The value of  $t_{clk}$  increases with r and  $\rho$ . Large values of  $\beta$  also increase  $t_{clk}$ . Table 3.1 shows the design space for small r. The choice between radix-4 and radix-8 is clear, since  $\delta$  is 2 and radix-4 results in lower  $t_{clk}$ . The choice between radix-2 and radix-4 depends on the technology. As discussed in Section 2.1, the radix-4 implementation is about 13% slower than the radix-2 implementation. However, the radix-2 scheme has a larger  $\delta$  which more than offsets the faster clock rate. Thus the radix-4 design with  $\rho=3$  is the best choice for maximum rate in LCA10000 Array technology [LS187]. The choice of  $\rho=3$  requires precomputing and storing the coefficient multiples of 3. To quantify the maximum rate differences between  $\rho=3$  and  $\rho=2$ , designs for both digit sets are implemented.

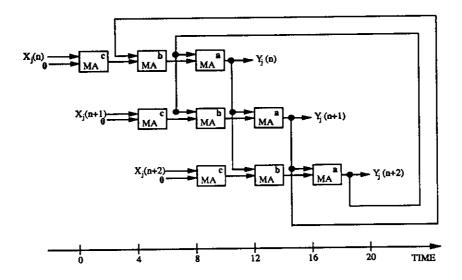

Choosing the architecture consists mainly of determining the number of stages in the pipeline. Since the digit recurrence requires feedback, the number of stages in the pipeline cannot be increased arbitrarily. The number of stages that minimize  $\delta_{imp}t_{clk}$  is determined by a delay analysis. Consider a 2-stage design. The first stage implements multiplication and addition to compute w[j], and the second stage implements digit selection. The first stage takes 14ns and the second 6ns. Thus  $t_{clk}=14$ , and the total delay is 56ns. For a single stage design,  $t_{clk}\approx 20ns$  (i.e., 14+6), and  $\delta_{imp}=3$ , giving a total delay of 60ns. Thus a 2-stage design is faster than a single stage one. The first stage can be pipelined further to obtain a faster clock. This is discussed later in the chapter.

For designs with different number of stages with the same total delay, the cost-effective choice is the design with the faster clock. For example, consider a 2-stage design with  $t_{clk}=15$  and  $\delta_{imp}=4$ , and a 3-stage design with  $t_{clk}=12$  and  $\delta_{imp}=5$ . Both have a total delay of 60ns. The number of modules required to achieve the maximum rate is given by  $\lceil \frac{d+\delta}{\delta_{imp}} \rceil$ . With  $\delta=2$  and d=8, the number of modules required for maximum rate is 3 for the 2-stage design, and 2 for the 3-stage design. The following sections consider 2-stage and 3-stage designs.

#### Circuit-Level Optimizations

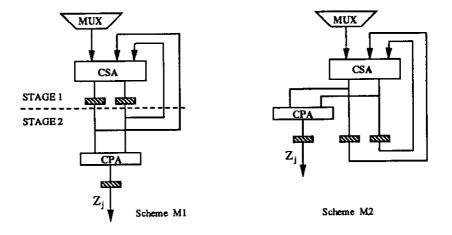

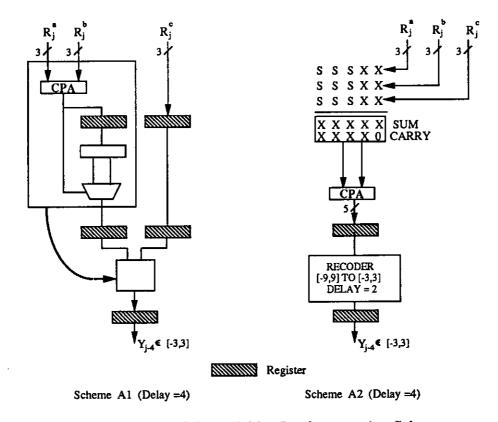

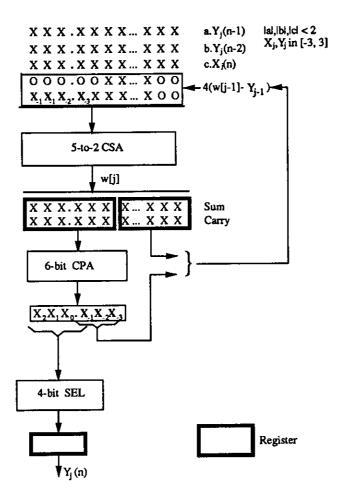

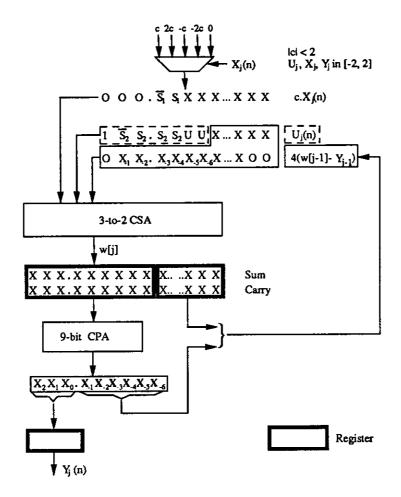

Figure 3.1 shows a 2-stage design, for  $\rho = 3$  and s = 6, and Figure 3.2 shows two optimizations that reduce the number of gates and minimize potential critical path delay. The first optimization includes the rounding selection in the CSA array. The second optimization reduces the number of gates by optimizing the sign extension required by 2's complement. The rounding optimization is discussed next.

As Equation (3.10) shows, the selected digit  $Y_{j-1}$  must be subtracted from the residual w[j-1] in each iteration. For a rounding selection function, the integer part produced by the CPA is incremented by the leading fraction bit to produce the selected digit. Figure 3.1 shows the selection step based on the four most significant bits produced by the CPA.

The selection may be optimized by eliminating the separate increment step and including the increment in the CSA array. The selection optimization, along with additional logic simplification, is shown in Figure 3.2. Adding  $\frac{1}{2}$  to the residual produces the correct digit for rounding selection. To compensate for the addition, the scaled residual must be reduced by 2 in the next iteration. As shown in Figure 3.2, this is accomplished by adding -2 to the scaled residual (the 110.1X... term). A side effect of this addition is that a -2 output digit is produced, instead of a 0 digit, immediately after the sum and carry registers are cleared. This is remedied by clearing the output digit register a clock later.

Figure 3.3 shows the optimized 2-stage scheme chosen for implementation. The critical path consists of the buffers which fan out the digit to the multiplexers, the 7-input multiplexes which select the coefficient multiple, and the 5-to-2 CSA tree. The critical path can be shortened by:

- 1. Selecting a small digit set, i.e.,  $\rho = 2$ .

- 2. Introducing another stage for multiplexing the coefficients of digits  $Y_j(n-2)$  and  $X_j(n)$  as shown in Figure 3.4. This stage does not reduce the maximum rate because the delay incurred by  $Y_j(n-1)$  is still the same.

Consequently, four designs are considered for implementation:

- 1. 2-stage design with  $\rho = 3$  and  $\delta_{imp} = 4$ .

- 2. 3-stage design with  $\rho = 3$  and  $\delta_{imp} = 4$ .

- 3. 2-stage design with  $\rho = 2$  and  $\delta_{imp} = 5$ .

4. 3-stage design with  $\rho = 2$  and  $\delta_{imp} = 5$ .

The designs are implemented in LSI Logic Corporation's LCA 10000 Series Compacted Array Technology [LSI87]. The implementations do not include the I/O buffers and pads. The next section compares the performance and cost of the implementations.

## 3.4 Performance and Cost

This section compares the performance (number of samples per second) and cost (number of gates), based on the simulation results obtained from the implementations. Comparisons are meaningful only when the following factors are identical for all implementations.

- 1. Technology.

- 2. Sum of coefficient bounds, s, defined in (3.1).

- 3. Number of digits, d, per word of input and output.

- 4. Number of bits, m, used in the implementation to represent coefficient in 2's complement.

Typically, m or d is specified and the number of fraction bits required in the implementation, f, must be determined. For the radix-4 implementations described, the three values are related as follows.

$$m = 2d (3.19)$$

$$f = m + 2(\delta - 1) \tag{3.20}$$

The cost measures derived from the simulation are the number of gates used for the most significant part of the module and the number of gates per fraction bit slice. The most significant part includes the integer bits, a few fraction bits (typically  $\beta$ ) and the selection logic. The number of gates used for a similar implementation with f fraction bits are given by the following expressions.

Figure 3.1: Composite 2-Stage On-Line Scheme  $(\delta_{imp} = 4)$

Figure 3.2: Optimizing Composite On-Line Scheme

Figure 3.3: Optimized 2-Stage Composite On-Line Scheme  $(\delta_{imp} = 4)$

Figure 3.4: Optimized 3-Stage Composite On-Line Scheme  $(\delta_{imp} = 4)$

```

Composite 2-stage (\rho=2): Gates<sub>module</sub> = 372+89f

Composite 2-stage (\rho=3): Gates<sub>module</sub> = 336+125f

Composite 3-stage (\rho=2): Gates<sub>module</sub> = 390+109f

Composite 3-stage (\rho=3): Gates<sub>module</sub> = 354+145f

```

Expressions for three performance measures are given below. The maximum rate and the rate of a single module are obtained by finding the minimum clock period,  $t_{clk}$  (ns), at which the implementations can be properly simulated. The minimum clock period increases very little with higher precision. The increase is purely due to the larger fan-out caused by the increased number of digit multiplexers.

- 1. Rate of a single module (Msample/s) =  $\frac{1000}{t_{elk}(\delta+d)}$

- 2. Maximum Rate (Msamples/s) =  $\frac{1000}{t_{elk}\delta_{imp}}$

- 3. Number of modules for Maximum Rate =  $\left\lceil \frac{d+\delta}{\delta_{imp}} \right\rceil$

Table 3.2 shows the performance and cost for four implementations with I/O words of 16 bits (d=8) and s=6. The fastest design has 3 stages and uses a digit set of  $\{-3,\ldots,3\}$ . The latency of the 3-stage modules from the x(n) or the y(n-2) input is 5 clocks. However, the maximum rate is determined by the latency from the y(n-1) input,  $\delta_{imp}$ , which is 4 clocks. The maximum rate of 1 sample per 4 clocks can be achieved using three modules. The number of Gates/Array is the total number of gates for as many modules as required to produce the maximum rate. Arrays are described in Chapter 5.

Table 3.2: Performance/Cost for Composite Word Modules (d = 8)

| Module Type       | ρ | $\delta_{imp}$ | Gates | $t_{clk}$ | Max. Rate | Gates  |

|-------------------|---|----------------|-------|-----------|-----------|--------|

|                   |   |                | /Mod. | ns        | (MSmp./s) | /Array |

| Composite 2-stage | 2 | 5              | 2152  | 14        | 14.3      | 5976   |

| Composite 2-stage | 3 | 4              | 2586  | 14        | 17.8      | 6798   |

| Composite 3-stage | 2 | 5              | 2570  | 11        | 18.8      | 7230   |

| Composite 3-stage | 3 | 4              | 2964  | 11_       | 22.7      | 7932   |

## CHAPTER 4

# Schemes Using On-Line Multiply-Add Modules

The Multiply-Add (MA) module is a useful building block in realizing conventional (bit parallel) FIR and IIR filters. The on-line MA module has a similar usefulness in building on-line filters, IIR in particular [Bra89a]. Sections 4.1 and 4.2 describe the design and implementation of an on-line MA module that is less pipelined but much faster than the implementation described in [Bra89a]. The design choices and decisions are similar to those faced in implementing a composite on-line module described in the previous chapter. Section 4.3 discusses performance and costs of two MA modules. It also compares the performance and cost of MA module implementations that compute (1.1) with the composite module implementations described in the previous chapter.

# 4.1 Design of MA Module

The computation performed by the on-line MA module is generically expressed by y = cx + u, where x, y and u are on-line forms. Since the computation is a specific instance of Equation (1.1), with b = 0 and a = 1, the problem of designing a fast MA module is similar to that of designing a composite module which implements (1.1). The recurrence for the MA, an instance of (3.10), is given by:

$$w[-1] = 0 \tag{4.1}$$

$$w[j] = r\{w[j-1] - Y_{j-1}(n)\} +$$

$$r^{-\delta}\{cX_j(n) + U_j(n)\}, \quad j = 0, 1, 2...$$

(4.2)

To achieve a fast implementation of the recurrence, the following parameters have to be selected.

- On-line delay  $\delta$  and module delay  $\delta_{imp}$ .

- Radix r and digit set  $\{-\rho, \ldots, \rho\}$  for X, Y and U.

- Number of fraction bits required for selection,  $\beta$ .

The stability limit for second-order filters requires that |c| < 2. Consequently, s = 3 for an MA module. Equation (3.18) can be used to select appropriate parameters. Table 4.1 shows the variation of  $\delta$  and  $\beta$  for radices 2, 4 and 8. The lowest on-line delay is obtained with a digit set of  $\{-6, \ldots, 6\}$  for a radix-8 implementation. The advantage of lower on-line delay is offset by the longer clock period required for the larger digit set. Similarly, the radix-2 design has a slightly shorter clock period which is more than offset by the larger on-line delay. This leaves the radix-4 designs for implementation. The implementations and circuit-level optimizations for the radix-4 designs are discussed next.

Table 4.1: Variation of On-Line Delay for MA Module (s = 3)

| Radix | 2 | 4 | 4 | 8 | 8 | 8 | 8 |

|-------|---|---|---|---|---|---|---|

| ρ     | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| β     | 3 | 5 | 2 | 5 | 3 | 5 | 3 |

| δ     | 3 | 2 | 2 | 2 | 2 | 1 | 1 |

# 4.2 Implementation of MA Module

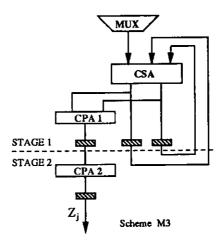

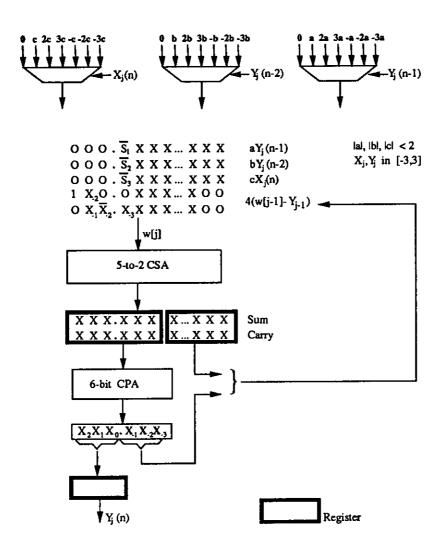

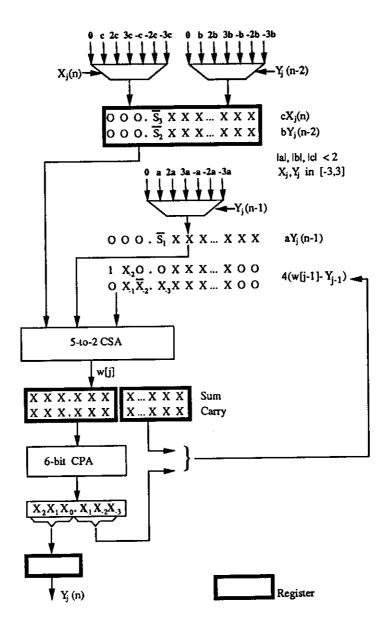

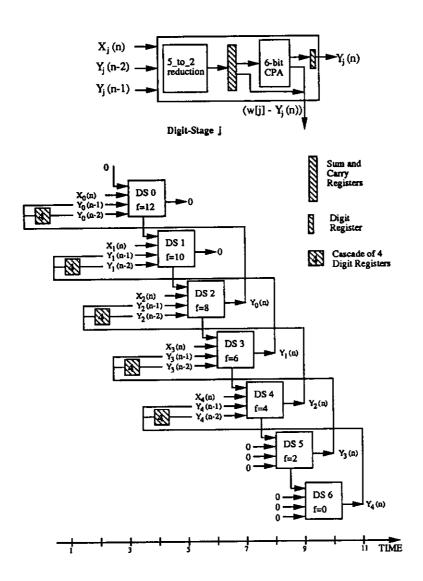

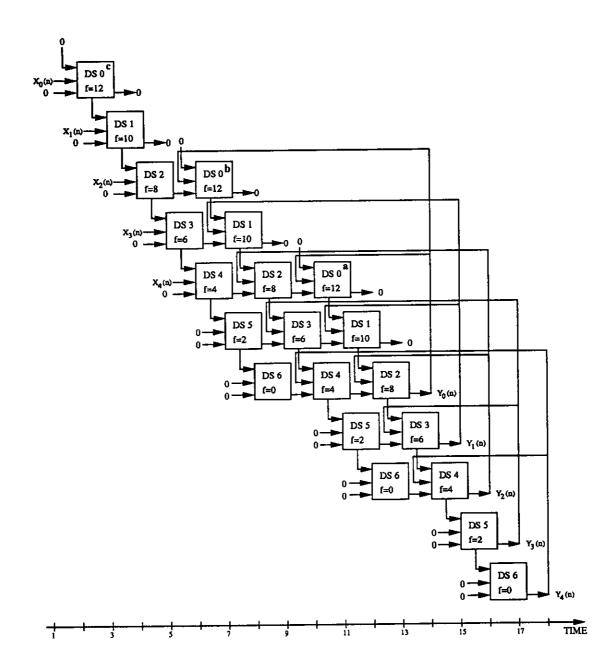

The implementation of the radix-4 MA modules is similar to the 2-stage composite module shown in Figure 3.1. The differences are in the number of terms and the length of the CPA. Figure 4.1 shows the the circuit-level optimizations for the MA modules. Two of these optimizations, performing rounding selection in the CSA and logic minimization, were discussed in Section 3.3 for the composite module. The third optimization replaces a 4-2 CSA with a 3-2 CSA, as shown in Figure 4.1. This is accomplished by observing the following.

- 1. The  $U_j(n)$  term requires only 4 fraction bits.

- 2. The shifted Partial Carry-Save form has  $\beta 2$  zeros in the most significant fraction part due to the CPA.