# Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

THE UCLA MIRROR PROCESSOR: CONTROL IMPLEMENTATION AND TESTING CONSIDERATIONS FOR A VLSI RISC WITH MICRO ROLLBACK

Titus Lai

January 1991 CSD-910001

# The UCLA Mirror Processor: Control Implementation and Testing Considerations for a VLSI RISC with Micro Rollback

Titus Lai

Computer Science Department University of California Los Angeles, California 90024-1596 U.S.A.

#### Abstract

Many methods for achieving fault tolerance are based on the use of concurrent error detection — the outputs of every component are checked before being used by any other component. In order to minimize the performance degradation usually associated with concurrent error detection, checking can be done in parallel with the transfer of information between components. Since module state may be modified before an error is flagged, system modules support *micro rollback* — the ability to undo recent state changes and roll back the system to its state prior to the clock cycle in which the error originated.

The UCLA Mirror Processor is a RISC microprocessor capable of micro rollback. Concurrent error detection is accomplished by running two Mirror Processor chips in lock-step synchronization and comparing their external outputs and a compressed signature of their internal states.

This report details the function, timing, and implementation of the Mirror Processor controller, emphasizing the error detection and recovery mechanisms. The area overhead of the error detection and rollback logic is shown to be quite large: 67% of the controller area is dedicated to micro rollback. The performance overhead is found to be minimal. *Functional testing*, in which a processor chip is tested in software through the use of its normal instruction set, is shown to be adaptable to the Mirror Processor. Special instructions added for testing the error detection and rollback logic are presented, along with example test procedures using these instructions.

# **Table of Contents**

| Chapter 1: Introduction                    | 1  |

|--------------------------------------------|----|

| 1.1. Micro Rollback                        | 1  |

| 1.2. Overview of Mirror Processor          | 2  |

| 1.3. Main Processor                        | 3  |

| 1.4. Error Detection                       | 4  |

| 1.5. Error Recovery                        | 4  |

| Chapter 2: The Mirror Processor Controller | 5  |

| 2.1. Controller Design Considerations      | 5  |

| 2.2. Description of the Controller         | 6  |

| 2.3. Controller Timing                     | 8  |

| 2.3.1. Processor Timing                    | 8  |

| 2.3.2. Memory Interface Timing             | 8  |

| 2.3.3. Normal Instruction Cycle            | 11 |

| 2.3.4. Interrupts and Traps                | 13 |

| 2.3.5. Rollbacks                           | 14 |

| 2.4. Details of Controller Implementation  | 14 |

| 2.4.1. busIR                               | 14 |

| 2.4.2. busIR Latch and Driver              | 15 |

| 2.4.3. Next State Logic                    | 15 |

| 2.4.4. PLA's                               | 16 |

| 2.4.5. Condition Code Logic                | 17 |

| 2.4.6. Post-FSM Logic and Valid Bit Logic  | 18 |

| 2.4.7. Memory Control Logic                | 19 |

| 2.4.8. Memory Enable Signals               | 19 |

| 2.4.9. Interrupt Logic                     | 20 |

| 2.4.10. Comparator Logic                   | 21 |

| 2.4.11. Controller Rollback Memory         | 23 |

| 2.4.12. Critical Paths                     | 24 |

| 2.5. Alternate Wait State Timing           | 25 |

| 2.6. Clock Generation                      | 26 |

| Chapter 3: Error Detection and Recovery    | 32 |

| 3.1. Rollback Timing                       | 32 |

| 3.1.1. Internal Rollback                   | 32 |

| 3.1.2. External Rollback                   | 32 |

|     | 3.1.3. Absolute and Relative Rollbacks     | 32 |

|-----|--------------------------------------------|----|

|     | 3.2. Error Detection Timing                | 33 |

|     | 3.2.1. Register File Parity Errors         | 33 |

|     | 3.2.2. busIN Parity Error                  | 33 |

|     | 3.2.3. Comparison Errors                   | 33 |

|     | 3.2.4. busOUT Parity Error                 | 33 |

|     | 3.2.5. Multiple Rollbacks                  | 34 |

|     | 3.3. Rollback Control Logic and Timing     | 36 |

|     | 3.3.1. Overview                            | 36 |

|     | 3.3.2. External Rollback Signals           | 37 |

|     | 3.3.3. Input Latches                       | 37 |

|     | 3.3.4. Internal Error Signals              | 37 |

|     | 3.3.5. Post-rollback Counter               | 38 |

|     | 3.3.6. Rollback Enable Bit and Counter     | 38 |

|     | 3.3.7. Internal Rollback Logic             | 38 |

|     | 3.3.8. Valid Bits                          | 39 |

|     | 3.3.9. Selection Logic                     | 39 |

|     | 3.3.10. Rollback Amount Encoder            | 40 |

|     | 3.3.11. Rollback Amount Arbitration        | 40 |

|     | 3.3.12. Frame Counter and Rollback Counter | 41 |

|     | 3.3.13. Shutdown Logic                     | 41 |

|     | 3.3.14. Pad Enabling                       | 42 |

|     | 3.3.15. Rollback Bit                       | 42 |

|     | 3.3.16. Rollback Procedure                 | 42 |

|     | 3.3.17. Critical Path                      | 43 |

|     | 3.4. State Repair                          | 43 |

| Ch  | apter 4: Controller Implementation         | 48 |

|     | 4.1. Layout                                | 48 |

|     | 4.2. Overhead                              | 48 |

|     | 4.2.1. Area Overhead                       | 48 |

|     | 4.2.2. Transistor Overhead                 | 51 |

|     | 4.2.3. Examples                            | 52 |

|     | 4.2.3.1. CMP                               | 52 |

|     | 4.2.3.2. RB                                | 54 |

|     | 4.2.3.3. STATE                             | 55 |

| Cha | apter 5: Simulation and Debugging          | 57 |

|     | 5.1. Architecture Level Simulation         | 57 |

|     | 5.2. Switch Level Simulation               | 58 |

| Cha | apter 6: Testing                           | 59 |

|     | 6.1. Testing Considerations                | 59 |

| 6.2. Testing Vanilla RISC                        | 59 |

|--------------------------------------------------|----|

| 6.2.1. Functional Testing                        | 59 |

| 6.2.2. Application of Functional Testing         | 62 |

| 6.3. Testing Error Detection and Rollback Logic  | 64 |

| 6.3.1. Test Instructions                         | 64 |

| 6.3.2. Error Recovery Test Procedures            | 65 |

| 6.3.2.1. State Compression Comparison Error      | 65 |

| 6.3.2.2. Register File Parity Error              | 66 |

| 6.3.2.3. Memory Access, Address Comparison Error | 67 |

| 6.3.2.4. Memory Access, Data Comparison Error    | 67 |

| 6.3.2.5. Input Bus (busIN) Parity Error          | 68 |

| Chapter 7: Conclusion                            | 69 |

| Appendix A: Controller Signals                   | 71 |

| Appendix B: Test Program Listings                | 79 |

| Appendix C: Error Detection Tests                | 93 |

| Appendix D: Verification Instructions            | 94 |

| References                                       | 96 |

# **List of Figures**

| Figure 1.1: Prototypical Register with Delayed Write Buffer | 2  |

|-------------------------------------------------------------|----|

| Figure 1.2: Mirror Processor                                | 3  |

| Figure 2.1: Controller                                      | 7  |

| Figure 2.2: Memory Interface Timing                         | 10 |

| Figure 2.3: Control Timing                                  | 12 |

| Figure 2.4: busIR Latch and Driver                          | 15 |

| Figure 2.5: PLA Bit Slice (\$\phi_{1b}\$ PLA)               | 18 |

| Figure 2.6: Memory Address Enable Bit                       | 20 |

| Figure 2.7: Comparator Logic Block                          | 22 |

| Figure 2.8: Clock Generator                                 | 27 |

| Figure 2.9: d4 Delay Inverter                               | 28 |

| Figure 2.10: Slave Clock Generation Timing                  | 28 |

| Figure 2.11: Clock Generation Timing                        | 29 |

| Figure 2.12: $\phi_2$ Generation                            | 30 |

| Figure 2.13: $\phi_2$ Clock Generation Timing               | 31 |

| Figure 3.1: Rollback Control                                | 36 |

| Figure 3.2: Rollback Amount Arbitration Logic               | 41 |

| Figure 3.3: Rollback Procedure                              | 44 |

| Figure 3.4: Rollback Control Timing                         | 45 |

| Figure 3.5: Rollback Amount Arbitration                     | 46 |

| Figure 3.6: State Repair Procedure                          | 47 |

| Figure 4.1: Controller Floorplan                            | 48 |

# List of Tables

| Table 2.1: Data Size Line Encoding                         | 9  |

|------------------------------------------------------------|----|

| Table 2.2: Interrupt Vectors                               | 21 |

| Table 2.3: Comparison Logic Error Signals                  | 22 |

| Table 4.1: Blocks in Controller Layout                     | 49 |

| Table 4.2: Controller Implementation Statistics            | 50 |

| Table 4.3: Area Overhead, Dimensions                       | 50 |

| Table 4.4: Area Overhead, Percentage of Total Area         | 51 |

| Table 4.5: Transistor Overhead, Number Used                | 52 |

| Table 4.6: Transistor Overhead, Percentage of Total Number | 53 |

| Table 6.1: Instruction Argument Definitions                | 64 |

#### 1. INTRODUCTION

In a fault-tolerant computing system, the ability to detect errors and recover quickly from them is of utmost importance. In many systems, checkers are placed at the outputs of each module in the system in order to confine the error to that module and prevent it from causing damage elsewhere. However, because module outputs must be checked before being sent to other modules, the system can experience significant delays while the outputs are being checked.

One way to get around this problem is to do the checking at the same time the outputs are being sent to other modules. In this case, the results of the checker may not be ready until several cycles later, at which point an error may have propagated to other modules. Thus, it will be necessary to undo the results of the last few cycles and restore the state of the system to a known error-free state.

#### 1.1. Micro Rollback

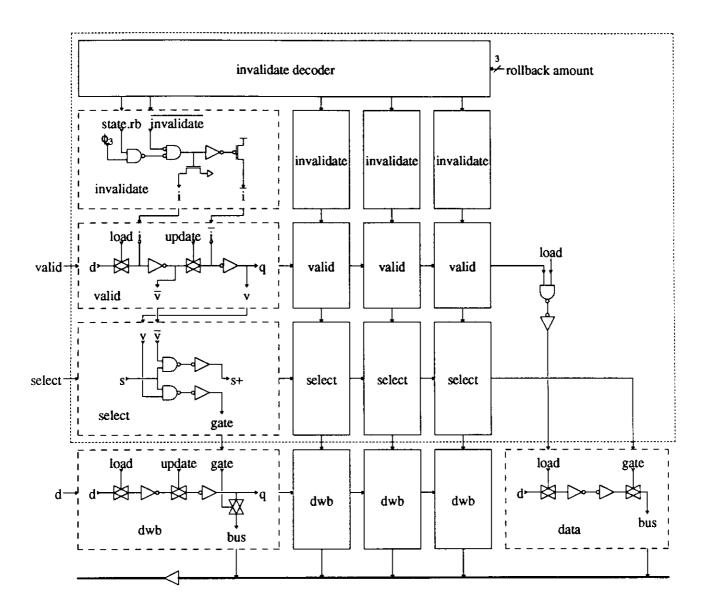

A method of backing up a CPU several cycles, known as *micro rollback*, is described in [8]. It basically involves the placing of an N-entry delayed write buffer (DWB) at each register that holds information across cycles (e.g., program counter, status register, instruction register, etc.). Figure 1.1 shows a circuit diagram of a typical DWB. When a register is written, it is actually written into the first entry of the DWB. At each subsequent cycle, the entire DWB is shifted by one entry, and the last entry is written into the actual register. Along with each entry in the DWB, there is a bit indicating whether that entry is valid or not. The bit is normally set when the register is written; to cancel the results of the last M cycles, the valid bits of the M most recent entries are cleared (where  $M \le N$ ). When the register is read, a selection circuit picks out the most recent entry with a set valid bit. In addition, when the DWB shifts, the actual register is written only if the valid bit is set. The same idea is also used in the register file, except that the DWB entry includes the address of the register being written each cycle.

The Mirror Processor is a VLSI processor employing hardware support for micro rollback, based largely on the Berkeley RISC II processor [4]. One of its intended goals is to evaluate the area and

Figure 1.1: Prototypical Register with Delayed Write Buffer

performance overhead of micro rollback. This report describes the implementation of the controller of the Mirror Processor, details its rollback and recovery schemes, and presents some issues related to the testability of the processor.

# 1.2. Overview of Mirror Processor

The Mirror Processor (Figure 1.2) is an implementation of a fault-tolerant RISC processor employing hardware support for micro rollback. It is designed to detect and recover from all single transient errors and, in some cases, multiple transient errors without the need for extensive error-

correction code circuitry and without the sacrifice in speed suffered by checking data before its use.

Figure 1.2: Mirror Processor

# 1.3. Main Processor

At its core, the processor is a 2  $\mu$ m CMOS implementation of the Berkeley RISC II processor (MOSIS SCMOS design rules with  $\lambda$ =1  $\mu$ m). Under basic operation it is, with a few exceptions, binary-compatible with RISC II. Built on top of that are various error-checking blocks and delayed write buffers which are transparent to the user. In addition, several new instructions have been added to the instruction set for the purposes of testing the rollback logic.

#### 1.4. Error Detection

The processor is designed for duplex operation: a *master* chip functions as the main processor in the computer system, while a *slave* chip follows along in lock-step synchronization. The slave performs the same operations as the master, but instead of writing its outputs to the external bus, it compares them with the values written by the master. An error is flagged if any differences are found.

In addition, parity checkers are present in each processor to detect errors in values read out of the register file and in values read from the external input data bus (busIN). Each processor does its own local parity checking and flags an error if a parity error is detected.

#### 1.5. Error Recovery

An external *rollback* signal is made available to the entire processor system (CPU, memory manager, instruction cache, etc.). Whenever either processor detects an error, it pulls the rollback line and forces the entire system to roll back a certain number of cycles. If the rollback occurred because of a comparison error or because of a parity error on the external input data bus, it is assumed that a transient fault caused the error and that simply rolling back should remove the fault. However, if the error was a parity error on a register file read, the faulty value may have been present in the register file for a long time prior to its being read, so simply rolling back may not remove the fault. In this case, the processor with the good value must send that value to the other processor. This procedure is known as *state repair*, and it takes place after any rollback caused by a parity error.

#### 2. THE MIRROR PROCESSOR CONTROLLER

This chapter presents the Mirror Processor controller design in detail. The data path design is presented in [5].

# 2.1. Controller Design Considerations

There were many possible ways that the controller for the Mirror Processor could have been implemented. As the processor is a RISC processor, there are relatively few instructions, and all of them are simple instructions in the sense that they only perform one operation. Because of the simplicity of the instruction set, it is not necessary to build a microprogrammed controller; it is possible to efficiently hardwire the controller, which can then run significantly faster than a ROM with a microprogram.

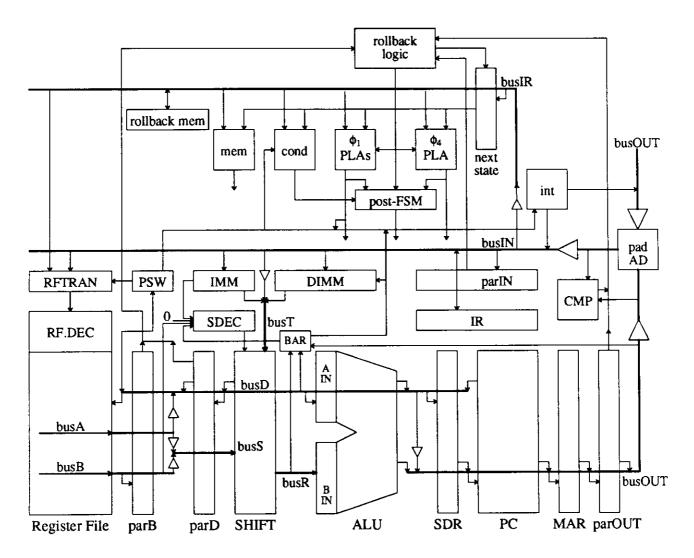

The original RISC II has a single generalized decoder to decode the opcode and generate 39 control bits which are then AND'ed with the various clock signals to produce 100 control signals (including multiple copies, clock signals, and control bits with no clock qualification). Unfortunately, such a simple scheme could not be used in the Mirror Processor controller. Many of the control signals are dependent not only on the opcode but also on the various rollback and repair signals. In addition, the Mirror Processor has about double the number of control bits as RISC II, due to the additional logic required to implement error detection and micro rollback. In particular, the controller takes 69 inputs and generates 134 control signals, 68 of which are internal to the controller and 66 of which are sent to the data path. In addition, it generates 17 external signals and four clock signals. Note that unlike in RISC II, there is no distinction between "control bits" and "control signals"; every signal already has some sort of clock qualification as it is generated.

A simpler way to implement the control would be to use one or two PLA's (Programmable Logic Arrays) or ROM's to generate all of the control signals. As noted before, because the Mirror Processor has a short cycle time and relatively few control signals, a ROM would require too much time to operate and take up too much area to be a practical solution.

PLA's, on the other hand, present the best compromise between speed/area and design/layout effort. Thus, it was decided that as many of the control signals as possible would be generated directly by several PLA's. However, several of the inputs to the controller become valid much later than the instruction. In order to allow the PLA's enough time to evaluate, it was decided not to have them wait for the late signals; instead, those control signals depending on the late inputs would be generated by random static logic. In addition, some signals have to become valid as soon as possible after the arrival of the instruction. These signals are also generated by random static logic.

# 2.2. Description of the Controller

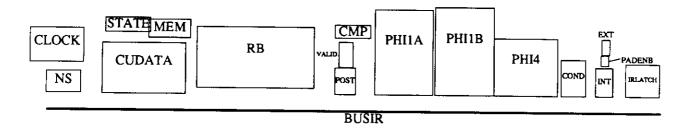

The controller of the Mirror Processor is shown in Figure 2.1. Instructions come in from the pads on busIN and are latched onto busIR. A four-state finite state machine keeps track of whether the processor is executing a normal instruction, executing the second cycle of a two-cycle instruction, or performing state repair. The Next State Logic block computes the next state based on the incoming opcode and on the repair signals generated by the Rollback Logic (Chapter 3). The next state, plus the opcode and the repair signals, are sent to three PLA's that decode the opcode and generate the majority of the control signals used by the data path.

Of the signals that aren't generated by the PLA's, most of the rest of them are generated by the Post-FSM Logic and Valid Bit Logic blocks. They produce signals that are dependent on values coming from the Rollback Logic, Interrupt Logic, and Condition Code Logic blocks, all of which produce their results well after the instruction arrives. The Valid Bit Logic block generates the valid bits used by all of the DWBs, while the Post-FSM Logic block generates the rest of these "late signals." There is, in addition, a separate Condition Code Logic block used to analyze the condition codes from the PSW and generate a condition bit used to control jump instructions; it is separate from the PLA's because it too depends on signals that arrive long after the instruction. Finally, a separate Memory Control Logic block generates the signals used to initiate a memory access; they are not generated by one of the PLA's because they are needed as soon as possible after the arrival of the opcode.

The remaining blocks handle inputs from external sources other than the incoming instruction. The Interrupt Logic Block monitors the external *interrupt*, *reset*, and *shutdown* lines as well as signals from the data path indicating a trap condition. It decides if the current cycle will be interrupted and gates both the calli instruction onto *busIN* and the proper interrupt vector onto *busOUT*. The Rollback Logic block serves double duty: it monitors the internal parity and comparison error signals and signals a rollback to the rest of the system if an error is detected, and at the same time it monitors the external rollback and rollback amount lines and signals the rest of the processor that a rollback is taking place if the line is pulled. Finally, a DWB saves the contents of *busIR* and one of the state bits each cycle and restores them on a rollback.

Figure 2.1: Controller

The generation of the four clock phases is done on-chip in the Clock Generator block. However, in

order to allow more control over the clock signals when testing the processor, separate input pads for each of the four signals is provided as well.

The implementation details of each of the controller blocks are given in Section 2.4 and summarized in Section 4.

#### 2.3. Controller Timing

This section details the timing of the Mirror Processor from the point of view of the controller.

Timing as it relates to the data path is covered in greater detail in [5].

# 2.3.1. Processor Timing

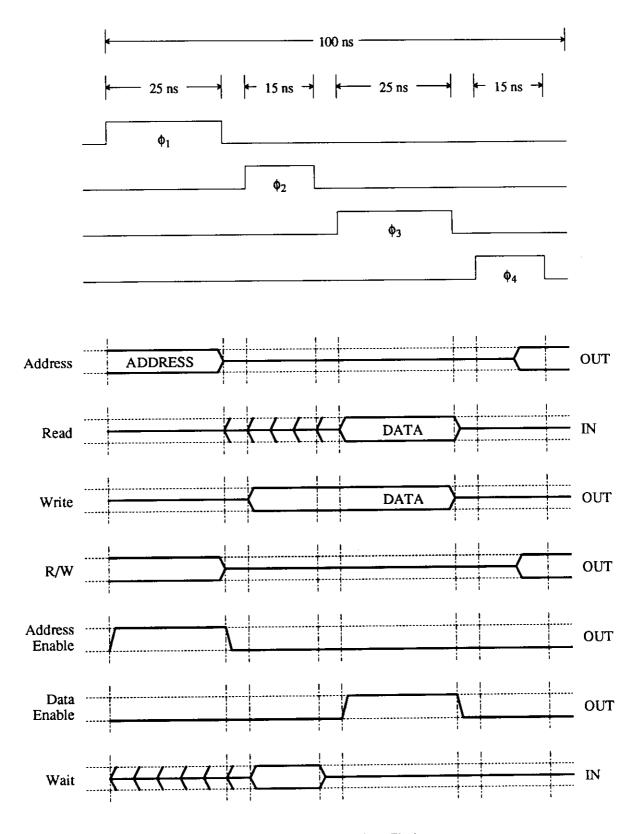

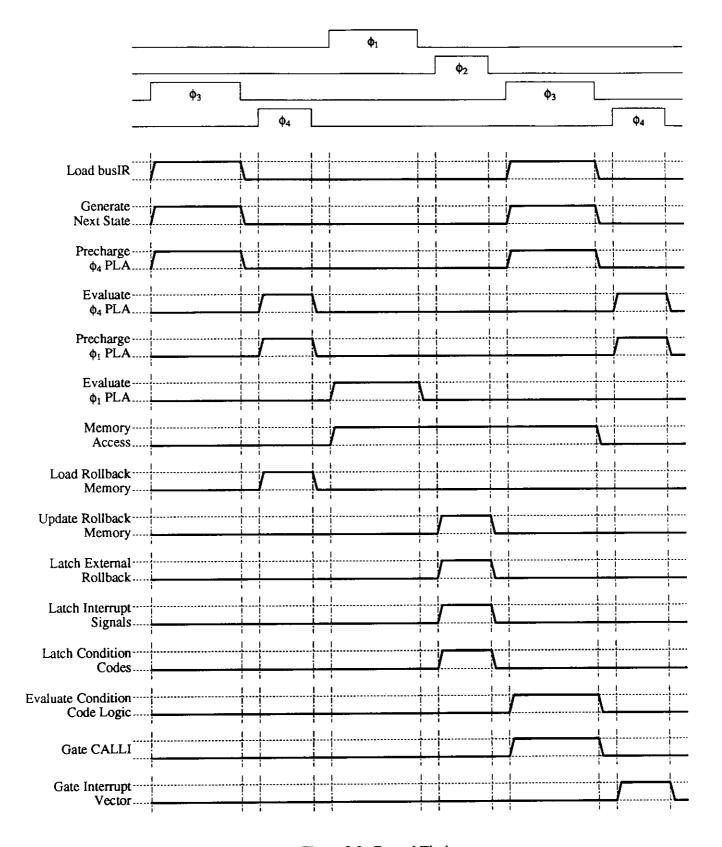

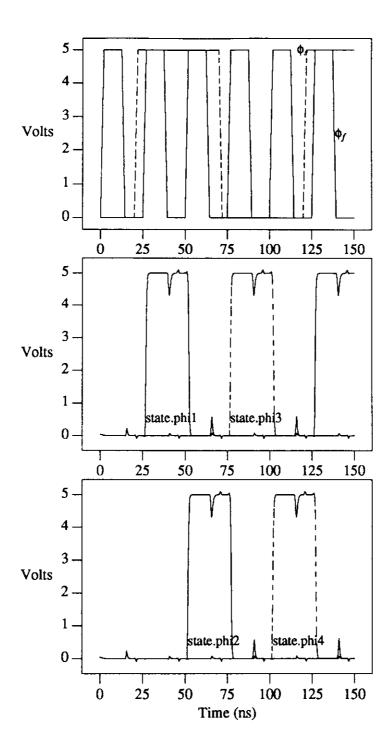

The processor runs on a four phase clock with a total cycle time of 100 ns. The first and third phases ( $\phi_1$  and  $\phi_3$ ) are 30 ns each (25 ns high, 5 ns low), and  $\phi_2$  and  $\phi_4$  are 20 ns each (15 ns high, 5 ns low).

# 2.3.2. Memory Interface Timing

Figure 2.2 shows the timing used by the processor to communicate with the memory system. The address of the word, halfword, or byte being accessed is gated onto the address/data lines, the *data size* lines are set (the encoding is the same as in RISC II; see Table 2.1), and the *read/write* line is set to indicate the type of access (0 = read, 1 = write), after which the *address enable* line is asserted. It is assumed that the memory does not run on the same clock as the processor, so the *address enable* line is present to tell the memory when to begin the access. On the leading edge of the *address enable*, the memory can assume that the address and the *read/write* signal are stable and latch them in. If the memory cannot retrieve the requested data (on a read) immediately, it has approximately 25-30 ns to assert the *wait* line (45 ns minus time to go through pads minus delay from rising edge of  $\phi_1$  to rising edge of *address enable*), as the processor must latch the *wait* signal at the end of  $\phi_2$ . If the memory can respond immediately and the access is a read, it should begin gating the data onto the address/data lines

immediately after the falling edge of address enable and continue to do so until the falling edge of the data enable signal. If the access is a write, the memory should wait until the rising edge of data enable, at which time the data to be stored should be stable on the address/data lines and can be latched in.

| Data Size | out.size<1> | out.size<0> |

|-----------|-------------|-------------|

| word      | 1           | 0           |

| halfword  | 0           | 1           |

| byte      | 0           | 0           |

Table 2.1: Data Size Line Encoding

Addresses are gated onto the pads during  $\phi_4$ , and the *address enable* line is asserted shortly after the trailing edge of  $\phi_4$ . The data on a read is latched in by the processor on  $\phi_3$ , while the data on a write is gated onto the pads beginning  $\phi_2$ , with the *data enable* signal asserted shortly after the trailing edge of  $\phi_2$ .

The address enable line rises on the falling edge of  $\phi_4$  and falls on the falling edge of  $\phi_1$ ; the memory must latch the address within that time (30 ns). It then has until the falling edge of data enable to gate the data onto the address/data lines; this will occur 50 ns after the falling edge of address enable (i.e., on the falling edge of  $\phi_3$ ). If the memory cannot respond in that time, it must signal a wait state. Data enable is asserted only on cycles that are not wait cycles, so if a wait state is signaled, the memory will then have one cycle plus 50 ns to respond. Note that the address enable line will not be reasserted during the wait cycle. In the case of a write, the data to be written will be gated onto the address/data lines during  $\phi_2$  regardless of whether the cycle is a wait cycle or not; however, the data enable line will not be asserted on a wait state, just as in a read. Once data enable is enabled, the memory will have 30 ns to latch the data in.

The short length of time allowed for the memory to raise the *wait* signal is a result of certain implementation constraints. Section 2.5 describes these constraints and presents a possible solution to this problem.

Figure 2.2: Memory Interface Timing

#### 2.3.3. Normal Instruction Cycle

Figure 2.3 shows the timing of the various blocks in the controller during a normal instruction cycle. The Mirror Processor has a pipelined instruction fetch/execution cycle: as one instruction is being executed, the next instruction is being fetched. The instruction fetch begins on  $\phi_4$ , when the address of the instruction to be fetched is gated onto *busOUT* and through the pads. If the memory cannot respond with the requested data that cycle, it raises the *wait* line, which the controller latches on  $\phi_2$ . If the wait line is high, the *state.wait* bit is set, and the processor does nothing except shift the DWBs (with valid bit = 0) until the next  $\phi_2$ , when the *wait* line is latched again. If the memory can respond, the incoming instruction is gated onto *busIN* and passed straight through onto *busIR* during  $\phi_3$ . As the opcode is arriving on *busIR*, the Next State Logic computes the next state, and its output is latched on the falling edge of  $\phi_3$ . While all this is happening during  $\phi_3$ , the  $\phi_4$  PLA begins precharging. It evaluates and latches its outputs on  $\phi_4$ , which is when the  $\phi_1$  PLA's precharge. These PLA's evaluate and latch their outputs on  $\phi_1$ . Meanwhile, the Memory Control Logic also evaluates on  $\phi_4$ , just in time generate the signals needed for the next instruction fetch. The Condition Code Logic PLA precharges  $\phi_2$  and evaluates  $\phi_3$ , in time for the condition bit to determine which address to gate out on  $\phi_4$  for conditional jumps. Note that every PLA evaluates every cycle, regardless of whether or not it is a wait cycle.

The sequence for a two-cycle instruction (load, store) is only slightly different. Because of the instruction fetch pipeline, the instruction following the load/store arrives on busIN during  $\phi_3$  of the first cycle of the load/store. However, it is not decoded until  $\phi_3$  of the second cycle, so it must be stored somewhere. At the same time, the opcode of the load/store is re-decoded during the first cycle, so it must remain on busIR across two cycles. Thus, during the first cycle of the load/store, the next instruction is latched into the IRlatch but is not gated onto busIR. During the second cycle, when busIN will have data during  $\phi_3$ , the IRlatch is not reloaded, but its value is gated onto busIR.

The instruction execution timing during  $\phi_4$  is constrained by certain implementation details and impacts greatly on the controller's critical path (Section 2.4.12). Section 2.5 describes possible

Figure 2.3: Control Timing

alterations to the Mirror Processor's design that could improve the critical path and also allow the memory a longer time to assert the *wait* signal.

#### 2.3.4. Interrupts and Traps

The interrupt logic monitors the external Interrupt Request (IRR), shutdown, and reset lines, as well as various lines from the data path indicating a trap condition. All are latched on  $\phi_2$ , at which time the internal interrupt signals are sent to the rest of the processor. If the interrupt or trap is taken, a hardwired calli instruction is gated onto busIN during  $\phi_3$  in place of whatever instruction would normally be gated on from the pads, and an interrupt vector corresponding to the type of interrupt or trap is gated onto busOUT during  $\phi_4$ . The instruction that is actually interrupted is allowed to finish, but an invalid bit is shifted into the register file DWB, effectively canceling the results of the instruction.

The handling of interrupts after this point is exactly the same as in RISC II; all of the caveats that apply to RISC II apply to the Mirror processor as well. For instance, the first instruction of every interrupt handler must be a **getlpc**, typically to r24, in order to save the address of the instruction being fetched during the execution of the interrupted instruction. In addition, all interrupt handlers must end with the following sequence:

jmpx alw,0(r25) reti alw,0(r24)

in order to restore the sequence of memory accesses prior to the interrupt. Finally, the interrupt handler must be careful to save its own state before re-enabling interrupts and make sure there are more free register windows before making a subroutine call [4].

There are, however, two cases where the interrupt sequence differs from the RISC II scheme. Two of the trap signals, "bad shift amount" and "address misalignment," cannot be generated by the data path before the end of  $\phi_2$ . In these cases, they are latched  $\phi_3$ , and the trap is taken in the following cycle. However, because the point at which the trap is taken is one cycle *after* the instruction that caused the trap, more needs to be done in order for the trap handler routine to determine the instruction that caused

the trap. So, in addition to latching the signals  $\phi_3$ , invalid bits are written into every DWB on  $\phi_4$ , when they load their valid bits. Thus, there will be no state change after the trap is detected, and the trap handler will be able to find the correct instruction.

Reset and shutdown are handled in exactly the same manner as other interrupts, except that they have higher priorities than any other type of interrupt or trap.

#### 2.3.5. Rollbacks

The rollback memory attached to *busIR* operates in exactly the same way as the Instruction Register in the data path [5]. It loads from *busIR* on  $\phi_4$  and updates on  $\phi_2$ . When a rollback occurs during  $\phi_3$ , the valid bits are cleared (set to 0), and the most recent valid entry is selected and gated onto *busIR* all on  $\phi_3$ .

#### 2.4. Details of Controller Implementation

This section presents detailed descriptions of each of the blocks in the controller except the rollback logic, which is described in Chapter 3.

## 2.4.1. busIR

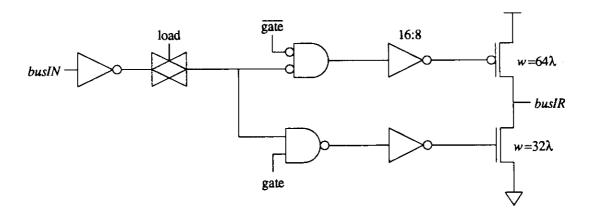

Immediate (IMM) bit, the condition field (four bits), and the five-bit destination register (Rd) field, four bits of which coincide with the condition field. All of the other blocks in the controller read off of this bus, which serves to buffer the controller from busIN during loads, stores, and state repairs. Loads and stores are two-cycle instructions; the opcode must remain available for two cycles because the PLA's decode the opcode every cycle, regardless of what else is going on that cycle (e.g., state repair, rollback, interrupt, etc.). In addition, the destination register for a load must be available during the second cycle for the incoming data. During a rollback, the value of busIR is restored by the controller's rollback memory. If a state repair takes place after a rollback, busIR keeps the instruction available while the data word being repaired is read in on busIN.

#### 2.4.2. busIR Latch and Driver

Normally, the interface between busIN and busIR acts as a transparent latch, while during loads and stores it holds the next instruction over one cycle as described in Section 2.3.3. The driver is similar in design to the busIN driver [5], with the addition of a latch between busIN and the driver; see Figure 2.4. SPICE runs show that it takes 8.0 ns to charge busIR from zero to one.

Figure 2.4: busIR Latch and Driver

# 2.4.3. Next State Logic

The state of the controller logic is determined by a four-state finite state machine, with each state representing the type of cycle that is currently executing. Most cycles are represented by the *normal* state, that is, a normal one-cycle instruction. The second cycle of a load or store instruction is represented by the *suspend* state, so called because the instruction fetch that would normally take place during that cycle is replaced by the load/store access instead, so the instruction fetch pipeline is temporarily suspended. The other two states represent the first and second state repair cycles (*repair1* and *repair2* respectively).

Although four states can be represented by two bits normally, three bits must be used in this case, one to distinguish between *normal* and *suspend* states (bit 0), and two more to indicate *repair1*, *repair2*, or no repair. The *normal/suspend* bit is saved each cycle in the controller's rollback memory and is restored on a rollback. If a state repair takes place after the rollback, the bit must be remembered across

both cycles of the repair since it will not be restored again after the repair, so it is carried along unchanged through both cycles. Bit 1 is set for *repair1*, while bit 2 is set for *repair2*; neither bit is set in the absence of state repair.

The next state is computed during  $\phi_3$  based on the current state, the repair signals set during  $\phi_2$ , and the opcode of the instruction being executed in the current cycle. In normal operation, the only time the state needs to change from *normal* to *suspend* is when the next cycle will be the second cycle of a load or store. Only one opcode bit (bit 5) is needed to distinguish between load/store instructions and all others, so the *suspend* state will be true only if the current state is *normal*, and bit 5 of the opcode that arrived in the previous  $\phi_3$  is set. Thus, opcode bit 5 (*op5*) is latched every  $\phi_4$  to be used in the following  $\phi_3$ . The actual next state computation is implemented in random static logic, with its outputs latched  $\phi_3$  and relatched  $\phi_2$  before being fed back around as inputs (see Figure 2.1). Note that the re-latching during  $\phi_2$  could just as easily have been done during  $\phi_1$  or  $\phi_4$ ; the phase in which to do the latching was chosen at random.

The *suspend* and *op5* bits are latched one more time during  $\phi_3$  before being sent to the Controller Rollback Memory (Section 2.4.11). Since the Rollback Memory is loaded during  $\phi_4$  and the next *op5* bit is also latched during  $\phi_4$ , this latch prevents the *op5* bit from being overwritten before is it written into the Rollback Memory. It was later noticed that the latch is not needed for the *suspend* bit, and in addition, it would not be needed for the *op5* bit if it were latched during  $\phi_1$  or  $\phi_2$  instead. However, there was insufficient time to make the necessary design modifications.

#### 2.4.4. PLA's

Most of the control signals used by the data path are generated by three domino logic PLA's. The  $\phi_4$  PLA, the smallest of the three, generates the signals that must be valid during  $\phi_1$ . It precharges during  $\phi_3$  and evaluates during  $\phi_4$ , thus requiring its inputs (including the three bits of next state) be stable before the rising edge of  $\phi_4$ . The  $\phi_{1a}$  and  $\phi_{1b}$  PLA's generate the signals that are used in the other phases.

Because there are a large number of such signals, they are divided up between two PLA's in order to avoid having a very large PLA with a long evaluation time. The two PLA's precharge during  $\phi_3$  and evaluate during  $\phi_1$ . Most of their outputs are also latched during  $\phi_1$ ; however, several of the  $\phi_{1b}$  PLA's outputs are not latched until  $\phi_2$  because their previous values are being used  $\phi_1$ . Specifically, the PSW update and the register file write both take place  $\phi_1$ , so signals pertaining to these blocks are delayed until  $\phi_2$ .

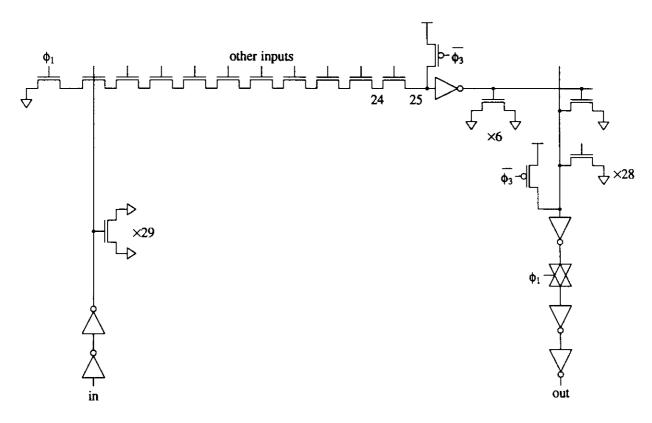

The PLA's were generated by feeding the output equations to *eqntott* [6] and then passing the output to *espresso* [6] with the "output phase optimization" option to minimize the number of product terms. *magic* layout was generated with *mpla* [6] using a template originating from Caltech but modified heavily. Figure 2.5 shows a "worst case" bit slice of the  $\phi_{1b}$  PLA. It combines the input with the largest gate load, the NAND term with the greatest number of series transistors, the NOR-plane input with the largest gate load, and the NOR term with the largest drain load. SPICE simulations of the worst cases of each PLA show evaluation times of 13.0 ns, 16.5 ns, and 18.5 ns for the  $\phi_4$ ,  $\phi_{1a}$ , and  $\phi_{1b}$  PLA's respectively. The setup time for the  $\phi_4$  PLA is 7 ns (*i.e.*, the input must be stable 7 ns prior to the rising edge of the evaluate clock, which is  $\phi_4$  in this case; see Section 2.4.12); the setup times for the  $\phi_1$  PLA's were not calculated because their inputs must already meet the  $\phi_4$  PLA setup time.

#### 2.4.5. Condition Code Logic

This block of logic takes as input the four condition code bits from the PSW and the four bits from the condition field in the instruction and produces as output one bit indicating whether or not the condition codes satisfy the indicated condition (in the case of a conditional branch). The output bit is AND'ed with some of the PLA outputs to produce signals required at the beginning of  $\phi_4$  (these signals determine which address is gated onto *busOUT* for the next instruction fetch), so the output of this block must be ready by the middle of  $\phi_3$ . As we have limited ourselves to static gates of no more than four inputs, a static NAND/NOR tree implementation of the logic would require five levels of large, four-input

Figure 2.5: PLA Bit Slice (\$\phi\_{1b}\$ PLA)

NAND and NOR gates, which would be slow and which would require a lot of area. However, all of the inputs can be ready by the end of  $\phi_2$ , so dynamic logic can be used instead. The logic has been implemented as a PLA with eight inputs, one output, and 18 product terms, generated in the same manner as the other two PLA's. The PLA precharges  $\phi_2$  while latching its inputs at the same time, and it evaluates and latches its outputs during  $\phi_3$ . SPICE runs show the output is ready 7.75 ns after the rising edge of  $\phi_3$ .

# 2.4.6. Post-FSM Logic and Valid Bit Logic

Some of the control signals used by the data path are dependent on the condition bit, the *rollback* signal, the *interrupt* signal, and the *wait* signal, all of which become valid long after the PLA's evaluate. In order to allow the PLA's to evaluate without waiting for them, these control signals are produced outside of the PLA's by the Post-FSM Logic and Valid Bit Logic blocks. The valid bits shifted into the DWBs each cycle are produced by the Valid Bit Logic block, while the rest of them are produced by the

Post-FSM Logic. In either case, every signal is produced by AND'ing the required condition bit(s) with the decoded opcode signals coming from the PLA's. Static random logic is used since the inputs arrive at different times.

## 2.4.7. Memory Control Logic

Five of the bits that control the memory access (read/write, instruction/data, data size (2 bits), address/data pad enable) must be valid as soon into  $\phi_4$  as possible, since the instruction fetch begins that phase. They cannot be included in the  $\phi_4$  PLA because that PLA requires most of  $\phi_4$  to evaluate, so instead they are generated by the random logic in the Memory Control Logic block. Both dynamic and static implementations were considered. It was found that because all of the inputs are ready before the end of  $\phi_3$ , the static version was faster than the dynamic version (the delay being only the delay through a latch, rather than the time to discharge the output line plus the delay through the latch), so the static version was used.

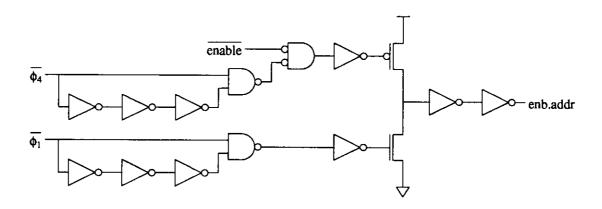

#### 2.4.8. Memory Enable Signals

The two memory enable bits, address enable and data enable, are also generated in the Memory Control Logic block. The memory interface scheme requires that the enable signals not go up until the address or data is stable on the address/data lines, so the enable signals cannot simply be tied to the rising edges of  $\phi_4$  and  $\phi_2$ ; they must be delayed until it is certain that the memory sees the proper address/data value on the lines. At the same time, the enable signal should rise as soon as possible after the address/data value is ready in order to give the memory as much time as possible to respond to the request. One way to do this would be to self-time the delay, i.e.,, use the worst case delay on busOUT to trigger the enable signal (assuming the delay through the pads is equivalent for all pads). However, none of the busOUT lines can be used to directly trigger the signal because it cannot be guaranteed that at least one of the lines will have a transition, so a delay circuit featuring an exact replica of one bit of busOUT must be designed in order to implement this scheme. This would take up far too much area in the

controller, so the self-timing approach was dropped.

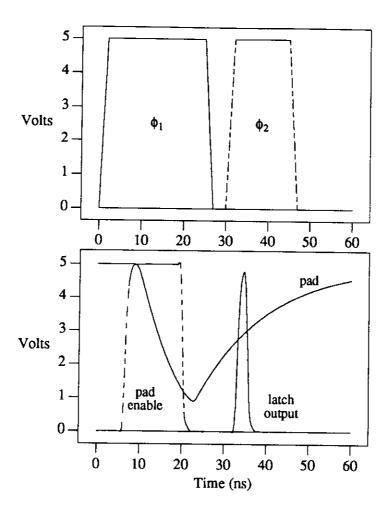

The current implementation has the address enable line being enabled from the falling edge of  $\phi_4$  to the falling edge of  $\phi_1$ . SPICE runs have shown that this gives an adequate delay, although it doesn't give the memory quite as much time to respond. The circuit diagram is shown in Figure 2.6. The falling edge detectors use delay inverters [5] (see Section 2.6) to delay the complement of the clock signal long enough to generate a pulse on the falling edge. The data enable circuit is similar, except that it is valid from the falling edge of  $\phi_2$  to the falling edge of  $\phi_3$ .

Figure 2.6: Memory Address Enable Bit

# 2.4.9. Interrupt Logic

This block, implemented in static random logic, takes all the various interrupt and trap condition signals and sets the internal interrupt bit, *state.int*. In the case of a reset or a shutdown, the internal reset or shutdown bit is set instead (*state.reset* and *state.shutdown* respectively). The Interrupt Logic also determines the interrupt vector to gate onto *busOUT*. Since all of the vectors differ only in three bits, only those three bits need to be generated and sent to the *busOUT* driver in the data path. A list of all possible interrupt and trap conditions and their respective interrupt vectors is shown in Table 2.2. It should be noted that the interrupt vectors shown differ from the RISC II vectors in that they are placed in the lower half of the memory space (locations 0x0 to 0x40), while in RISC II they were placed in the upper half (0x800000000 to 0x80000030). This was done in order to simplify the logic gating the interrupt

vector onto busOUT. It should also be noted that only reset and shutdown traps are non-maskable; all others can be masked out by the interrupt enable bit from the PSW.

| Cause                          | Vector     |

|--------------------------------|------------|

| Reset Pin pulled               |            |

| illegal opcode                 |            |

| privileged opcode              | 0x00000000 |

| address misalignment           | <u> </u>   |

| illegal shift amount           |            |

| Interrupt Request Pin pulled   | 0x00000010 |

| Register File window overflow  | 0x00000020 |

| Register File window underflow | 0x00000030 |

| Shutdown Pin pulled            | 0x00000040 |

Table 2.2: Interrupt Vectors

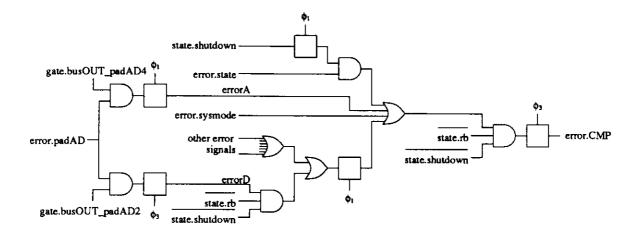

# 2.4.10. Comparator Logic

Each output pad has associated with it a small amount of comparison logic. When the processor is operating in *slave* mode, each output signal value is compared with the value present on the pad (which is the value written by the master), and if they differ, an error signal corresponding to that pad is set. Most of the comparison error signals are routed directly to the Comparator Logic block (Figure 2.7 and Table 2.3), where they are OR'ed together to create a global comparison error signal (*error.CMP*). The exceptions are the multi-bit vectors: data size (2 bits), state compression (4 bits), and address/data pads (33 bits). In each case, the error signals from the individual pads are first OR'ed together at the pads, and only a single error signal representing the entire vector is sent to the Comparator Logic block (except for the address/data lines, where three signals are sent; see below). A more detailed description of the comparison logic at the pads is presented in [5].

Because of the large number of address/data pad error signals, there was not enough room at the pads to OR all of them together into a single error signal. Instead, they are OR'ed down to three signals (one representing bits 0 to 15, one representing bits 16 to 32, and the error signal from the parity bit pad) which are then sent to the Comparator Logic block. The three signals are OR'ed together here into the

Figure 2.7: Comparator Logic Block

| Error Signal   | Signal(s) Being Compared     |

|----------------|------------------------------|

| error.AD       | address                      |

| error.enb.addr | address enable bit           |

| error.enb.data | data enable bit              |

| error.id       | instruction                  |

| error.ira      | interrupt acknowledge signal |

| error.rw       | read                         |

| error.size     | data size                    |

| error.state    | state compression bits       |

| error.sysmode  | system mode bit              |

| error.busA     | busA parity error            |

| error.busB     | busB parity error            |

| error.busOUT   | busOUT parity error          |

Table 2.3: Comparison Logic Error Signals

final error signal (error.padAD).

Most of the error signals are OR'ed together in a static OR tree and latched  $\phi_1$ . After the internal rollback and shutdown lines have been set during  $\phi_2$ , the comparison error signal is AND'ed with them and latched again on  $\phi_3$ , after which it is sent directly to the Rollback Logic (Chapter 3). The state compression and system mode bit error signals cannot be ready by the end of  $\phi_1$ , so they are OR'ed in with the  $\phi_1$  error signal after the  $\phi_1$  latch. In addition, because the state compression errors are ignored during shutdowns, the state compression error bit (*error.state*) needs to be AND'ed with *state.shutdown*. However, because *state.shutdown* changes during  $\phi_2$ , and *error.state* does not become valid until

sometime into  $\phi_2$ , state.shutdown needs to be saved. save.shutdown saves state.shutdown during  $\phi_1$  and is then AND'ed with error.state when it arrives. Finally, because the address/data lines are used twice per cycle, the error signal from those lines (error.padAD) is latched during both  $\phi_1$  and  $\phi_3$  (for address and data errors, respectively), conditioned on whether or not a value is being gated out during that phase. gate.busOUT\_padAD4 is asserted during  $\phi_4$  and  $\phi_1$  when an address is being gated out, and gate.busOUT padAD2 is asserted during  $\phi_2$  and  $\phi_3$  when data is being stored.

In addition to detecting comparison errors on external signals, the Comparison Logic block also sets the error signals for parity errors on busA, busB, and busOUT. The parity bits read out of the register file are sent to the Comparison Logic block along with the new parity bits generated by the data path after the register read and compared. They are XOR'ed together, and the appropriate error signal is set if they differ. The parity bit calculated for busOUT during the second cycle of a state repair is XOR'ed with the newly-calculated parity bit of the value read from the register file the previous cycle; the busOUT error flag is set if the bits are different. Section 3.2.4 describes the busOUT parity error in more detail.

#### 2.4.11. Controller Rollback Memory

The fourteen bits of busIR, plus the normal/suspend bit and opcode bit 5 of the previous cycle, are saved in a DWB each cycle and restored on a rollback. The controller DWB behaves in exactly the same way as the IR, loading on  $\phi_4$  and updating on  $\phi_2$ .

During normal one-cycle instructions, the controller DWB contains the same information as the IR except for the state bit, since busIR is loaded directly from busIN. Thus, in those cases the controller DWB is completely redundant and not needed. However, during the first cycle of a load or store instruction, busIR and busIN will have different values: busIR will hold the load/store instruction across to the second cycle, while the next instruction arrives on busIN. When rolling back to that second cycle, both the load/store instruction and the next instruction need to be restored. In this case, the controller DWB is needed to restore the load/store instruction while the IR restores the next instruction.

#### 2.4.12. Critical Paths

The main critical path for the controller occurs during  $\phi_3$ , when the instruction arrives on buslN. Because the PLA's are dynamic, the inputs cannot change during the evaluate phase. In the case of the  $\phi_4$  PLA, it evaluates during  $\phi_4$ , so its inputs cannot change after the rising edge of  $\phi_4$ . In addition, there is a setup time associated with the inputs, such that if an input changes after the minimum setup time, the PLA may not function properly. For the PLA's used in the Mirror Processor, the worst-case scenario happens if the input closest to the precharge transistor in the AND plane changes to 1 after the precharge clock has been de-asserted. If the node on the other side of the AND plane transistor for this input (node 24 in Figure 2.5) was set to 0 in the previous cycle, and all the other inputs are 0, then the precharged node (node 25 in Figure 2.5) may incorrectly discharge. Thus, the minimum setup time is the latest time prior to the rise of the evaluate clock that the input can change without causing the precharged node to discharge. For the  $\phi_4$  PLA, the input must be stable at most 23 ns into  $\phi_3$ . This results in the following critical path: the instruction arriving on the address/data pads during  $\phi_3$  must go from the pads to buslN to buslR to the  $\phi_4$  PLA and be stable by 23 ns into  $\phi_3$ .

The critical path during  $\phi_4$  is set by the evaluation time of the  $\phi_4$  PLA, while the time required to perform rollback amount arbitration sets the constraints for  $\phi_1$  and  $\phi_2$  (see Section 3.3.17).

Another critical path during  $\phi_2$  resulted in the removal of the conditional return instructions. Because the PSW updates its condition codes during  $\phi_1$  and the interrupt logic sets *state.int* during  $\phi_2$ , it would be necessary to evaluate the condition bit, increment the Current Window Pointer in the PSW, detect a register window overflow, and cause a trap all within  $\phi_2$ . Since this was clearly not possible given a 15 ns  $\phi_2$ , it was decided to make returns unconditional. Thus, the window pointer could be incremented without waiting for the condition bit to be evaluated, and an overflow condition could be detected much sooner in  $\phi_2$ . In addition, the evaluation of the condition bit could be moved to  $\phi_3$ , thereby allowing it to be implemented as a dynamic PLA.

#### 2.5. Alternate Wait State Timing

Because the memory is not given very much to time to assert the *wait* signal, it would be preferable to latch the *wait* line one phase later, during  $\phi_3$ . However, this is not possible with the current controller implementation. Because the PLA's evaluate every cycle regardless of whether or not it is a wait cycle (Section 2.3.3), *busIR* must not be reloaded during  $\phi_3$  of a wait cycle; otherwise, the PLA's will receive garbage input. Since it is necessary to know whether or not the current cycle is a wait cycle before  $\phi_3$ , the wait line must be latched during  $\phi_2$ .

One possible way to allow the *wait* line to be latched during  $\phi_3$  would be to load *busIR* regardless of the value of the *wait* line and then disable the latching of the PLA, Memory Logic, and Condition Code Logic outputs during a wait cycle. The outputs would then remain the same as in the previous cycle, as in the case of the current implementation. In addition, the Register File Translator in the data path [5] would have to disable the latching of the destination register number off of *busIN* during a wait cycle. Since nothing else is dependent on the *wait* signal being set during  $\phi_3$ , the latching the signal can be delayed until then.

Another way to allow latching of the wait signal during  $\phi_3$  would be to eliminate the need to use busIR during  $\phi_4$ . Then, the loading of busIR could be delayed until  $\phi_4$ , allowing the wait signal to be latched during  $\phi_3$ . However, the modifications to the controller design to allow this would be more than trivial.

First, there are two blocks that read the opcode of the instruction that arrives during  $\phi_3$  off of busIR during  $\phi_4$ : the  $\phi_4$  PLA and the Memory Control Logic. Under normal operation, the Memory Control Logic outputs the same values every cycle except during the second cycle of a load or store instruction. Thus, the only time the opcode is important in the Memory Control Logic is during the second cycle of a load or store, during which time busIR is not re-loaded anyway.

Of the twelve  $\phi_4$  PLA outputs, ten of them are dependent on the opcode of the just-arrived instruction. One of them (gate.busOUT\_padAD2) differs only during the second cycle of a store, so the

arguments for the Memory Control Logic signals apply to this signal as well. The remaining nine signals are needed by the data path at or near the beginning of  $\phi_1$ . If they were to be implemented in static random logic, the opcode inputs would not need to be ready until the time the signals need to be ready minus the evaluation time. Since the signals are not needed at *exactly* the beginning of  $\phi_1$ , the evaluation time can be pushed into  $\phi_1$ . If the evaluation time is made short enough and pushed far enough into  $\phi_1$ , the loading of *busIR* can be delayed until after the *wait* line has been latched in  $\phi_3$ . In order to minimize the evaluation time, the opcode decoding must use as few gates as possible. Of the nine signals that need to be generated, six of them control the inputs to the shifter, requiring that the logic detect an ALU instruction, a shift instruction, or a ldhi instruction. Two of the other three signals control the window pointer in the PSW, requiring the detection of calls and returns, and the last signal controls the selection of either the PC or LSTPC (see [5] for full descriptions of these blocks), requiring the detection of the getlpc instruction. Because of the great number of instructions that need to be detected, it would probably require more than "a few" gates to implement all the signals; however, the evaluation time could probably still be shortened enough to allow the loading of *busIR* during  $\phi_4$ .

Although the second scheme would involve much more work to achieve, another benefit would be to remove *busIR* loading from the controller's critical path during  $\phi_3$  (Section 2.4.12). It would, however, probably increase the critical path in  $\phi_4$ , as the logic would not be given very much time to evaluate.

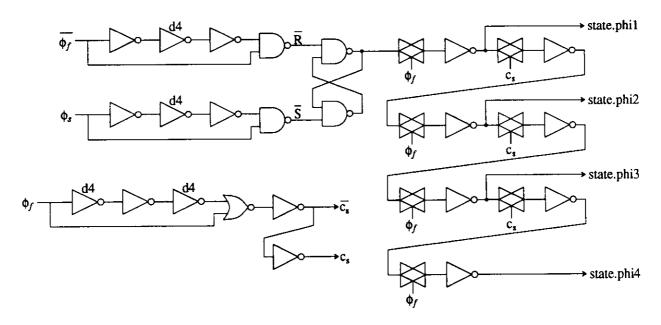

#### 2.6. Clock Generation

The Clock Generator block generates the four clock phase signals used by the rest of the processor. The block can generate all four signals from an external master clock signal, or all four signals can be supplied externally, in which case the Clock Generator block passes them straight through. A single clock mode bit (in.csel) determines which mode the Clock Generator will operate in.

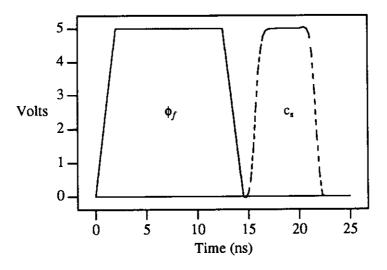

When operating in on-chip generation mode, the Clock Generator takes two inputs: a fast  $clock(\phi_f)$ , which has a cycle time of 25 ns and is used to generate each phase signal, and a slow

clock  $(\phi_s)$ , which has a cycle time of 100 ns and is used to indicate the start of  $\phi_1$ . Both clocks are guaranteed to have a 50% duty cycle, and the rising edge of the slow clock is guaranteed to occur a setup time before the rising edge of the fast clock (although the falling edge of  $\phi_s$  is *not* guaranteed to occur before the rising edge of  $\phi_f$ ). Each clock is fed into an edge detector whose outputs serve as inputs to an SR flip-flop. The flip-flop is set on the rising edge of  $\phi_s$  and is cleared on the the falling edge of  $\phi_f$ . The output of the flip-flop is then sent into a four-stage shift register, where each stage represents one of  $\phi_1$  through  $\phi_4$ . The shift register is clocked by  $\phi_f$ ; since the output of the flip-flop is set to 1 only during one cycle of  $\phi_f$  per cycle of  $\phi_s$ , the first stage of the shift register will be loaded with a 1 only every fourth cycle. Thus, on each successive cycle of  $\phi_f$ , only one stage of the shift register will have a 1, and the stage with the 1 drives the signal for that particular phase.

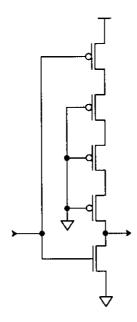

Figure 2.8: Clock Generator

Figure 2.8 shows the edge detectors, flip-flop, and shift register. Each stage in the shift register is composed of a master-slave flip flop. The master stage is clocked by  $\phi_f$ ; the slave stage is clocked by a signal generated from  $\phi_f$  ( $c_s$ ). Figure 2.8 also shows the logic that generates two non-overlapping clocks from a single clock. In the figure, inverters marked with a d are delay inverters [5]; the number following the d indicates the number of series P-transistors. A "d4" delay inverter is shown in Figure 2.9. Timing

Figure 2.9: d4 Delay Inverter

diagrams for the slave clock and the shift register output are shown in Figures 2.10 and 2.11.

Figure 2.10: Slave Clock Generation Timing

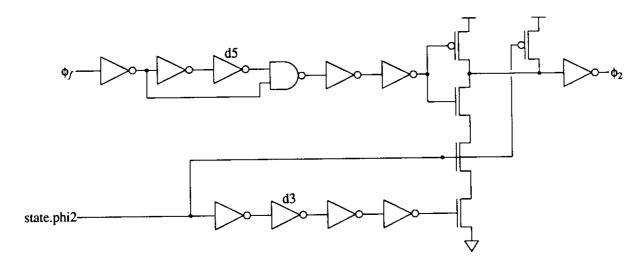

Because  $\phi_f$  has a 25 ns cycle time, each shift register stage will hold its value for exactly 25 ns. Since both  $\phi_1$  and  $\phi_3$  are high for 25 ns, the output of the  $\phi_1$  and  $\phi_3$  shift register stages can be sent directly to the clock drivers. However, both  $\phi_2$  and  $\phi_4$  are high for only 15 ns, and they must each rise 5 ns after the falling edge of the previous phase, so the shift register stage outputs cannot be used directly. Figure 2.12 shows how  $\phi_2$  is generated;  $\phi_4$  is generated in the same way. The shift register stage output

Figure 2.11: Clock Generation Timing

(state.phi2) is AND'ed with  $\phi_f$ ; however, the rising edge of state.phi2 is delayed 4 ns, and the falling edge of  $\phi_f$  is delayed 6.5 ns to create a signal that rises 5 ns after the rise of  $\phi_f$  (there is a 1 ns propagation delay) and falls 15 ns later. Because the falling edge of state.phi2 is also delayed 4 ns while the rising edge of  $\phi_f$  is not, a straightforward AND'ing of the delayed signals would result in a spike at the output at the beginning of the next  $\phi_f$  cycle. In order to prevent this from happening, the last NAND gate is modified slightly to include the non-delayed state.phi2 as well. Thus, the  $\phi_2$  output will be high only when state.phi2 and the delayed state.phi2 are high, along with the delayed  $\phi_f$ . A timing diagram of the  $\phi_2$  clock generation is shown in Figure 2.13.

Figure 2.12:  $\phi_2$  Generation

Figure 2.13:  $\phi_2$  Clock Generation Timing

#### 3. ERROR DETECTION AND RECOVERY

The Mirror Processor includes two types of error detection: parity checking of the register file and input bus, and comparison of output pins. Error recovery is accomplished by micro rollback and state repair. This chapter details the timing of the error detection and recovery schemes, as well as the implementation of the rollback control logic. The implementation of the error detection schemes is detailed in [5].

## 3.1. Rollback Timing

#### 3.1.1. Internal Rollback

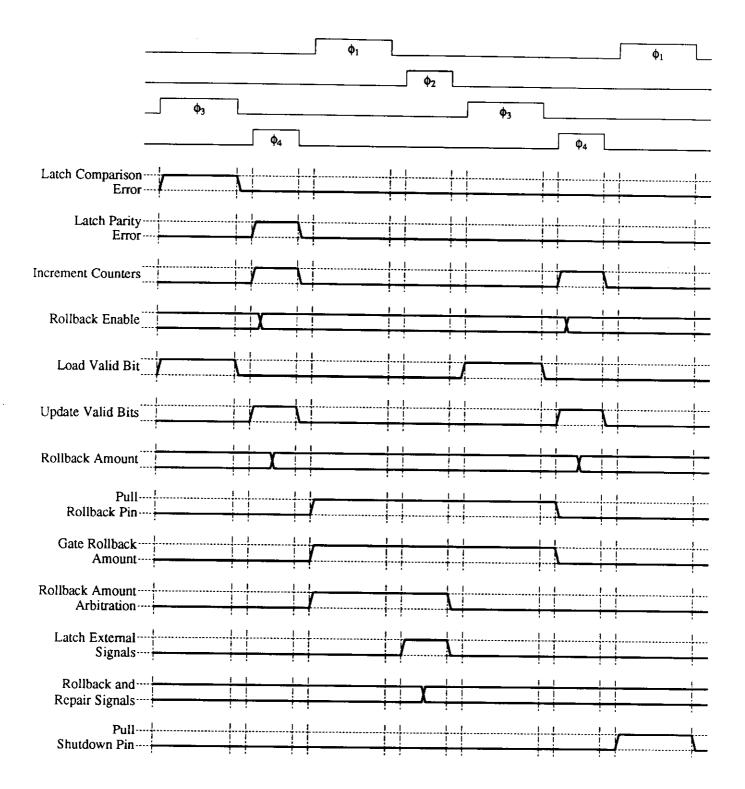

The internal comparison and parity error signals are latched by the Rollback Logic on  $\phi_3$  and  $\phi_4$  respectively. If any error condition is true, the external *rollback* line is pulled on  $\phi_1$ , and the proper rollback amount is sent out at the same time. The *rollback* and *rollback amount* lines are held until  $\phi_4$ .

#### 3.1.2. External Rollback

The rollback logic monitors the external *rollback* and *rollback amount* lines and latches them on  $\phi_2$ . If the *rollback* line is pulled, the internal rollback signal (*state.rb*) is set and sent to the rest of the processor. On  $\phi_3$ , all the DWBs invalidate the indicated number of valid bits, and in the case of the controller, *busIR* is restored from its DWB. If the rollback amount is greater than four, then the external *shutdown* signal is pulled on  $\phi_1$ . Note that because the rollback amount is latched at the end of  $\phi_2$ , any rollback amount arbitration must be completed before then.

## 3.1.3. Absolute and Relative Rollbacks

In most cases, rollbacks will be absolute. An absolute rollback of n cycles means that the processor will roll back exactly n cycles, regardless of whether any of those cycles are valid or not (see Section 3.3.8). Occasionally, a relative rollback will be required. A relative rollback of n cycles results in rolling back the n most recent valid cycles. The number of cycles actually rolled back will depend on

the number of invalid cycles in the recent past.

### 3.2. Error Detection Timing

## 3.2.1. Register File Parity Errors

The values of *busA* and *busB* are parity checked when they are read out of the register file during  $\phi_1$ . The error signal is latched by the rollback logic on  $\phi_4$ , and in the following cycle a rollback of one cycle takes place. State repair is then initiated (Section 3.4).

#### 3.2.2. busIN Parity Error

A value arrives on busIN during  $\phi_3$  of every cycle except a wait, and its value is parity checked on the following  $\phi_1$ . The error signal is latched the following  $\phi_3$ , after which a rollback of two cycles is signaled. No state repair is needed.

## 3.2.3. Comparison Errors

The comparison error signal is latched each  $\phi_3$  by the Comparator Logic (Section 2.4.10). If an error is indicated, a rollback of two cycles will be signaled. Again, no state repair is needed.

#### 3.2.4. busOUT Parity Error

Normally, the value on busOUT is checked by the output pad comparison logic. However, during state repair, the comparison is disabled because each processor will have a different value on busOUT (the one doing the restoring will have the value to be restored, while the other one will have whatever value was left there from the previous cycle). Because the value being restored is left on busOUT between the first and second repair cycles, any errors occurring to that value will not be caught by the normal comparison mechanism. Thus, the parity bit that is generated for busOUT is compared against the parity bit of the value that was read out of the register file during the first repair cycle, and an error signal is latched  $\phi_3$  if a mismatch occurs, followed by a rollback of one cycle to restart the state repair.

## 3.2.5. Multiple Rollbacks

There are several situations in which errors occurring during a rollback will cause further rollbacks. How multiple rollbacks are handled is dependent on the number of previous rollbacks and, to a certain extent, on the type of error that caused the most recent rollback.

If a rollback occurs and an erroneous value is restored from a rollback memory, that value will be detected either one or two cycles after the rollback (two cycles in the case of the PC, since it doesn't get put on the output pads until one cycle after the rollback; two cycles in the case of the controller if the flipped bit(s) is in the destination register field, since its state compression is not exported until the cycle after the rollback; one cycle in all other cases). In either case, the normal two-cycle rollback that would occur due to a comparison error will not invalidate the DWB entry with the bad value. In order to recover in this situation, it is necessary to roll back to the cycle before the one that was rolled back to previously, thus requiring a relative rollback [5] of two or three cycles (i.e., canceling the two or three most recent valid cycles [see Section 3.3.8]). The rollback logic has associated with it a counter that keeps track of the number of cycles since the last rollback; if an error is indicated within two cycles of a previous rollback and the normal amount to rollback is the same as the counter value (i.e., the rollback will be to the same cycle that was rolled back to before), then it is assumed that the error was due to a faulty rollback memory value, and a relative rollback to the cycle before the erroneous one is performed instead. Note that if the second rollback is caused by a parity error, the relative rollback one cycle more will result in the wrong register being repaired, since it is the instruction rolled back to that is used to determine which register to repair. However, this will do no harm, since the correct value will be copied from one processor to another.

It may be the case, however, that the proper cycle to roll back to is greater than four cycles previous to the current one. Since it it impossible to roll back more than four cycles, the rollback amount will be capped at four cycles, thus effectively causing a rollback to the cycle rolled back to before. In this scenario, because the offending instruction is never invalidated, it will repeatedly cause comparison errors

and rollbacks. Since there is no way to recover from this situation, it is necessary to detect when repeated rollbacks are occurring. The rollback logic has another counter that keeps track of the number of rollbacks that have occurred and which is cleared every 16 cycles. If four rollbacks occur within 16 cycles, it is assumed that the processor is stuck in an infinite rollback loop, and a shutdown is signaled.

Another problem occurs if it happens that the repeated rollbacks are caused by an erroneous value in the PSW rollback memory. When a shutdown trap is taken, all the other DWBs are loaded with fixed values associated with the calli instruction or are not read from. The IR and the controller DWB are loaded with the calli instruction, and the PC and MAR are loaded with the address of the shutdown handler. The SDR is not read from during the shutdown trap, and the next access to the SDR will be a write since the only time the SDR is read from is during the second cycle of a load or store, which will not happen again until after it is loaded during the first cycle of the next load or store. The PSW, on the other hand, only changes the Interrupt Enable and System Mode bits while keeping the previous values of the other fields. If one of those other fields is the one that caused the repeated rollbacks, it will still be incorrect after the shutdown, causing even more rollbacks. To correct this situation, all error checking is disabled for three cycles following a shutdown, enough time for the shutdown handling routine to save the PSW and store in a known good value.

Error checking is also disabled for three cycles after a reset in order to prevent random values on the error signals from causing an unwanted rollback.

If, on a register read, both processors detect a parity error in the same register, then it will not be possible to do a state repair, since neither processor has the correct value. However, to allow for the possibility that one of the processors actually has the correct value and that a second transient fault may have caused it to erroneously report an error (e.g., bit flip on busA itself and not the register, flipped parity error signal, flipped repair signal), no state repair will follow the one-cycle rollback. Thus, the instruction reading the registers with corrupted values will be executed again, and if the transient fault case were true, then only one processor will signal a parity error the second time through. However, if

both processors really do have bad values in the same register, then they will both signal a parity error on the same bus again. This will again cause a one-cycle rollback without state repair, and so on until the fourth rollback, after which a shutdown will occur.

## 3.3. Rollback Control Logic and Timing

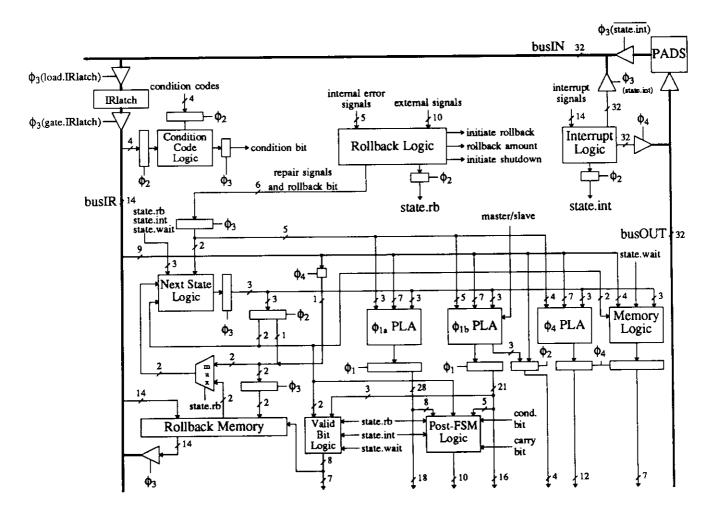

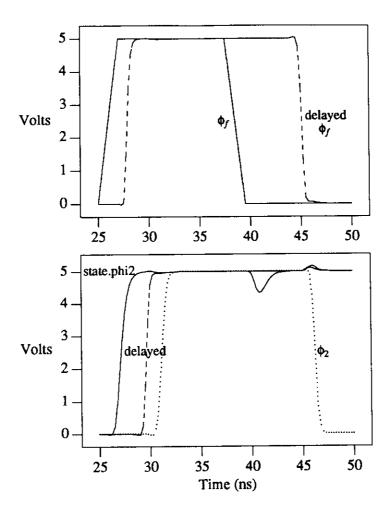

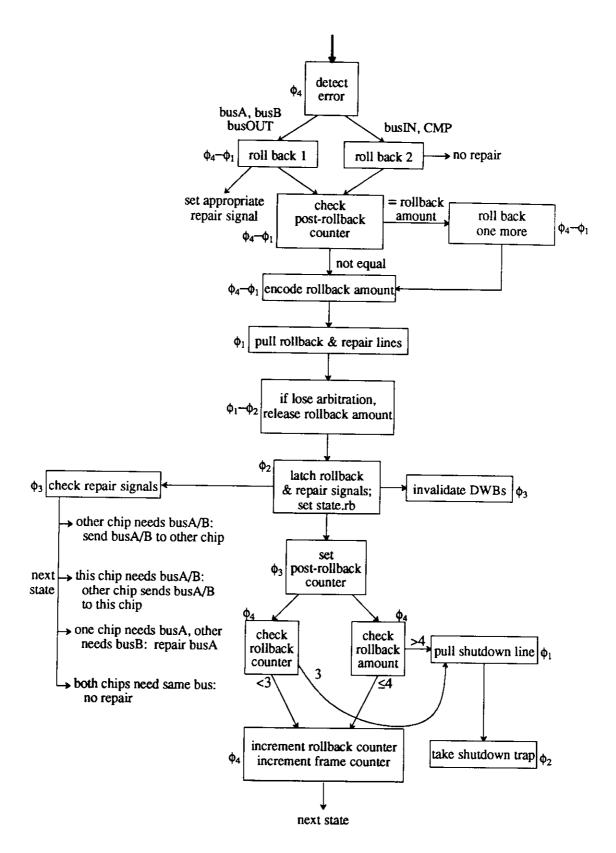

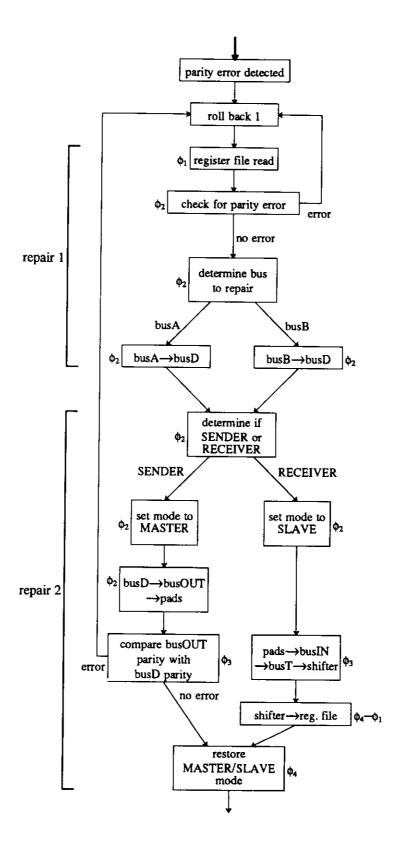

This section presents a detailed description of the Rollback Logic in the controller, as well as detailed timing of the rollback procedure. A block diagram of the Rollback Logic is shown in Figure 3.1.

Figure 3.1: Rollback Control

#### 3.3.1. Overview

The Rollback Logic consists of two parts. The first part monitors the the error signals generated by the parity checkers and comparators and pulls the external *rollback* line if an error is detected. It also determines the amount to roll back and recognizes shutdown conditions. The other part monitors the external *rollback*, *rollback amount*, and repair lines and sets the internal rollback signal (*state.rb*). Each part operates independently of each other, with the second part signaling a rollback to the whole system

and the first part reacting to the fact that something in the system has signaled a rollback.

## 3.3.2. External Rollback Signals

There are eight external rollback signals shared by all the modules in the system. The rollback line is asserted to tell the system that a rollback is going to occur. Whenever the rollback line is asserted, every module in the system must initiate a rollback in the current cycle. The amount to roll back is given on the rollback amount lines and is represented as a three-bit binary number. The four repair lines indicate which bus (busA or busB) on which processor needs to repaired in the event of a parity error. For a particular bus, the processor that detected the error asserts its out.repairX line, where X is either A or B for busA or busB respectively, which is then demultiplexed to assert either the repairXm or repairXs signal, where m and s correspond to master and slave respectively. Each processor reads in all four signals directly and can thus determine if it needs to be repaired or if it needs to repair the other processor.

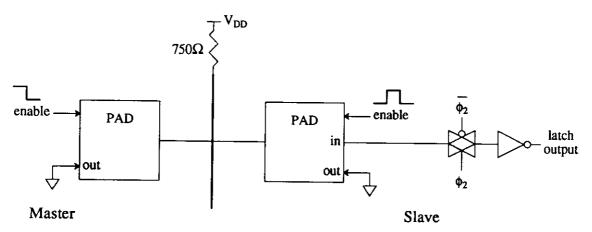

All of the external rollback signals are active-low wired-NOR lines held at one by  $750\Omega$  pullup resistors. The *out* line of each pad is connected to ground; when any module in the system wants to assert a signal, it raises that pad's enable line, thus forcing a zero onto the line. The  $750\Omega$  value was chosen to give a slightly faster fall time than rise time (the higher the resistance, the faster the fall time and the slower the rise time) but to have a reasonably fast rise time nonetheless.

#### 3.3.3. Input Latches

The eight external rollback signals are latched during  $\phi_2$ . state.rb is set if the rollback line has been pulled and the reset and shutdown lines haven't (they have precedence over rollbacks). The latch outputs are sent directly to the rest of the data path and controller.

#### 3.3.4. Internal Error Signals

The busA and busB parity error signals are latched during  $\phi_4$ , while the signals indicating busIN

parity errors, busOUT parity errors, and output pad comparison errors are latched by the controller's Comparator block during  $\phi_3$ . All five signals are sent directly to the Internal Rollback block (Section 3.3.7). In addition, the latched busA and busB parity error signals are sent to the output pads to become the external repair signals (out.repairA and out.repairB respectively; see Section 3.3.2).

#### 3.3.5. Post-rollback Counter

This two-bit counter keeps track of the number of cycles since the last rollback. It is set to 1 during a rollback cycle and increments by one each subsequent cycle until it rolls over to zero, after which it stays at zero. If the Internal Rollback Logic (Section 3.3.7) detects an error when the counter is non-zero, and the normal absolute rollback amount for that type of error is the same as the counter value minus one, then a relative rollback is signaled instead (see Section 3.1.3).

## 3.3.6. Rollback Enable Bit and Counter

When a reset or shutdown occurs, internal parity and comparison errors should be ignored for a few cycles afterwards (see Section 3.2.5). The three-bit Rollback Enable Counter is set to four when a reset or shutdown trap is taken and decrements by one each subsequent cycle until it reaches zero, after which it remains at zero. Whenever the counter is greater than zero, the Rollback Enable Bit is cleared. When the Rollback Enable Bit is cleared, internal rollbacks are disabled.

Both the Rollback Enable Counter and the Post-rollback Counter are implemented in a domino logic PLA similar to the ones used elsewhere in the controller. The inputs are latched during  $\phi_2$  at the same the PLA is precharging, and the outputs are evaluated and latched during  $\phi_3$ .

#### 3.3.7. Internal Rollback Logic

This block of static random logic determines if the next cycle is going to be a rollback cycle and, if so, the number of cycles to roll back. The block evaluates when any of the internal error signals change, and if the signals indicate a rollback is to occur, the external rollback line is pulled beginning  $\phi_1$ . The

amount to rollback is determined by the type of error (one cycle for busA/busB parity errors, two cycles for other errors) and the value of the Post-rollback Counter (Section 3.3.5). The amount is signaled on one of four lines, indicating "roll back 1," "roll back 2," "roll back relative 2," or "roll back relative 3." The first two (indicating absolute rollbacks) are sent directly to the Rollback Amount Encoder (Section 3.3.10), while the other two latter two (indicating relative rollbacks) are sent to the Selection Logic (Section 3.3.9) for translation into an absolute rollback amount. All four lines are mutually exclusive, so that it is not possible to signal more than one rollback amount.

### 3.3.8. Valid Bits

A set of valid bits like those used in the DWBs is used to keep track of which cycles are valid when performing a relative rollback. It is a four-bit shift register, updated each cycle, where each bit represents one of the past four cycles. When a rollback is performed, each cycle that is rolled back across has its corresponding bit set to zero. See [5] for implementation details. The first stage of each cell is loaded during  $\phi_3$ , and the second stage is updated during  $\phi_4$ . Invalidation takes place during  $\phi_3$  of a rollback cycle.

A valid cycle is one in which its corresponding valid bit here is set to 1. This will include any cycle that wasn't a rollback cycle, repair cycle, or wait cycle, and any cycle that wasn't invalidated by a previous rollback.

#### 3.3.9. Selection Logic

The Selection Logic translates a relative rollback amount into an absolute rollback amount, using the valid bits to select the second or third most recent valid instruction. It is the same as the three-level selection logic in the PC[5], except that the logic to select the most recent valid cycle has been removed. The logic will select the second or third cycle depending on whether a 1 comes in on the "roll back relative 2" line or the "roll back relative 3" line (they are supposed to be mutually exclusive; there should never be a case where both lines carry a 1) and will output a 1 on one of six lines corresponding to

cycles 2 through 7. The logic is purely static, so the proper line will be set shortly after either the selection lines change or the valid bits shift, both of which happen in  $\phi_4$ .

## 3.3.10. Rollback Amount Encoder

This block of static random logic, labeled "Encode" in Figure 3.1, encodes the eight rollback amount lines, two from the Internal Rollback block ("roll back one," "roll back two") and six from the Selection Logic, into a three-bit binary number representing the actual rollback amount. If the Selection Logic gives a value greater than four, it is encoded as four (i.e., the processor will never cause a rollback greater than four cycles).

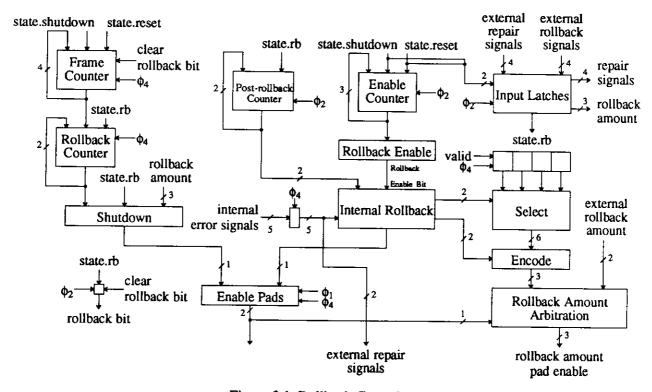

#### 3.3.11. Rollback Amount Arbitration

It is possible that more than one module in the system will signal a rollback in a given cycle. If this is the case, and the two modules gate different rollback amounts onto the *rollback amount* lines, the greater amount should be the taken. Each module requesting a rollback needs to decide if it is requesting the greatest amount and, if not, remove its value from the *rollback amount* line.

The procedure used by the Mirror Processor is a straightforward implementation of the Futurebus arbitration protocol [9]. The rollback amount being gated onto the external rollback amount lines by the processor is compared bit by bit with the amount read in from the same lines, starting with the most significant bit. To begin with, every bit is enabled and gates its value out on line. If any bit gates out a 0 and reads in a 1, it knows some other module is gating out a greater value starting with that bit position, so it disables all the lower significant bits. Once a bit is disabled, it stops gating its value on the line. If the bit gating a 0 out reads a 0 in, then it re-enables the lower bits. Note that the most significant bit is never disabled.

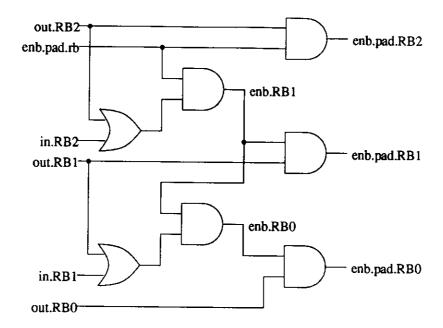

Figure 3.2 shows the implementation of the arbitration logic. In the figure, the *out.RBx* lines are the rollback amount lines output by the selection logic, while the *in.RBx* lines are the external rollback amount lines (in this figure, they are assumed to be active high). The *enb.pad.RBx* lines are the actual

Figure 3.2: Rollback Amount Arbitration Logic