#### Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

FLAG: AN FP BASED VLSI LAYOUT GENERATOR

Winthrop John Wu

May 1989 CSD-890023

# FLAG: An FP Based VLSI Layout Generator

Winthrop John Wu

May 1, 1989

# Contents

| 1 | Intr | oduction                                                       | 1  |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Problem                                                        | 1  |

|   | 1.2  | Approach                                                       | 2  |

|   | 1.3  | Circuit Description                                            | 3  |

|   | 1.4  | Symbolic Interpretation                                        | 5  |

|   |      | 1.4.1 Defining the Corresponding Structure of an FP Expression | 6  |

|   |      | 1.4.2 Intermediate Form Generation                             | 9  |

|   | 1.5  | Physical Layout and Circuit Simulation                         | 13 |

|   |      | 1.5.1 Symbolic, Virtual-Grid Layout                            | 14 |

|   |      | 1.5.2 Layout Verification                                      | 15 |

|   | 1.6  | Previous Work                                                  | 16 |

|   | 1.7  | Objective                                                      | 17 |

| 2 | Des  | ign Environment                                                | 18 |

|   | 2.1  | Conventional Design Cycle                                      | 18 |

|   | 2.2  | Limitations                                                    | 20 |

|   | 2.3  | Advantages                                                     | 21 |

|   | 2.4  | FLAG Design Cycle                                              | 21 |

|   | 2.5  | Limitations                                                    | 22 |

|   | 2.6  | Advantages                                                     | 23 |

|   | 2.7  | An Example                                                     | 23 |

|   |      | 2.7.1 Typical Design Cycle                                     | 24 |

|   |      | 2.7.2 FLAG Design Cycle                                        | 24 |

|   |      | 2.7.3 Discussion                                               | 27 |

| 3  | Des | ign and  | l Evaluation Experiments               | <b>3</b> 0 |

|----|-----|----------|----------------------------------------|------------|

|    | 3.1 | Simple   | Combinational Circuits                 | <b>3</b> 0 |

|    |     | 3.1.1    | Exclusive-Or                           | 31         |

|    |     | 3.1.2    | AND-OR Networks                        | 36         |

|    |     | 3.1.3    | NAND Networks                          | 41         |

|    |     | 3.1.4    | Concluding Remarks                     | 47         |

|    | 3.2 | MSI M    | odules                                 | 47         |

|    |     | 3.2.1    | Full Adder                             | 47         |

|    |     | 3.2.2    | Multiplexor                            | 55         |

|    |     | 3.2.3    | Encoder                                | 63         |

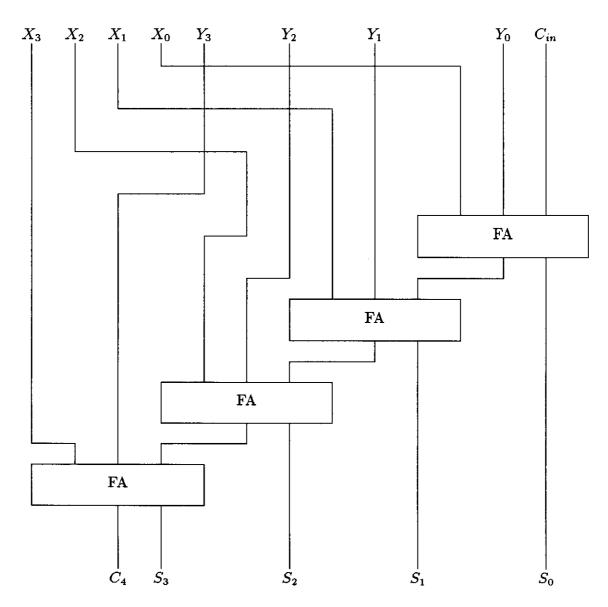

|    |     | 3.2.4    | Ripple Carry Adder                     | 69         |

|    |     | 3.2.5    | Concluding Remarks                     | 74         |

|    | 3.3 | LSI Mo   | $\operatorname{odules}$                | 74         |

|    |     | 3.3.1    | Conditional Sum Adder                  | <b>75</b>  |

|    |     | 3.3.2    | Carry Save Multiplier                  | 84         |

|    |     | 3.3.3    | Concluding Remarks                     | 95         |

|    | 3.4 | Compo    | osite Circuit                          | 95         |

| 4  | Sun | ımary    | and Conclusions                        | 102        |

| Δ  | Syn | tax of : | rp                                     | 110        |

| 11 | •   |          | s                                      | 110        |

|    | A.2 | _        | ation                                  | 110        |

|    |     |          | ons                                    | 111        |

|    |     | A.3.1    |                                        | 112        |

|    |     | A.3.2    | Tail Functions                         | 112        |

|    |     | A.3.3    | Distribute From Left and Right         | 113        |

|    |     | A.3.4    | Identity                               | 114        |

|    |     | A.3.5    | Append Left and Right                  | 114        |

|    |     | A.3.6    | Transpose                              | 114        |

|    |     | A.3.7    | Rotate Left and Right                  | 116        |

|    |     | A.3.8    | Predicate (Test) Functions             | 117        |

|    |     | A.3.9    | Predicate operators: and, or, not, xor | 119        |

|    |     | A.3.10   | Arithmetic/Logical                     | 119        |

|    |     | A 3 11   | Circuit Primitives                     | 121        |

|   |            | A.3.12 Library Routines (Used in Simulations) 122 |

|---|------------|---------------------------------------------------|

|   | <b>A.4</b> | Combining Forms                                   |

|   |            | A.4.1 Compose                                     |

|   |            | A.4.2 Construct                                   |

|   |            | A.4.3 Apply-to-All                                |

|   |            | A.4.4 Conditional                                 |

|   |            | A.4.5 Constant                                    |

|   |            | A.4.6 Right Insert                                |

|   |            | A.4.7 Left Insert                                 |

|   |            | A.4.8 Right Seq                                   |

|   |            | A.4.9 Left Seq                                    |

|   | A.5        | Time Domain Functions and Combining Forms         |

|   | <b>A.6</b> | User Defined Functions                            |

| ъ | TOT A      | AG User Manual 129                                |

| В | нья<br>В.1 |                                                   |

|   | D.1        | Functional Simulation                             |

|   |            | B.1.2 Steps                                       |

|   |            | B.1.3 Comments                                    |

|   | B.2        | Symbolic Interpretation and Topology Extraction   |

|   | 2.2        | B.2.1 Input                                       |

|   |            | B.2.2 Output                                      |

|   |            | B.2.3 Steps                                       |

|   |            | B.2.4 Comments                                    |

|   | B.3        | Physical Layout and Circuit Simulation            |

|   |            | B.3.1 Input                                       |

|   |            | B.3.2 Output                                      |

|   |            | B.3.3 Steps                                       |

|   |            | B.3.4 Comments                                    |

|   | <b>B.4</b> | Graphical Display                                 |

|   |            | B.4.1 Input                                       |

|   |            | B.4.2 Output                                      |

|   |            | B.4.3 Steps                                       |

# List of Figures

| 1.1  | Abstract View of the FLAG Design Process         | 4          |

|------|--------------------------------------------------|------------|

| 1.2  | Computation Graph and its Associated Hypergraph  | 8          |

| 1.3  | Planar Embedding of the Computation Graph        | 10         |

| 1.4  | Planar Graph Broken into Cross Sections          | 11         |

| 1.5  | Conceptual View of the VIVID System              | 14         |

| 2.1  | Conventional Design Cycle                        | 19         |

| 2.2  | FLAG Design Cycle                                | 22         |

| 2.3  | 3-Bit Decoder Block Diagram: Conventional Design | <b>25</b>  |

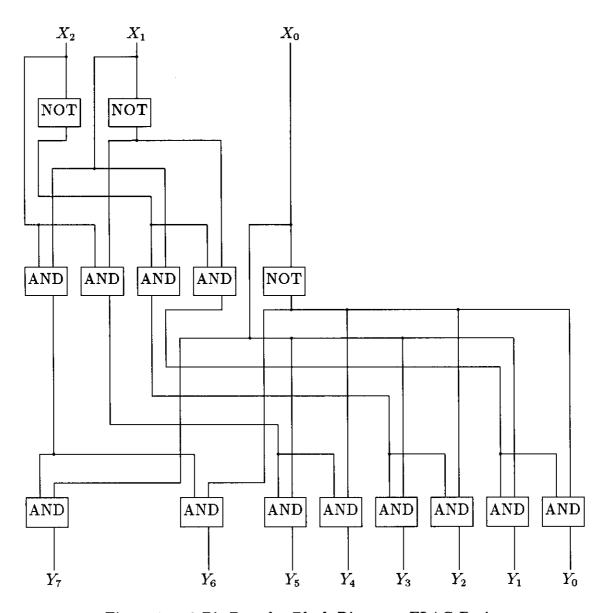

| 2.4  | 3-Bit Decoder Block Diagram: FLAG Design         | 28         |

| 3.1  | XOR Schematic                                    | 31         |

| 3.2  | Exclusive Or Logic Diagram: FLAG Design          | 34         |

| 3.3  | Exclusive-OR: FLAG layout                        | 35         |

| 3.4  | Exclusive-OR: Hand layout                        | 35         |

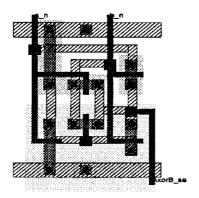

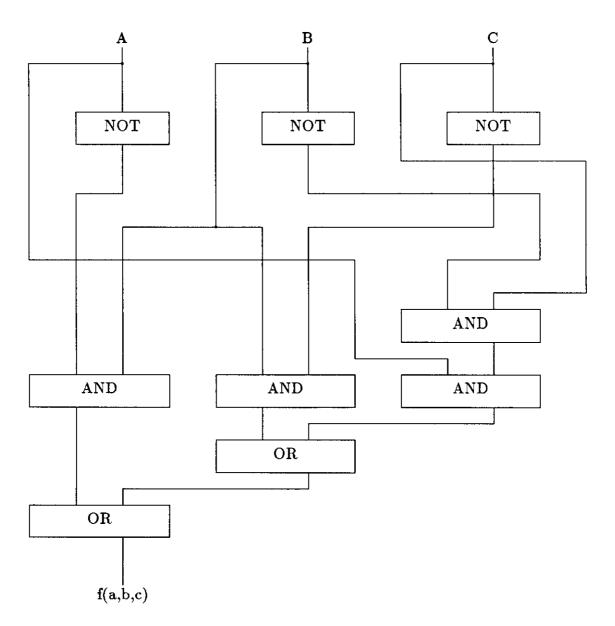

| 3.5  | AND-OR Logic Diagram: FLAG design                | 37         |

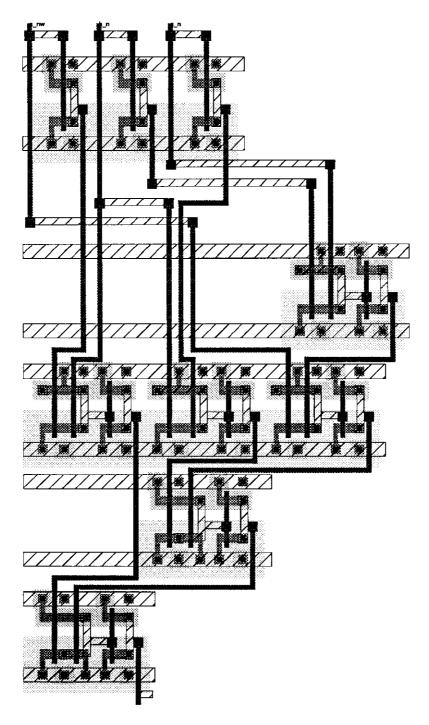

| 3.6  | AND-OR: FLAG layout                              | 38         |

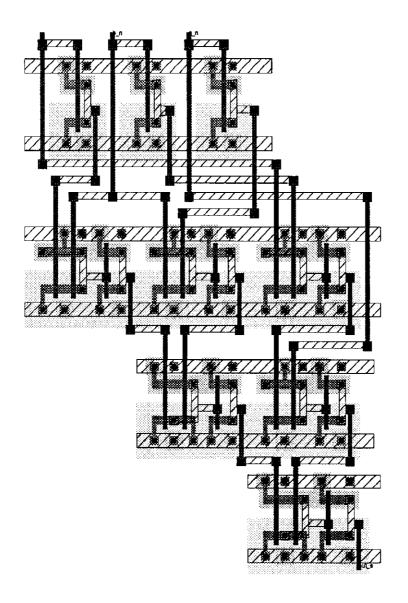

| 3.7  | AND-OR: Hand layout                              | <b>3</b> 9 |

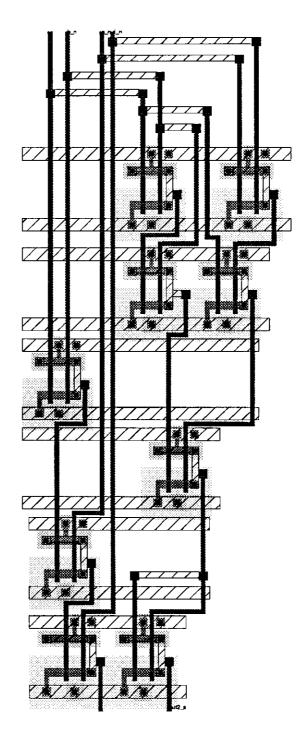

| 3.8  | NAND: FLAG layout                                | 43         |

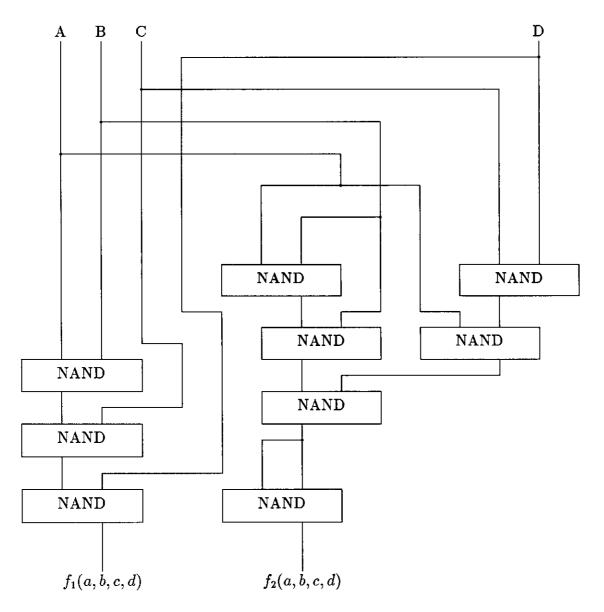

| 3.9  | NAND Network Logic Diagram: Hand design          | 44         |

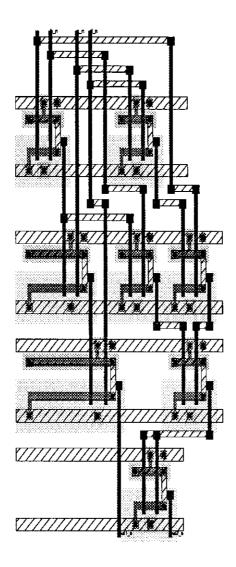

| 3.10 | NAND: Hand layout                                | 45         |

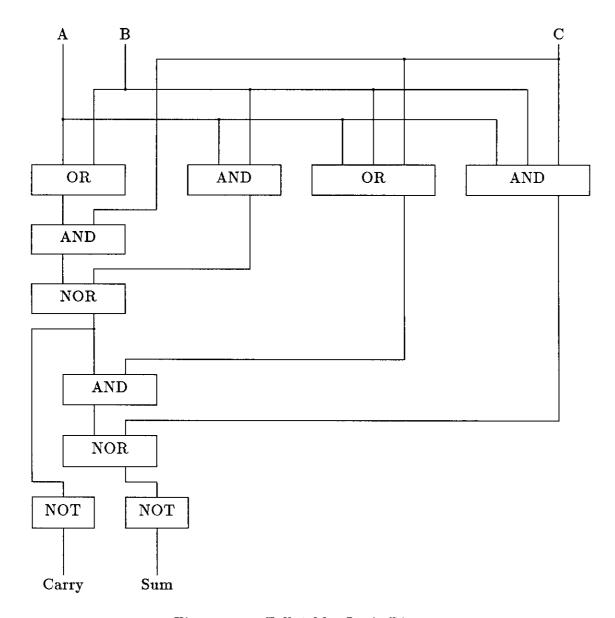

| 3.11 | Full Adder Logic Diagram                         | 48         |

| 3.12 | Full Adder schematic                             | <b>4</b> 9 |

| 3.13 | Full Adder Logic Diagram: FLAG design            | 52         |

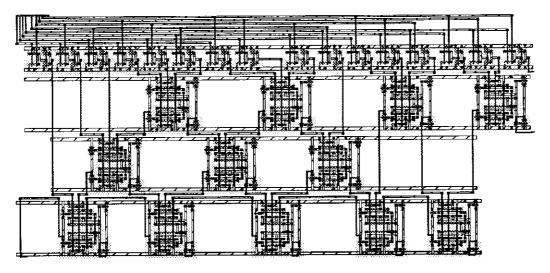

| 3.14 | Full Adder: FLAG layout                          | 53         |

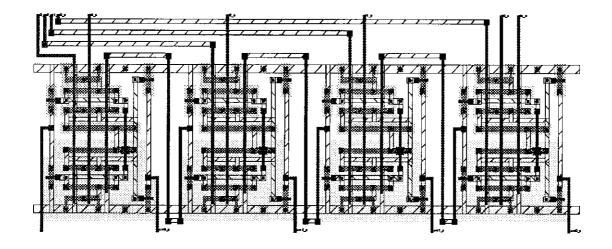

| 3.15 | Full Adder: Hand layout                          | 54         |

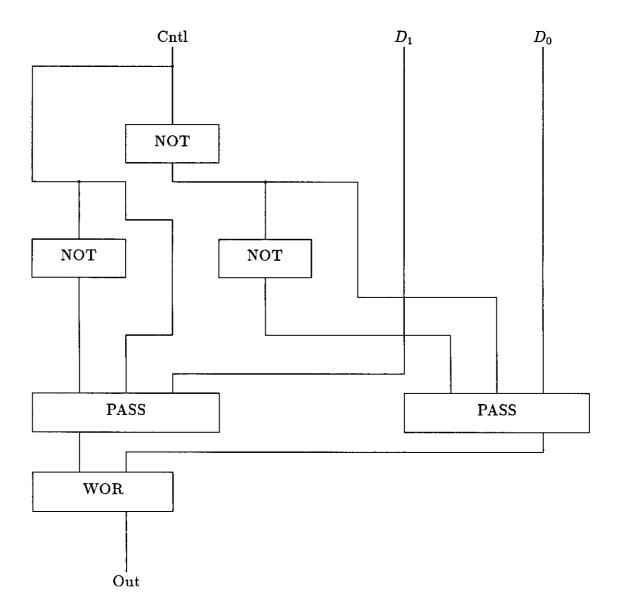

| 2 16 | 2 Input Multiployer Logic Diagram: FLAC design   | 59         |

| 3.17       | 2-Input Multiplexor: FLAG layout                                | 60  |

|------------|-----------------------------------------------------------------|-----|

| 3.18       | 2-Input Multiplexor Logic Diagram: Hand design                  | 61  |

| 3.19       | 2-Input Multiplexor: Hand layout                                | 62  |

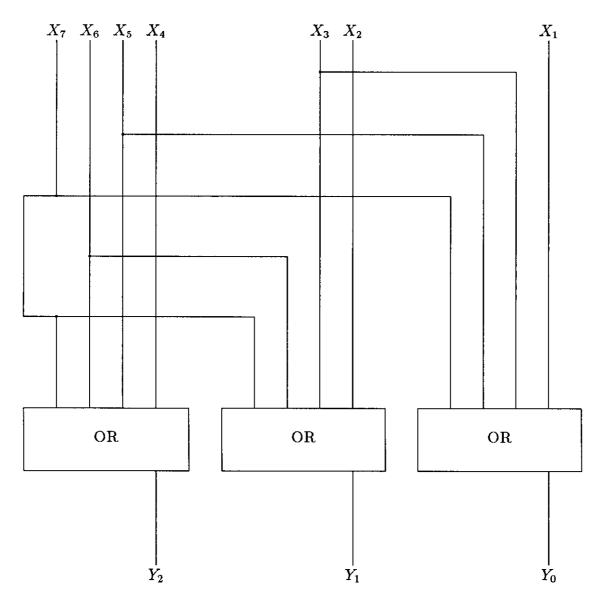

| 3.20       | 8-Bit Encoder Logic Diagram                                     | 66  |

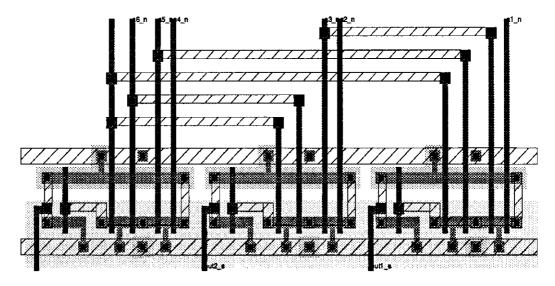

| 3.21       | 8-Bit Encoder: FLAG layout                                      | 67  |

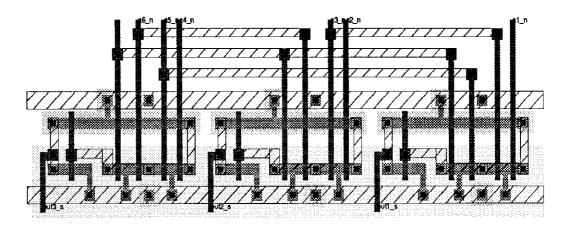

| 3.22       | 8-Bit Encoder: Hand layout                                      | 67  |

| 3.23       | 4-Bit Ripple Carry Adder Logic Diagram                          | 71  |

| 3.24       | 4-Bit Ripple Carry Adder: FLAG layout                           | 72  |

| 3.25       | 4-Bit Ripple Carry Adder: Hand layout                           | 72  |

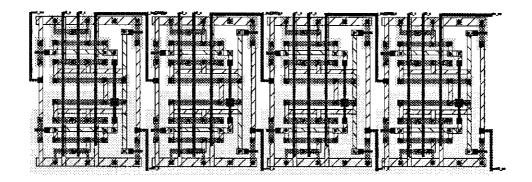

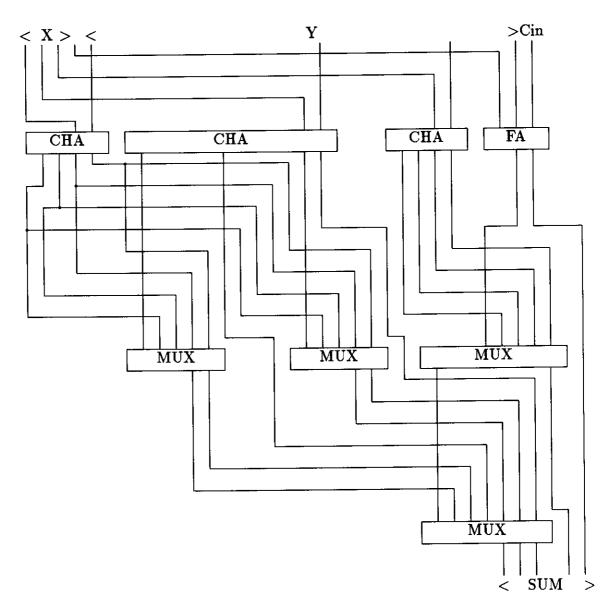

| 3.26       | 4-bit Conditional Adder Logic Diagram                           | 81  |

| 3.27       | 4-bit Conditional Sum Adder: FLAG layout                        | 82  |

| 3.28       | 4-bit Conditional Sum Adder: Hand layout                        | 83  |

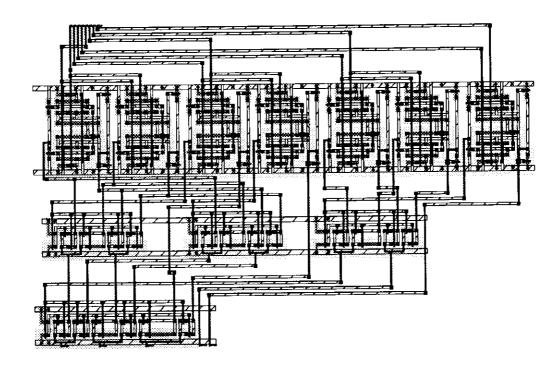

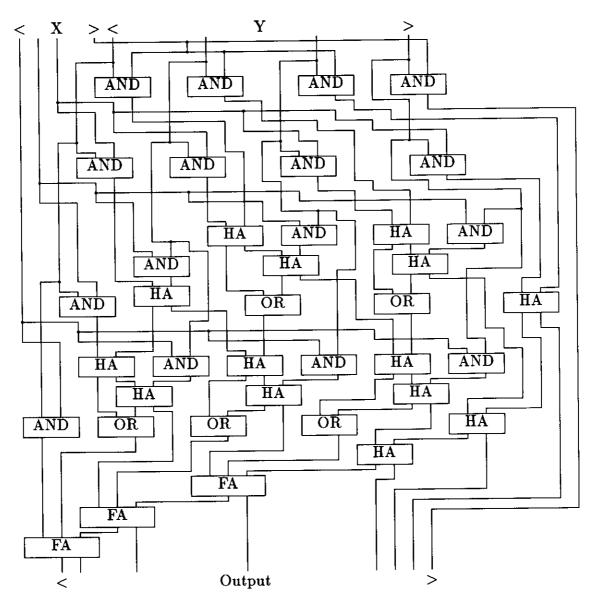

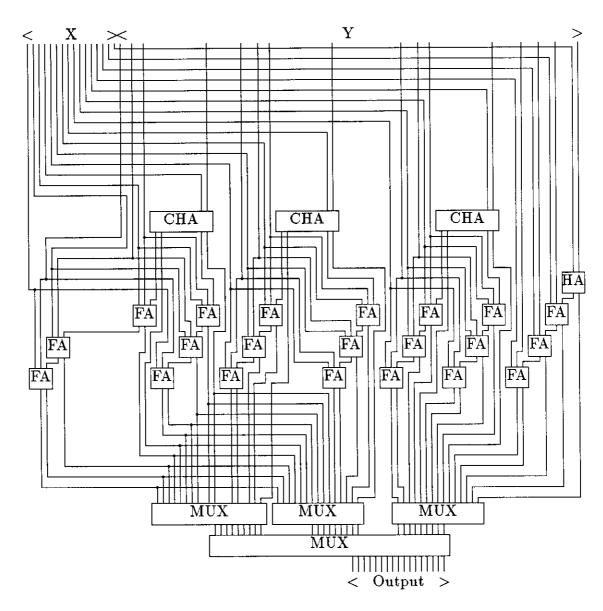

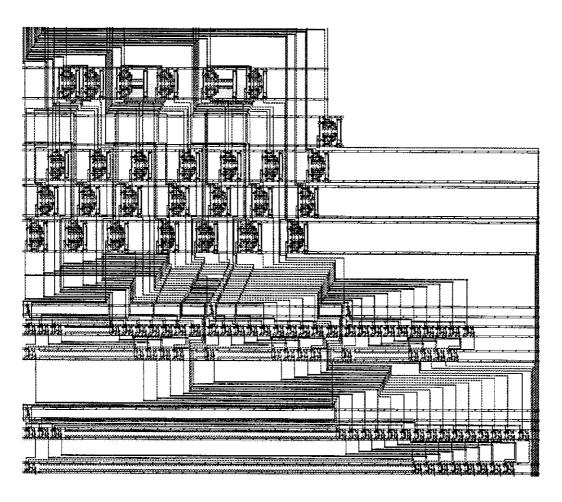

| 3.29       | A $4 \times 4$ Carry-Save Multiplier Logic Diagram: FLAG design | 91  |

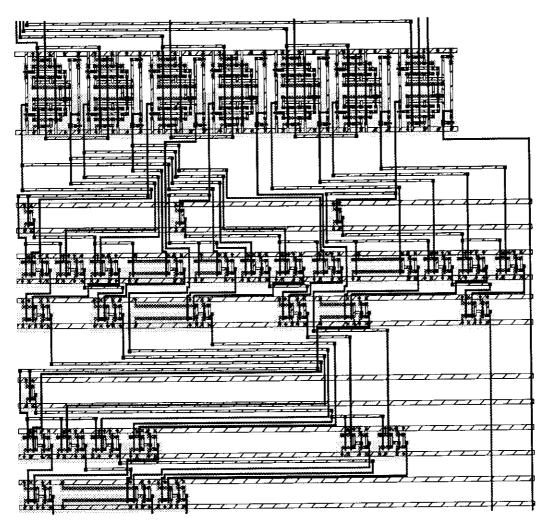

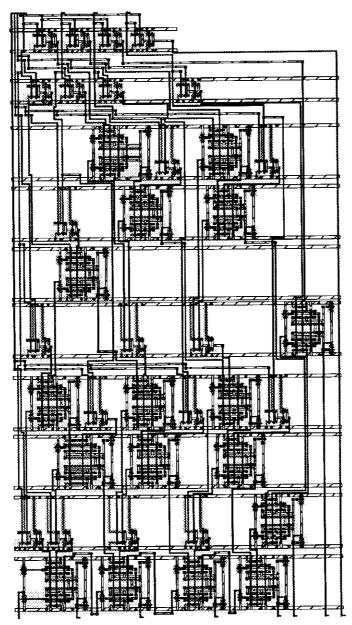

| 3.30       | A $4 \times 4$ Carry Save Multiplier: FLAG layout               | 92  |

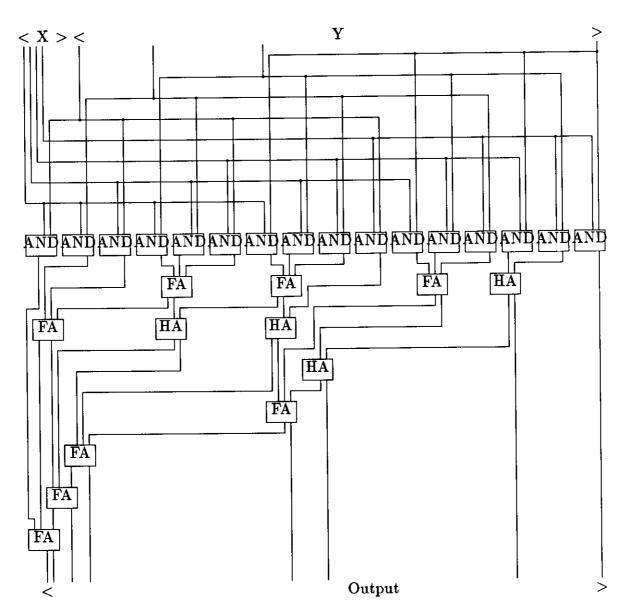

| 3.31       | A $4 \times 4$ Carry Save Multiplier Logic Diagram: Hand design | 93  |

| 3.32       | A $4 \times 4$ Carry Save Multiplier: Hand layout               | 94  |

| 3.33       | 16-bit Composite Adder Logic Diagram                            | 99  |

| 3.34       | 16-bit Composite Adder layout                                   | 100 |

| B.1        | Abstract View of FLAG                                           | 130 |

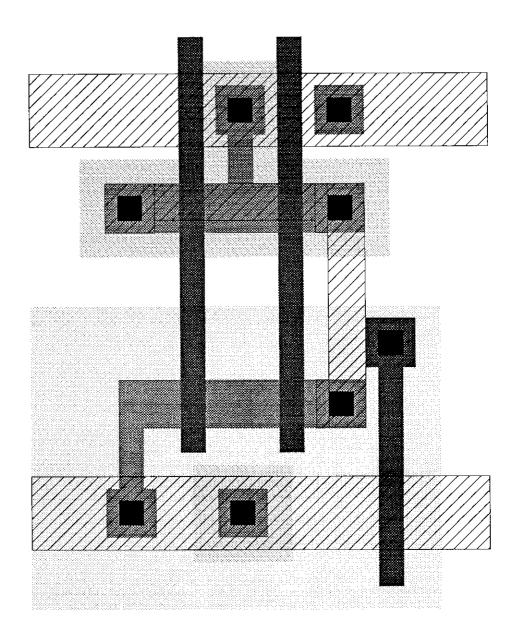

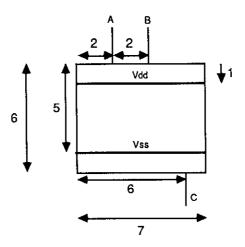

| <b>B.2</b> | Example Layout of a 2-Input NAND                                | 139 |

| B.3        | Graphical Interpretation of NAND                                | 141 |

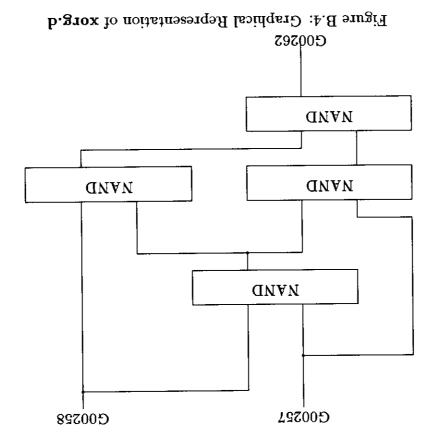

| <b>B.4</b> | Graphical Representation of xorg.d                              | 147 |

|            |                                                                 |     |

# List of Tables

| 3.1  | Exclusive Or Comparison                        |

|------|------------------------------------------------|

| 3.2  | AND-OR Network Comparison                      |

| 3.3  | Critical Paths in AND-OR Network               |

| 3.4  | NAND Network Comparison                        |

| 3.5  | Full Adder Comparison                          |

| 3.6  | Multiplexor Comparison                         |

| 3.7  | Encoder Comparison                             |

| 3.8  | Ripple Carry Adder Comparison                  |

| 3.9  | Example of addition by a conditional sum adder |

| 3.10 | Conditional Sum Adder Comparison               |

| 3.11 | Carry-Save Multiplier Comparison               |

| 3.12 | Adder Delay Comparison                         |

| 4.1  | Ratios of FLAG vs Hand Design Parameters       |

# **ACKNOWLEDGMENTS**

First of all, I would like to thank my advisor, Miloš Ercegovac for all his guidance and patience. Next, I would like to thank my committee members, Tomas Lang and Yuval Tamir for their comments during the writing of this work. I would also like to thank my parents for their continual encouragement and support during this work. In addition, I would like to thank Dorab Patel and Martine Schlag, whose work formed the basis for much of this work. Finally, I would like to thank all my friends for their help and support during the writing of this work.

#### Abstract

Rapid prototyping and architectural exploration are not possible in typical design systems due to either the amount of designer effort required or the lack of designer control over the final design. An FP based VLSI Layout Generator (FLAG) is presented whose main objective is to provide rapid prototyping and architectural exploration as part of the design approach. FLAG takes as input a behavioral description of the circuit, written in an applicative language (FP) and generates a VLSI layout from it. A number of circuits are created, ranging in complexity from an exclusive-OR to a carry-save multiplier. For each circuit, a VLSI layout is created by hand and by FLAG. The FLAG and hand layouts are compared against each other on the basis of overall layout area, circuit delay and circuit design time.

## Chapter 1

### Introduction

#### 1.1 Problem

Typical VLSI design systems take some form of schematic input and convert it into a physical layout. The schematic input can take the form of a functional description, block diagram, circuit diagram, behavioral description, or digital algorithm. The conversion of the schematic input to physical implementation can either be accomplished by hand or the process can be automated.

If the schematic conversion is performed by hand, the designer is responsible for all aspects of the translation of the schematic input into a physical layout. This approach possesses the following drawbacks:

- It is slow and tedious: All aspects of the conversion must be performed by hand.

- It is error-prone: Human error is an unavoidable part of the process.

- It requires VLSI expertise: Since the designer is performing the physical layout, he must be aware of the various VLSI design issues that may affect the design.

- The scaling and combining of different circuits cannot be done easily.

Because of the drawbacks of this approach, rapid prototyping is not possible and architectural exploration is too costly in terms of time and effort to include as part of the design process.

Another method of schematic conversion is to automate the entire process and minimize the designer's participation in the design process through the use of automatic layout tools and silicon compilers. Automatic layout tools take a description of the circuit in terms of modules and net-lists and generates masks while silicon compilers generate circuit elements and interconnections from a behavioral description. Examples of automatic layout tools and silicon compilers are GAELIC, DELILA, Genesil, MacPitts, CAPRI, SCHOLAR and ARSENIC. This approach has the advantage that rapid prototyping is now feasible. All that is required from the designer is a schematic description of the intended circuit. A drawback of this approach is that the designer often has little or no control over the structure of the physical layout and there is no way to guarantee that the final design will correspond to the designer's intentions. This becomes an obstacle to architectural exploration since the designer has lost the ability to specify the structure of the final circuit.

The goal of this thesis is to present a VLSI design approach whose objective is to provide rapid prototyping and architectural exploration as part of the overall design cycle. The approach is based upon FLAG, (FP based VLSI Layout Generator), which takes an algorithm written in a functional programming language, FP, as input and automates the generation of a physical layout while still allowing the designer to retain control over the design of the resulting physical layout. This work is based upon the theoretical work of [Schl84,Schl86] and upon her implementation of the symbolic interpreter. Related work has been done by [Laht81,Mesh84,Pate85,Worl86,Shee84].

The circuits generated by FLAG are meant to be a first approximation of the hand-generated ones and are not meant to replace them. We restrict our attention to combinational circuits and systems; sequential circuits and systems will not be considered here.

#### 1.2 Approach

The goal of FLAG is to allow architectural exploration to become part of the typical design cycle. The "philosophy" of the FLAG approach can be stated as follows.

- Automating the tedious aspects of the design cycle with the intention of minimizing the designer intervention.

- Providing the designer with control over the overall structure of the final design.

- Promoting a hierarchical design approach.

- Providing quick feedback about a particular design at various levels of abstraction.

- Providing an interface to lower-level VLSI CAD tools.

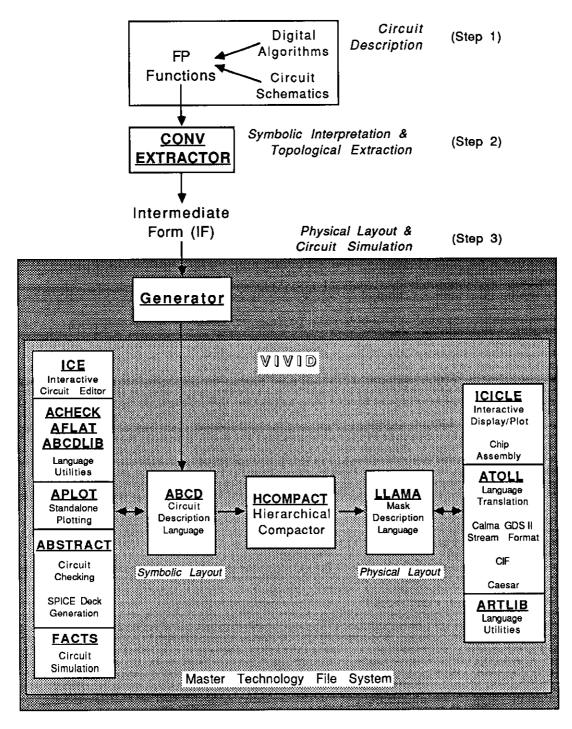

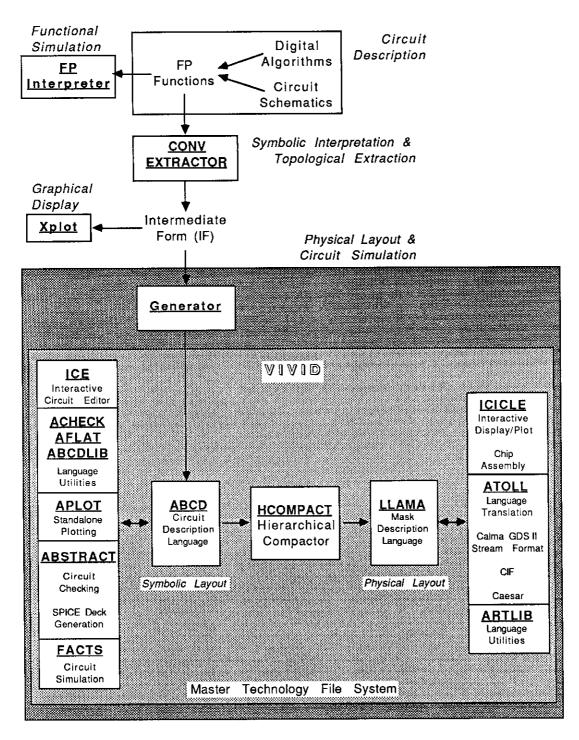

An abstract view of the FLAG design cycle is shown in Figure 1.1. The design process can be broken down into three steps:

- 1. System Behavior and Structural Description

- 2. Symbolic Interpretation & Topological Extraction

- 3. Physical Layout and Circuit Simulation

#### 1.3 Circuit Description

In Step 1, a description of the target circuit's behavior and structure is generated in an applicative language, FP<sup>1</sup>, that has been modified to facilitate its us as a hardware description language. The description can be created from an algorithm or circuit diagram and is written as a series of FP functions. The manner in which a circuit's structure is described will be discussed in the next section. The advantages gained from describing the circuit with an applicative hardware description language are:<sup>2</sup>

• Describes the structure and behavior of a circuit at a high-level.

<sup>&</sup>lt;sup>1</sup>J. Backus, "Can Programming Be Liberated from the Von Neumann Style? A Functional Style and Its Algebra of Programs," CACM Turing Award Lecture, Vol. 21, No. 8 (August 1978), 613-641.

<sup>&</sup>lt;sup>2</sup>Dorab Patel, Martine Schlag, and Miloš Ercegovac, "νFP: An Environment for the Multi-level Specification, Analysis, and Synthesis of Hardware Algorithms," Functional Programming Languages and Computer Architecture, J.P. Jouannaud, Ed. Nancy, France: Springer-Verlag Lecture Notes in Computer Science, September 1985, pp. 238-255.

Figure 1.1: Abstract View of the FLAG Design Process

- The description can be used to simulate the circuit. This permits rapid testing and preliminary debugging of designs.

- Generic functions can be defined, independent of the size of their arguments; for example; a function which adds two bit vectors of any size can be defined.

- In FP, the combining forms specify precedences and parallelism between functions. The use of these forms allows various algorithmic structures to be recognized and exploited.

- The FP combining forms interconnect and instantiate functions yielding graphs with functions as nodes (see [Schl86]) allowing the structure of the function to be extracted.

- Computations can be viewed, in FP, as consisting of two types of activities: directing data movement and changes in value. In FP, the delineation between these two activities is often explicit and can be used to facilitate the extraction of structural information from an FP function (see [Schl86]).

- The algebraic properties of FP present the possibility of transforming an algorithm by applying algebraic identities to its FP specification.

#### 1.4 Symbolic Interpretation

In Step 2, the circuit description is symbolically interpreted<sup>3</sup>, through the use of symbolic objects, to create a computation graph of the circuit. The symbolic output object generated by the FP combining forms can be determined from the symbolic outputs of their sub-functions until only nodes corresponding to primitives remain. The resulting graph is the computation graph for the circuit. The replacement of nodes by the structure of their associated functions can be monitored to obtain a hierarchical representation of the computation graph.

The unit of information represented by a single element (atom) of a symbolic object can be arbitrary: it reflects the level of abstraction desired in the representation of an FP expression. For example, in a decoder each atom would

<sup>&</sup>lt;sup>3</sup>Martine Schlag, "Extracting Geometry from FP for VLSI Layout," UCLA, Los Angeles, California, Tech. Rep., CSD-840043, October 1984., pp.8-11.

most likely be a bit, while in a Fast Fourier Transform (FFT), each atom could represent a complex number. Once the level of representation of the atoms is fixed, the FP primitives of an FP expression can be classified into one of the following two categories.

Computational Primitives These functions have the potential to generate atoms which are not copies of atoms in the input object and/or whose effect is determined by the value of the input atoms (such as a comparator).

Routing Primitives These functions never create new atoms and their effect is independent of the value of their input atoms. They merely rearrange the atoms within an FP object, possibly leaving some out and replicating others.

Routing primitives can be executed on symbolic objects. Computational primitives cannot and must be represented as black boxes; their output is a symbolic object with new labels. Computational primitives whose symbolic output object cannot be determined from a symbolic input object (e.g. iota) can not be used. Computational primitives are the primitive components of the layout, while routing primitives yield connectivity between intermediate input and output objects.

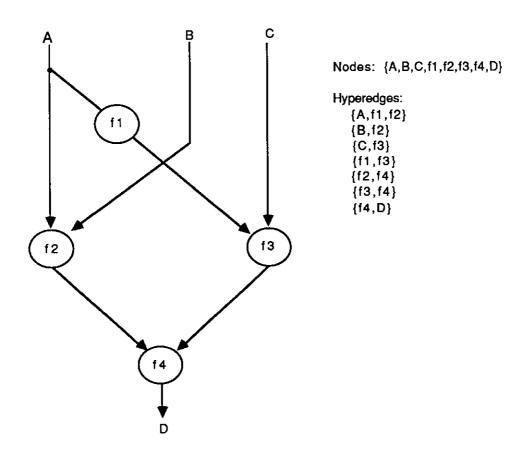

# 1.4.1 Defining the Corresponding Structure of an FP Expression

The amount of information extracted and retained from the routing functions and FP functional forms of an FP expression is what defines the term "corresponding structure." At a minimum, this information includes the connectivity of the computation graph: the enumeration of the primitives as boxes and their interconnections by net lists. A net list is generated for each atom occurring in the computation graph; it is a list of each occurrence of the atom as an input or output object of a primitive. The connectivity of the computation graph can be described by a hypergraph<sup>4</sup>. The primitives of the computation graph are the

<sup>&</sup>lt;sup>4</sup>A hypergraph is the generalization of a graph to higher dimensions. It consists of a set of vertices and a set of "hyperedges." Each hyperedge is a non-empty subset of vertices. See Berge, C. Graphs and Hypergraphs, North-Holland 1973.

vertices of the hypergraph and the net lists describing the interconnections of the atoms in the hypergraph are the hyperedges.

The hypergraph is obtained by traversing the computation graph with symbolic objects keeping track of each atom input to a primitive and each new atom generated by a primitive. The routing primitives can be executed during this traversal to remove them as primitives. Only the connectivity generated by the FP functional forms and routing functions is retained in the hypergraph. However, FP functional forms and routing functions contain information which can be used to "layout" this hypergraph. Each functional form implies a spatial (planar) organization of its components and each routing primitive, a routing pattern. Thus the "structure" of an FP expression must encompass the connectivity of the computation graph and may contain additional information extracted from the combining forms and routing primitives. Figure 1.2 shows a computation graph and its associated hypergraph.

The structure of an FP function could be defined merely as the connectivity of the computation graph, but its distance from "real layouts" will require the use of conventional routing and placement tools. A definition of structure "closer" to fixed geometry and yet retaining functionality would be more advantageous. "Relative geometry" or "topology" can be extracted from an FP expression by using the ordering of the atoms within an FP object and retaining the spatial organization implied by the FP functional forms. In this type of structure, the relative placement of elements is specified without specifying their dimensions or exact coordinates.

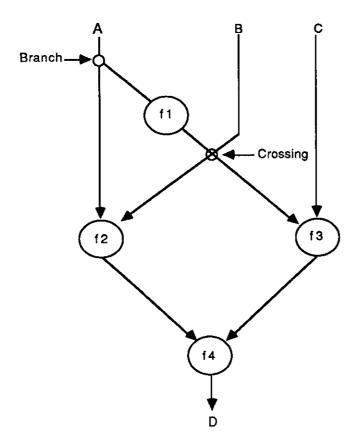

Formally, the "topology" of an FP expression can be defined as an embedding in the plane of a graph corresponding to the hypergraph. This planar graph is comprised of three types of nodes. The first type is a primitive of the computation graph or vertex of the hypergraph. The second type is a branch node which is used in representing a hyperedge (net-list). The third type is a crossing node which is needed to obtain a planar graph. The crossing node always has four incident edges, two pairs, each pair belonging to a wire. Examples of these nodes can be found in Figure 1.3. The edges interconnecting these nodes correspond to a single atom and thus can be mapped to wires. In essence, each hyperedge of the computation graph is mapped to a tree whose interior nodes are either branch or crossing nodes and whose leaves are the original nodes of the computation

Figure 1.2: Computation Graph and its Associated Hypergraph

graph belonging to this hyperedge. Figure 1.3 shows the planar embedding for the computation graph of Figure 1.2.

It is possible to define for each FP expression such a planar graph along with its embedding. In particular, it is possible to use FP objects in representing this "structure." To obtain fixed geometry, some type of compaction tool must be employed. Although the exact positions of elements are unknown, the fixed geometry obtained will still reflect the "topology" of the FP expression. Thus algebraic transformations on the FP expressions can predictably affect the positions in the "real layout" of nodes of the computation graph. See [Schl86] for more detailed information.

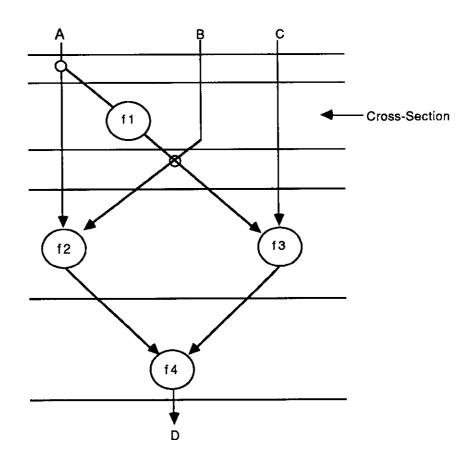

#### 1.4.2 Intermediate Form Generation

The planar graph created from the FP description of the circuit is translated into a format, referred to as the Intermediate Form (IF), for representing the "topological" structure of FP expressions. The intermediate form represents the planar graph and its embedding created from an FP expression. A planar graph and its embedding is represented by dividing the plane into horizontal slices (cross-sections), and for each cross-section, listing the elements of the graph within or spanning the cross-section from left to right. Figure 1.4 breaks the planar graph of Figure 1.3 into cross-sections. Absolute vertical coordinates can be assigned to elements by allowing elements of the graph to inherit their vertical position from the cross-sections containing them. The horizontal coordinates are not explicit; elements sharing the same vertical coordinates are only ordered horizontally.

This IF can be represented by FP objects. The use of FP objects to represent structure, allows the derivation of structure to be implemented within the FP framework. The IF is a list of cross-sections with the symbolic output object (of the FP expression) tagged on to the front. The symbolic output object is provided for the traversal of the computation graph. As the graph is traversed, the symbolic output object is removed, new cross-sections are added to the front, and the new symbolic output object is put on the front.

Figure 1.3: Planar Embedding of the Computation Graph

Figure 1.4: Planar Graph Broken into Cross Sections

Formally, the IF consists of FP objects of the following form<sup>5</sup>,

$$< PS \ CS_1 \ CS_2 \dots \ CS_n > \text{for } n \ge 0,$$

where PS is an FP object not containing the atoms: \$, \*, +,  $\land$ , and t (these atoms are reserved for use as delimiters) and each  $CS_i$  is a cross-section. A cross-section is a list of FP objects each corresponding to elements of the graph.

$$CS_i = \langle x_1 x_2 \dots x_m \rangle$$

where  $x_j$  is one of the following,

Free wire An atom (not \$, \*, +,  $\wedge$ , and t). Elements of this type are wires which traverse the cross-section without being crossed by any other wires.

Crossing  $\langle *w * u_1 u_2 \ldots u_h \rangle$  such that exactly one  $u_h$  is + and at least one is  $\wedge$ . This type of element represents the wire crossings and branchings necessary for realizing the connections of the computation graph. The atom w is in the position corresponding to '+' and must be distributed to each position corresponding to a ' $\wedge$ '. The other atoms are wires which traverse this cross-section.

$\mathbf{Box} < \$ \ level \ \#levels \ id \ label \ \$ \ i_1 \ i_2 \dots \ i_k \ \$ o_1 \ o_2 \dots \ o_l \ \$ >$

Elements of this type correspond to the primitives which are to be drawn as boxes. The format allows the specification of how many cross-sections a box will occupy. In a strictly "topological" IF, this is not necessary since the dimensions of the elements are not relevant. However, if the cross-sections are used to assign vertical coordinates to these elements, this format is necessary to allow boxes to have varying sizes. The level is f, l, i, or b, indicating whether this is the first, last, intermediate or both (when a box is wholly contained within one) cross-section which the box occupies; an element of this type is instantiated for each cross-section in which it appears. The next three atoms are, respectively, the number of cross-sections occupied by this box, a unique identifier (which can be used to distinguish a box from others with the same label), and a label to be displayed with the box. The \$ acts as delimiters between these atoms, the input atoms,  $i_1, i_2, \ldots i_n$  and the output atoms,  $o_1, o_2, \ldots o_m$ .

<sup>&</sup>lt;sup>5</sup>Schlag, "Extracting Geometry from FP," pp.16-19.

Refer to [Schl84] for graphical interpretations of these elements and [Liao83] for a detailed discussion of the process for the assignment of horizontal coordinates to elements.

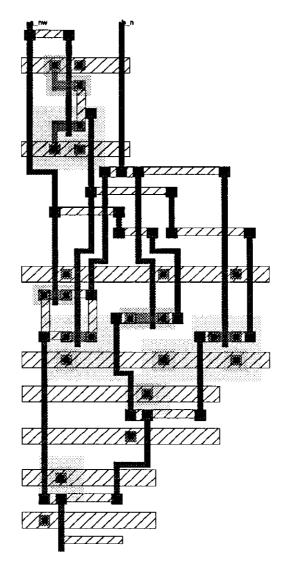

#### 1.5 Physical Layout and Circuit Simulation

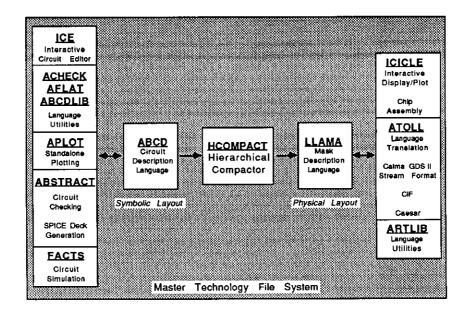

In Step 3, the IF is translated into ABCD, a circuit description language for VIVID<sup>6</sup>, and used as input for the VIVID system to perform the physical layout and circuit-level analysis. VIVID stands for the Vertically Integrated VLSI Design System developed at the Microelectronics Center of North Carolina [Roge86, Roge85]. The system is based on a symbolic, virtual-grid design methodology that greatly reduces the design time of custom VLSI circuits. This methodology makes it possible to provide, in a single integrated system, several features: technology independent tools for a wide range of MOS processes (CMOS, nMOS, SOI); scale independent circuit designs; open architecture that simplifies both integration with existing tools and creation of new tools; fast layout debugging using symbolic level circuit simulation; and fully automated mask generation and automated chip assembly. Figure 1.5 presents a conceptual view of the VIVID system<sup>7</sup>. It is divided into two main sections: symbolic layout and physical layout. The symbolic layout section contains the tools used to generate and manipulate symbolic, virtual-grid layouts, specified in ABCD (A Better Circuit Description) Language. The ABCD language provides a direct and well-defined interface to the symbolic, virtual-grid portion of the VIVID System. In the physical layout section, the mask descriptions generated by the compactor are specified in LLAMA (Layout Language for Mask Artwork) Language. Tools are provided to translate between LLAMA and other mask description languages.

<sup>&</sup>lt;sup>6</sup>C. D. Rogers, and S. W. Daniel, and J. B. Rosenberg, "An Overview of VIVID, MCNC's Vertically Integrated Symbolic Design System," **IEEE Design Automation Conference**, 1985, pp.62-68

<sup>&</sup>lt;sup>7</sup>Rogers, "An Overview of VIVID," pp.62-68.

Figure 1.5: Conceptual View of the VIVID System

#### 1.5.1 Symbolic, Virtual-Grid Layout

Symbolic, virtual-grid layout<sup>8</sup> can be viewed as an evolutionary refinement of physical mask layout. In physical mask layout, the designer specifies the circuit by drawing a set of polygons that indicate how to create a mask for each layer in the fabrication process. At the physical mask level, the basic elements of circuit design (such as transistors or contact cuts) are composite structures. Each transistor or contact cut is composed of polygons on several layers that are sized and positioned according to the design rules of the target fabrication process. In physical mask layout, each time one of these composite structures is needed, it is re-created from the component polygons. Symbolic layout provides a solution that eliminates this tedious and error-prone task.

With symbolic layout, symbols are provided to represent the most common structures. The designer organizes the symbols into a layout and the computer translates them into the proper mask representation. In its simplest form, the

<sup>&</sup>lt;sup>8</sup>Rogers, "An Overview of VIVID," pp.62-68.

translation is done by replacing each symbol with a fixed collection of polygons that implement the desired structure. A more flexible approach to symbol translation is to associate parameters with the symbols and to have a program use the parameters for generating a broad range of structures. For example, the symbol for a transistor might be accompanied by two parameters that specify the width and length of the gate region. The transistor generation program would then use parameters to size the transistor when constructing the mask layout.

Like symbolic design, virtual-grid layout is an extension of physical mask design. In physical mask design, the layout is usually created on a grid. The spacing of the grid represents some "real" spacing (for example, 3 u) and the designer uses the grid as an aid to establish the correct spacing between objects. The function of the virtual grid is the same as for a "real" grid except that the spacing between grid lines does not represent a fixed physical spacing. A symbol's placement captures only the relative geometry of the circuit. (For example, transistor A is above and to the right of transistor B) The actual spacing between two adjacent grid lines is determined by HCOMPACT, the compactor program. The compactor examines the objects on adjacent grid lines and, based on the design rules, determines the correct spacing between the grid lines. It does not perform any optimizations upon the circuit design.

#### 1.5.2 Layout Verification

The VIVID System provides two tools for verifying symbolic virtual-grid layouts; a symbolic level circuit extractor and an interactive circuit simulator<sup>9</sup> early in the layout process. The symbolic level circuit extraction is performed by the ABSTRACT (ABCD Circuit Extractor) program. ABSTRACT references the MTF System to calculate the electrical parameters associated with each circuit element. The calculated values are, by necessity, estimates since the mask generation has not been performed. However, these estimates are relatively accurate for all of the primitives except wires, which are directly dependent upon the final size of the layout. Reasonable estimates of wire length can be obtained by assuming that the spacing between the virtual grid lines will average out over the design. This average grid spacing parameter is coded in the MTF System

<sup>&</sup>lt;sup>9</sup>Rogers, "An Overview of VIVID," pp.62-68.

and can be tuned by the designer according to the technology being used and the performance of the compactor.

In conjunction with the circuit extraction, ABSTRACT performs error checking and provides the designer either textual or, via ICE, graphical feedback. The types of errors it can detect are overlapping or improper abutment of cells, unconnected or short-circuited components, and improperly named signals.

Circuit simulation is performed by the FACTS (Fast Circuit Simulator) program. The simulator has been designed for MOS simulations and can be used with circuits as large as several thousand devices. The speed of FACTS results from its selection of models and internal structure. Only MOSFET models are used and FACTS precalculates tables of simulation values before beginning a simulation. During the simulation, the designer can choose between two types of current modeling: a simple transistor current model or a more accurate second order model with saturation, linear, and cutoff regions; channel length modulation; drain and source threshold dependence; and capacitance modeling. FACTS also monitors all node voltages and, when the changes are small, increases the time step to avoid redundant or insignificant calculations.

Because of its simpler modeling and the use of symbolic, virtual-grid extraction, FACTS does not provide the accuracy of a full network analysis program. However, FACTS fills a gap between such programs and logic level simulators. It is faster than a detailed circuit simulator but still accurate enough to provide the waveform information necessary for debugging the analog behavior of a circuit. FACTS offers interactive features (such as probe capability to interrupt a simulation and observe any set of circuit nodes) to support its function as a debugging tool.

#### 1.6 Previous Work

[Laht81] showed that a functional style language could be used to specify combinational circuits and investigate their behavior. [Shee84] extended this to sequential systems. [Schl84,Schl86] investigated the extraction of topological information from functional programs. [Mesh84] analyzed timing in functionally specified combinational and sequential systems. [Pate85] explored a design environment based upon functional programs. [Worl86] examined a functional style

description for digital systems. [Lieb82,Lim65,Mori82,Vieg84] developed various hardware description languages. [Joha79,Ance83] developed a silicon compiler and a methodology for silicon compilation.

## 1.7 Objective

Chapter 2 scrutinizes the design cycle with and without FLAG. Chapter 3 discusses some circuits designed with FLAG and examines the results. Chapter 4 is the conclusion. A summary of the syntax of FP is provided in Appendix A. A user's manual for FLAG is provided in Appendix B.

## Chapter 2

## Design Environment

#### 2.1 Conventional Design Cycle

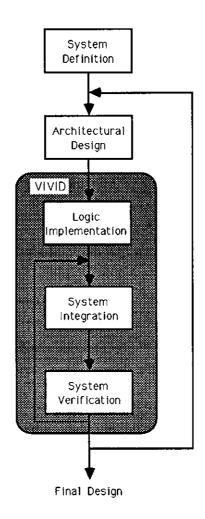

As is shown in Figure 2.1, a conventional design cycle for hand created VLSI circuits consists of the following 5 steps:

In the System Definition stage, the designer defines the functionality of the desired circuit from a circuit design, digital algorithm, circuit schematic, etc. The designer creates a behavioral description of the circuit which describes the system functionality. In the Architectural Definition stage, the architecture of the circuit is defined. From this architecture, a block diagram of the circuit is created and the circuit is partitioned into modules. Additionally, the function of the various modules is defined here. In the Logic Implementation stage, the modules are created and tested by the designer. Since the designer is responsible for the creation of the modules, he must be knowledgable about all aspects of VLSI circuit design. In the System Integration stage, the modules are integrated into the overall design and the module interconnections are laid out. Since this is done by hand, the process of system integration is slow and tedious. Further, errors can be introduced because of human error. These errors are unfortunately difficult to detect and tedious to correct. Finally, in the System Test stage, the functionality of the circuit produced is verified to ensure that it operates as intended. This is a slow process and may not be possible for large circuits.

In the typical design process, there are two feedback loops. The System Integration - System Verification loop attempts to uncover and correct any

Figure 2.1: Conventional Design Cycle

interconnection errors that resulted from the System Integration stage. Unfortunately, the process of error detection is slow and difficult. The correction of these errors must be done by hand and can be a rather tedious and possibly difficult task. The introduction of additional errors by the designer is not beyond expectation either. In the Architectural Design - System Verification loop, major design errors are detected and an attempt made to correct them. Possible errors include

- System functionality errors

- Timing errors

- Input-Output errors

These errors generally require a redesign of the circuit and a reiteration of the entire design cycle.

In the conventional design cycle, architectural exploration can not be introduced as part of the design cycle due to the large amount of time required in the generation of a single physical layout. Alteration of the system architecture is justifiable only if a major design error is discovered. It isn't reasonable for a designer to invest the time and effort necessary to change the system architecture unless a major payoff is evident. Therefore, architectural exploration becomes too expensive an activity to be included as a part of the design process because the probable gains do not outweigh the costs of the activity.

#### 2.2 Limitations

A typical hand-based design cycle suffers from the following limitations:

- The logic implementation and system integration steps are implemented from the bottom up.

- The logic implementation and system integration steps require VLSI design expertise by the designer.

- The logic implementation and system integration steps are tedious and error-prone.

• The scaling or combining of circuits requires re-execution of the system integration-system verification loop thereby requiring a large investment of time and effort by the designer.

These limitations of a typical design cycle are sufficient to prevent architectural exploration from being included as part of the design cycle.

#### 2.3 Advantages

A typical hand-based design cycle provides the following advantages:

- The designer has complete control over the layout produced.

- The designer can perform some hand optimizations upon the circuit at design time resulting in smaller and more efficient circuits.

#### 2.4 FLAG Design Cycle

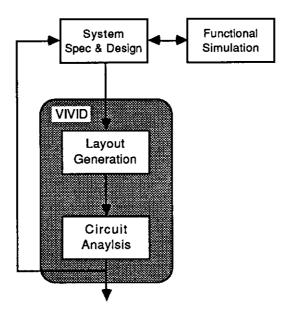

As is shown in Figure 2.2, the FLAG design cycle consists of the following 3 steps:

In the System Specification and Design stage, the designer creates a behavioral description of the digital algorithm or circuit design of interest in an applicative language, FP. To verify the correctness of the behavioral description, the description can be simulated functionally by the FP interpreter. Embedded in the behavioral description is the desired architecture for the physical implementation. In the Layout Generation stage, a physical layout is created from the behavioral description by FLAG and the VIVID. In the Circuit Analysis stage, the VIVID tools are used to examine the physical and electrical characteristics of the circuit for acceptability.

In the FLAG design cycle, there is only a single feedback loop namely the System Specification - Circuit Analysis loop. In this loop, there is little designer intervention required. As a result, the translation is quick and no additional errors can result from the translation of the behavioral description to a physical implementation. In addition, a different physical design can be created by modifying the behavioral description. No additional work is required and the designer retains control over the physical layout.

Figure 2.2: FLAG Design Cycle

In the FLAG design cycle, the time required to generate a physical implementation from a behavioral description is kept to a minimum. Therefore, it becomes feasible to experiment with various system architectures in order to find the most efficient design.

#### 2.5 Limitations

The FLAG design cycle suffers from the following limitations:

- Flow of data between modules is in a vertical direction. This is due to the current mapping scheme between the behavioral description and its physical realization.

- The designer does not have complete control over the placement of circuit elements within a layout.

- Designs are not as small as possible.

Module inputs enter only at the top of modules and their outputs appear only at the bottom.

These limitations are due mostly to the applicative language used to describe the system and the mapping used to translate the behavioral description into a physical layout.

#### 2.6 Advantages

The new design cycle provides the following advantages:

- Shortens the design cycle. It eliminates the tedious and error-prone portion of the design cycle and automates it.

- Designers are freed from low-level VLSI design issues.

- A correct FP description of the system produces a layout that is functionally correct.

- The scaling of circuits can be performed without requiring modification of the circuit description or additional effort by the designer.

- Different circuits can be combined together by combining their respective circuit descriptions without requiring a large investment of time and effort by the designer.

- A hierarchical design style is supported.

- Any given behavioral description corresponds to a single layout.

The advantages of the new design cycle make it possible to include architectural exploration as part of the design process. They shorten the design cycle enough that the designer can experiment with different architectures without investing a large amount of time.

#### 2.7 An Example

The design of a binary decoder will be followed through both design cycles to illustrate the differences between them. A binary decoder takes N binary inputs

and generates  $2^N$  binary outputs. For any particular input pattern only one output is true.

#### 2.7.1 Typical Design Cycle

System Definition:

Input:  $\langle X_{N-1}, ..., X_0 \rangle$

Output:  $< Y_{2^{N}-1}, ..., Y_{0} >$  where:

$$Y_i = \left\{ egin{array}{ll} 1 & ext{if } i = \sum\limits_{j=0}^{N-1} X_j imes 2^j \ 0 & ext{Otherwise} \end{array}

ight.$$

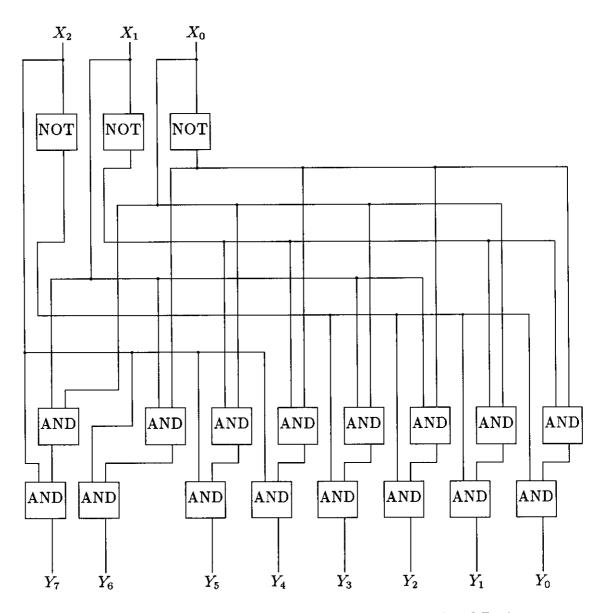

Architectural Design A block diagram for the decoder design is given in Figure 2.3. The only modules required are inverters and 2-input AND-gates.

Logic Implementation Trivial since the design for an inverter and an AND-gate are fairly standard and are probably part of any cell library.

System Integration The modules must be placed by hand according to the block diagram and the interconnections between them must be laid out. Unfortunately, this is often done by hand and is quite slow and tedious.

System Verification The design must be simulated in order to ensure correct operation of the circuit. If any errors are found, they must be corrected by hand.

#### 2.7.2 FLAG Design Cycle

System Specification and Design:

Input:  $\langle X_{N-1}, ..., X_0 \rangle$

Output:  $< Y_{2^{N}-1}, ..., Y_0 >$  where:

$$Y_i = \begin{cases} 1 & \text{if } i = \sum_{j=0}^{N-1} X_j \times 2^j \\ 0 & \text{Otherwise} \end{cases}$$

The function **decode** takes a vector of arbitrary length and returns a fully decoded version of the input. The format of the input is  $\langle x_{n-1} \dots x_0 \rangle$ .

Figure 2.3: 3-Bit Decoder Block Diagram: Conventional Design

The format of the output is  $\langle y_{2^n-1} \dots y_0 \rangle$ , where

$$y_k = \begin{cases} 1 & \text{if } \underline{X} = k \\ 0 & \text{otherwise} \end{cases}$$

The decode<sup>1</sup> function can be broken into the following steps<sup>2</sup>.

If (length of input = 1)

1 Perform a decode function upon a single bit

Else

- 1 Split the input into two vectors

- 2 Recursively apply decode to each vector to fully decode it

- 3 Form all possible pairs from the two decoded vectors

- 4 Reduce pairs to single bit vectors

```

DEFINE decode

IF (length = 1)

THEN decode_1@1

ELSE

& andg @

cross_match @

& decode @

split

ENDIF

```

The function decode\_1 takes an input of a single-bit and returns a fully decoded version of the input. The format of the input is  $\langle x \rangle$ . The format of the output is  $\langle x \overline{x} \rangle$ .

<sup>&</sup>lt;sup>1</sup>John Shelby Worley, "A Functional Style Description of Digital Systems", MS Thesis UCLA 1986, pp. 78-80.

<sup>&</sup>lt;sup>2</sup>See Appendix A for a description of the FP language.

```

DEFINE decode_1

[id, notg]

END

```

The function cross\_match takes an input of two vectors of arbitrary length and returns a vector containing all the possible pairs that can be formed from the input. The format of the input is  $<< x_{2^{\frac{n}{2}}-1} \dots x_0 >< y_{2^{\frac{n}{2}}-1} \dots y_0 >>$ . The format of the output is  $<< x_{2^{\frac{n}{2}}-1} y_{2^{\frac{n}{2}}-1} > \dots < x_{2^{\frac{n}{2}}-1} y_0 >< x_{2^{\frac{n}{2}}-2} y_{2^{\frac{n}{2}}-2} > \dots < x_0/; y_0 >>$ .

```

DEFINE cross_match

concat @

&distl @

distr

END

```

Correct functioning of the design can be verified through FP interpreter.

Layout Generation: The FP description is used by the layout generator to produce a physical layout of the proposed decoder design. A block diagram of the design is given in Figure 2.4.

Circuit Analysis: The physical layout's characteristics, area, module placement, delay are examined. If the design is not satisfactory, then another architecture can be created by modifying the FP description and re-running the layout generator.

#### 2.7.3 Discussion

In the typical design cycle, the system integration-system verification loop is the most time-consuming and tedious from the perspective of the designer. A lot of time and effort is spent in producing the physical realization of a proposed design since every aspect of the physical layout process must be performed by hand. Any errors introduced during the layout process must be detected and corrected by hand. With the FLAG design cycle, the designer is relieved of the burden of translating the block diagram into a physical layout. The designer only has

Figure 2.4: 3-Bit Decoder Block Diagram: FLAG Design

to generate the FP description of the circuit. FLAG creates a physical layout directly from the FP specification of the architecture without any additional input from the designer. An advantage of this is that no design errors will be in the physical layout if the FP specification of the design is correct. During the creation of the FP specification, the designer can verify the correctness of the specification with the FP interpreter. Checking the FP specification is a much simpler and quicker process than laying out an entire circuit and having to perform a circuit simulation to see that it functions correctly. With FLAG, once the FP description of the circuit has been created, a simple version of the circuit can be created and tested. For instance, with the decoder, a 2-bit decoder can be created and examined. If the resulting circuit is acceptable, a decoder of arbitrary length can be created without any additional work from the designer. In the typical design cycle, it is not possible to scale circuits as easily as with FLAG. Another advantage, provided by FLAG, is that composite circuits can be created by just combining the the FP descriptions of different circuits.. In the normal design cycle, the creation of a composite circuit would require at least the reexecution of the system integration-system verification loop which would require a lot of work from the designer. The FLAG design cycle frees the designer from the unimportant activities of module placement and interconnection and allows him to concentrate upon the more interesting activity of architecture design.

## Chapter 3

# Design and Evaluation Experiments

A number of examples is presented here in order to examine some of the features and drawbacks of FLAG. The examples range from SSI logic networks to complex LSI logic networks. For each example, a CMOS design is produced by hand and by FLAG. The CMOS layouts are then compared on the basis of area, the bounding box of the layout being used as an approximation; percentage of white space present in the design; delay through the circuit; and design time required. Design time is defined as the time needed to create a physical layout from an algorithmic specification of a circuit. Since VIVID translates a symbolic layout (ABCD) into a physical layout, the design time for the hand-generated circuits is the time needed to create the symbolic layout (ABCD). For the FLAG circuits, since FLAG translates the behavioral description into a symbolic layout (ABCD) for VIVID, the design time for the FLAG circuits is the time needed to generate the correct behavioral description.

### 3.1 Simple Combinational Circuits

In this section, several SSI-level modules, including an exclusive-OR, AND-OR network, and a NAND network are designed and a discussion of the results is given in Sec. 3.1.4.

#### 3.1.1 Exclusive-Or

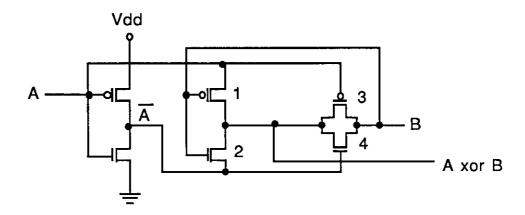

The exclusive-OR gate examined here will perform the exclusive-OR operation of two inputs. A canonical sum of products expression for the exclusive-OR of two inputs is:  $(\overline{a}b) + (a\overline{b})$ . Two approaches can be taken in the design of the exclusive-OR gate. Either a design based upon logic gates or a design based upon transmission gates can be used. Designs based upon transmission gates tend to be smaller in area and faster in terms of delay in comparison to their logic gate based counterparts. A logic diagram for the transmission gate exclusive-OR gate is shown in Figure 3.1<sup>1</sup>. The operation of the transmission gate exclusive-OR gate can be explained as follows:

- 1. When A is high,  $\overline{A}$  is low. Transistor pair 1 and 2 act as an inverter with  $\overline{B}$  appearing as the output. The pass gate formed by the transistors 3 and 4 is open.

- 2. When A is low,  $\overline{A}$  is high. The pass gate (transistor 3 and 4) is closed, passing B to the output. The inverter pair (transistor 1 & 2) is disabled.

Figure 3.1: XOR Schematic

In the description of the transmission-gate exclusive-OR, it is necessary to generate functional descriptions for the circuit elements used in the implementation: n-transistor, p-transistor, and a pass-gate. Functionally, the n-transistor

<sup>&</sup>lt;sup>1</sup>N. Weste and K. Eshraghian, Principles of CMOS VLSI Design: A Systems Perspective, (Reading, Massachusetts: Addison-Wesley, 1985), pp. 317.

acts like a gateway, passing its data if the gate input is high and turning itself off if the gate signal is low. This can be described functionally as an 'AND'ing together of the gate and data input. The format of the input is < gate, data > and the format of the output is < out >.

```

DEFINE n

andg

END

```

The p-transistor behaves in a similar fashion as the n-transistor except that it passes its data through when the gate input is low. Therefore, in description the gate input is inverted before the 'AND'ing is done. The format of the input is  $\langle gate, data \rangle$  and the format of the output is  $\langle out \rangle$ .

```

DEFINE p

andg @ [notg@1,2]

END

```

The pass-transistor has two control signals, cntlA and cntlB, and a data input. It also acts like a gateway, this time passing its output if cntlB is high and cntlA is low. Otherwise, the output is turned off. The format of the input is  $\langle cntlA, cntlB, data \rangle$  and the format of the output is  $\langle out \rangle$ . The pass-gate can then be described as follows:

```

DEFINE pass

!andg @ [notg@1,2,3]

END

```

In the implementation of the exclusive-OR, the outputs of the various circuit elements are 'wire-OR'ed together. Functionally, this situation can be described an 'OR'ing together of the outputs as long as one and only one output is active at any time. The format of the input is  $\langle inA, inB \rangle$  and the format of the output is  $\langle out \rangle$ .

```

DEFINE wor

org

```

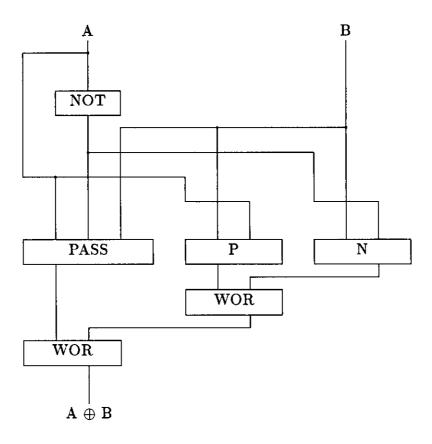

Now that all the circuit elements have been described, the description for the exclusive-OR can be shown. In the first line,  $\overline{A}$  is generated. A,  $\overline{A}$ , B are then routed to the various circuit elements. The outputs of these elements are then 'wired-OR'ed together in the last line. The format of the input is  $\langle A, B \rangle$  and the format of the output is  $\langle A, B \rangle$ .

```

DEFINE xor

!wor @

[pass,p@[3,1],n@[3,2]] @

[1,notg@1,2]

END

```

A block diagram of the FLAG design is given in Figure 3.2. The layout that is produced from this expression is shown in Figure 3.3. The layout for the hand design is shown in Figure 3.4. A comparison of the designs for a two input exclusive-OR gate is shown in Table 3.1.

Figure 3.2: Exclusive Or Logic Diagram: FLAG Design

| XOR           | FLAG              | Hand           |

|---------------|-------------------|----------------|

| Area          | $89 \times 205$   | $49 \times 72$ |

| White Space   | 66%               | 44%            |

| Average Delay | 4.3 ns            | 2.3 ns         |

| Maximum Delay | $4.5~\mathrm{ns}$ | 2.3 ns         |

| Design Time   | 1 hour            | 3 hours        |

Table 3.1: Exclusive Or Comparison

Figure 3.3: Exclusive-OR: FLAG layout

Figure 3.4: Exclusive-OR: Hand layout

#### 3.1.2 AND-OR Networks

In this subsection, an arbitrary AND-OR network will be designed. The boolean expression is:  $f(a, b, c) = (\overline{a}b) + (a\overline{b}c) + (b\overline{c})$  The hand implementation of this expression requires 9 logic gates: three inverters to form the complements of a, b, c, four 2-input AND-gates to form the product terms, and two 2-input OR-gates to form the final sums. A logic diagram for the circuit is shown in Figure 3.5.

The functional description of the network follows the boolean expression. First, the complement of the inputs is generated. Next, the various product terms are created and then 'OR'ed together in the last line.

```

DEFINE and-or(a,b,c)

!org @

[andg@[2@1,1@2],andg@[1@2,2@3],!andg@[1@1,2@2,1@3]] @

&[id,notg]

END

```

The layout that is produced from this FP description is shown in Figure 3.6.

For the hand design of the AND-OR network, we have a choice between using pass transistors or logic gates in the design. Logic gates were selected since an AND-OR network is being synthesized. The layout for the hand design is shown in Figure 3.7. A comparison of the designs for the AND-OR network is given in Table 3.2.

After closer examination of Table 3.2, we see that the FLAG version of the AND-OR network operated faster than the hand version. At first, this seems surprising; but upon closer examination of the designs, it becomes clear why this is so. The reason for the discrepancy in speed between the FLAG version of the AND-OR network and the hand version is due to the critical path of some of the product terms of the AND-OR network. Table 3.3 lists the critical paths for each product term of the AND-OR networks for both layouts. The term  $(\bar{a}b)$  is the one of interest. In the FLAG layout, the term  $(\bar{a}b)$  had a delay of three gate delays while undergoing four gate delays in the hand layout. This resulted in the FLAG circuit operating faster than the hand circuit.

Figure 3.5: AND-OR Logic Diagram: FLAG design

Figure 3.6: AND-OR: FLAG layout

Figure 3.7: AND-OR: Hand layout

| AND-OR        | FLAG             | Hand                 |

|---------------|------------------|----------------------|

| Area          | $162 \times 288$ | $163 \times 234$     |

| White Space   | 56%              | 55%                  |

| Average Delay | 14.1 ns          | 16.3 ns              |

| Maximum Delay | 16.5 ns          | 20 ns                |

| Design Time   | 10 minutes       | $2\frac{1}{3}$ hours |

Table 3.2: AND-OR Network Comparison

| Term             | FLAG          | Hand          |

|------------------|---------------|---------------|

| $\overline{a}b$  | 3 gate delays | 4 gate delays |

| $a\overline{b}c$ | 5 gate delays | 4 gate delays |

| $b\overline{c}$  | 4 gate delays | 4 gate delays |

Table 3.3: Critical Paths in AND-OR Network

#### 3.1.3 NAND Networks

In this subsection, an arbitrary NAND network will be designed. The boolean expressions were arbitrarily chosen and are:

$$f_1(a, b, c, d) = \overline{a}c + \overline{b}c + \overline{d}$$

$f_2(a, b, c, d) = \overline{a}\overline{b} + \overline{b}cd + abcd$

The implementation of these expressions requires 8 2-input NAND gates. By performing the following algebraic manipulations upon the expressions  $f_1$  and  $f_2$ , equations are created which are simpler to implement than the original expressions.

For

$$f_1(a, b, c, d)$$

:

$$\overline{a}c + \overline{b}c + \overline{d}$$

$$(\overline{a} + \overline{b})c + \overline{d}$$

```

For f_2(a, b, c, d):

\overline{a}\overline{b} + \overline{b}cd + abcd

\overline{a}\overline{b} + cd(\overline{b} + ab)

\overline{a}\overline{b} + a\overline{a} + cd(\overline{b} + ab)

\overline{a}\overline{b} + a\overline{a}(b + \overline{b}) + cd(\overline{b} + ab)

```

$$\overline{a}\overline{b} + a\overline{a}b + a\overline{a}\overline{b} + cd(\overline{b} + ab)$$

$$\overline{a}\overline{b} + a\overline{a}b + cd(\overline{b} + ab)$$

$\overline{a}(\overline{b}+ab)+cd(\overline{b}+ab)$

$(\overline{b} + ab)(\overline{a} + cd)$

The resulting expressions for  $f_1(a, b, c, d)$  and  $f_2(a, b, c, d)$  require 9 NAND gates to implement: three for  $f_1(a, b, c, d)$  and six for  $f_2(a, b, c, d)$ . A logic diagram for the NAND network is shown in Figure 3.9.

The functional description of the network follows the boolean expression.

```

DEFINE nand-network(a,b,c,d)

[ lins(nandg)@[1,2,3,4],

nandg @ [id,id] @ nandg @

[ lins(nandg)@[1,2,2], rins(nandg)@[1,3,4] ]

]

END

```

The layout that is produced from this FP description is shown in Figure 3.8.

For the hand design of the NAND network, we again have a choice between using transmission gates or logic gates in the design. Logic gates were selected since a NAND network is being synthesized. In the hand design, a single NAND gate can be removed since two of the NAND gates make use of the output of the same gate. This reduces the number of NAND gates required in the design to eight. The layout for the hand design is shown in Figure 3.10. A comparison of the designs for the test NAND network is given in Table 3.4.

Figure 3.8: NAND: FLAG layout

Figure 3.9: NAND Network Logic Diagram: Hand design

Figure 3.10: NAND: Hand layout

| NAND          | FLAG          | Hand                 |

|---------------|---------------|----------------------|

| Area          | 125 	imes 322 | $125 \times 241$     |

| White Space   | 54%           | 52%                  |

| Average Delay | 11.4 ns       | 10.3 ns              |

| Maximum Delay | 14 ns         | 14 ns                |

| Design Time   | 10 minutes    | $2\frac{1}{6}$ hours |

Table 3.4: NAND Network Comparison

#### 3.1.4 Concluding Remarks

As the three previous examples have shown, the hand layouts are smaller and a little faster than their FLAG produced counterparts, with the exception of the AND-OR network. The differences between the hand and FLAG layouts can be attributed to the fact that the designer was able to perform some optimization upon the hand versions of the circuits during the design cycle. Additionally, during the layout process, the designer could place and pack the circuit elements together in such a fashion as to minimize the total area used by the circuit and the delay of the circuit. The optimizations were made at the expense of the designer since additional time and effort had to be expended by the designer in order to perform the optimizations upon the hand design. In the FLAG produced circuits, the circuit elements were placed in a top to bottom fashion. This resulted in circuits that were larger and slower than their hand counterparts.

#### 3.2 MSI Modules

In this section, several MSI-level modules: a full adder, a multiplexor, an encoder, and a ripple carry adder are designed. The results are discussed in Sec. 3.2.5.

#### 3.2.1 Full Adder

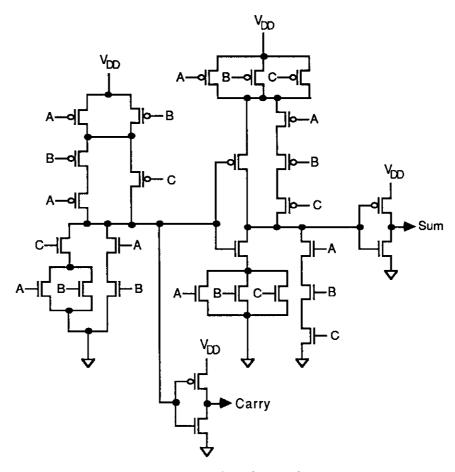

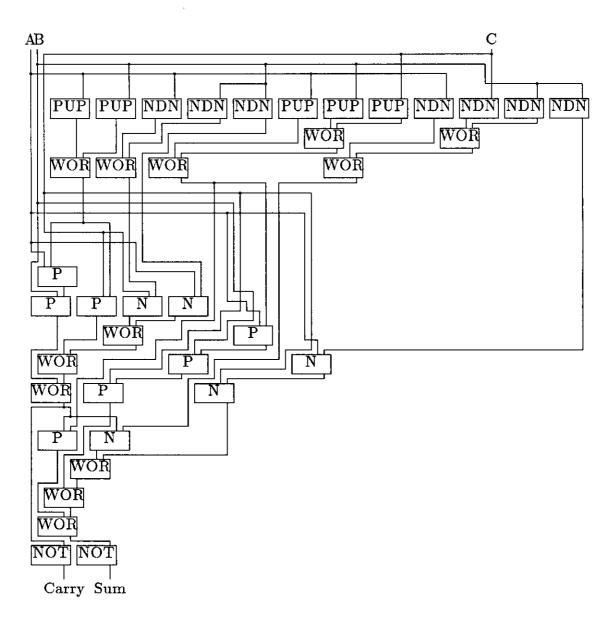

A full adder is a combinational circuit that takes three inputs and adds them together to produce a 2 bit vector: <carry, sum>. The switching expressions are

$$Sum = ABC + A\overline{BC} + \overline{ABC} + \overline{ABC}$$

$$Carry = AB + A(A + B)$$

A logic diagram for a full adder is given in Figure 3.11<sup>2</sup>. A transistor schematic for a full adder is given in Figure 3.12<sup>3</sup>. Since the carry out signal  $(\overline{Carry})$  is used in the generation of Sum, Sum will be delayed with respect to Carry. This facilitates the use of such a circuit in a n-bit ripple carry adder where the carry signal must "ripple" through the stages.

<sup>&</sup>lt;sup>2</sup>Weste, pp. 312.

<sup>&</sup>lt;sup>3</sup>Weste, pp. 312.

Figure 3.11: Full Adder Logic Diagram

Figure 3.12: Full Adder schematic

The FLAG description of the full adder is given below. The function fulladder takes a vector of three inputs and returns the sum of the inputs. The format of the input is  $\langle a \ b \ c \rangle$ . The format of the output is  $\langle Carry \ Sum \rangle$ . The function can be broken down into the following steps.

- 1. Connect up all pullup and pulldown transistors to the inputs according to the transistor schematic for the full adder.

- 2. Wire-OR the pullup and pulldown transistors together according to the transistor schematic for the full adder.

- 3. Connect up the n and p transistors to generate  $\overline{Carry}$  according to the transistor schematic for the full adder.

- 4. Connect up the n and p transistors to generate  $\overline{Sum}$  according to the transistor schematic for the full adder.

- 5. Complement  $\overline{Carry}$  and  $\overline{Sum}$ .

```

DEFINE full_adder

&notg @

[ 1, !wor@[ p@[1,2], 3, n@[1,4], 5 ] ]@

[ !wor@[ p@[2,p@[1,4]],

p@[3,4], n@[3,5],

n@[1,6]],

7,

p@[3,p@[2,p@[1,7]]],

8,

n@[3,n@[1,9]]

] @

[ 1,

2,

3,

wor@[4,5],

wor@[6,7],

8,

!wor@[9,10,11],

```

```

!wor@[12,13,14],

15

] @ concat @

[ id,

&Pup@[1,2],

&Ndn@[1,2,2],

&Pup@[1,2,3],

&Ndn@[1,3,2,2]

]

END

```

Since the design of the full adder makes use of pullup and pulldown transistors, functional descriptions of these circuit elements must be created.

Functionally, the pullup transistor returns a high signal (1) if its gate input is low and turns itself off otherwise. This can be described functionally as a 'Not'ing of the gate input. The format of the input is  $\langle gate \rangle$  and the format of the output is  $\langle out \rangle$ .

```

DEFINE Pup

notg

END

```

Functionally, the pulldown transistor returns a low signal if its gate input is high and turns itself off otherwise. This can be described functionally as an 'AND'ing together of the gate input and a low signal (0). The format of the input is  $\langle gate \rangle$  and the format of the output is  $\langle out \rangle$ .

```

DEFINE Ndn

andg @ [%0,id]

END

```

The function definitions for P, N, WOR can be found on pages 32 and 32.

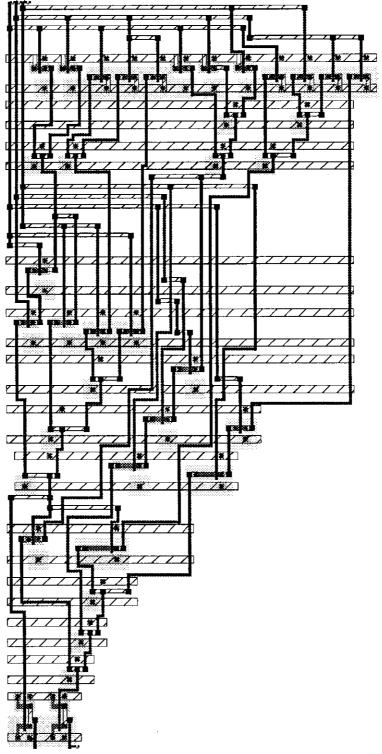

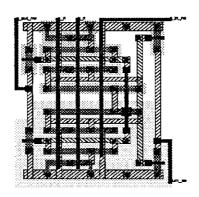

A block diagram of the FLAG design is given in Figure 3.13 The layout produced by the FP description for the full adder is shown in Figure 3.14 The layout produced from the hand design is shown in Figure 3.15. A comparison of the designs for the full adder is given in Table 3.5. Clearly, the FLAG design is inferior with respect to the hand design. The reasons for this are discussed in Sec. 3.2.5.

Figure 3.13: Full Adder Logic Diagram: FLAG design

Figure 3.14: Full Adder: FLAG layout

Figure 3.15: Full Adder: Hand layout

| Full Adder    | FLAG             | Hand           |

|---------------|------------------|----------------|

| Area          | $289 \times 594$ | $87 \times 17$ |

| White Space   | 65%              | 58%            |

| Average Delay | 23 ns            | 14 ns          |

| Maximum Delay | 30 ns            | 22 ns          |

| Design Time   | 2 hours          | 6 hours        |

Table 3.5: Full Adder Comparison

#### 3.2.2 Multiplexor

A multiplexor is a combinational system which performs a selection function. It takes N control inputs,  $\underline{\mathbf{c}} = \langle c_{N-1}, ..., c_0 \rangle$  and  $2^N$  data inputs,  $\underline{\mathbf{d}} = \langle d_{2^{N-1}}, ..., d_0 \rangle$ , each of which can consist of either a single bit vector or multiple bit vector. The output is selected as shown below:

$$Y = d_{\underline{c}}, \qquad \underline{c} = \sum_{i=0}^{N-1} c_i \times 2^i$$

In the multiplexor, the N control signals are first decoded. Each of these decoded control signals is then combined with each bit of the corresponding data vector and then OR'ed to produce the output.

In the design of the multiplexor, a choice between a logic gate implementation and a transmission gate implementation can be made. A transmission gate acts like a gateway; when it is turned on, data can pass through. When the gate is turned off, the output is in a high impedance state. This allows the output of multiple transmission gates to be connected together in a wired-OR fashion, avoiding the large AND-OR networks required for the logic gate implementation of the multiplexor. One drawback of transmission gates is that they require both the complemented and uncomplemented form of their respective control signals. The transmission gate design for the multiplexor was chosen. A logic diagram of the design of a two-input multiplexor is given in Figure 3.16.

The function  $\max^4$  takes two inputs, a vector of control inputs and a vector of data vectors and implements a selection function using the control inputs to choose one data vector to send as the output. The format for the input is  $<< Cntl_{N-1} \dots Cntl_0 > << d_{n-1}^{m-1} \dots d_0^{m-1} > \dots < d_{n-1}^0 \dots d_0^0 >>>$ . The format for the output is  $< d_{n-1}^i \dots d_0^i >$ ,  $0 \le i < m$ ,  $i = \sum_{j=0}^{N-1} Cntl_j \times 2^j$  The multiplexor function can be broken into the following steps.

- 1a Decode the control signals and generate their complements

- 1b Insure that the data is in the proper form

- 2 Route the decoded control signals to their respective data vectors

<sup>&</sup>lt;sup>4</sup>Worley, "Functional Style Description," pp. 86.

- 3a For each data vector, distribute its control signal across all its component bits

- 3b Route control and data signals to pass-gates

- 4 Connect together pass-gate outputs to form output vector

Since pass-gates require both the complement and uncomplemented version of its control signal, it is necessary to generate the complement of the decoded control signals. The outputs of the pass-gates are wire-OR'ed together so that the  $K^{th}$  bit of all the data vectors are connected together to form the  $K^{th}$  bit of the output and this is done for all the bits of the output.

The definition of the function wor can be found on page 32 and the function pass can be found on page 32.

The function **decode** takes a vector of arbitrary length and returns a fully decoded version of the input. The format of the input is  $\langle x_{n-1} \dots x_0 \rangle$ . The format of the output is  $\langle y_{2^n-1} \dots y_0 \rangle$ , where

$$y_k = \begin{cases} 1 & \text{if } \underline{X} = k \\ 0 & \text{otherwise} \end{cases}$$

The **decode** function can be broken into the following steps.

If (length of input = 1)

1 Perform a decode function upon a single bit

Else

- 1 Split the input into two vectors

- 2 Recursively apply decode to each vector to fully decode it

- 3 Form all possible pairs from the two decoded vectors

- 4 Reduce pairs to single bit vectors

```

DEFINE decode

IF (length = 1)

THEN decode_1@1

ELSE

&andg @

cross_match @

&decode @

split

ENDIF

END

```

The function decode\_1 takes an input of a single-bit and returns a fully decoded version of the input. The format of the input is  $\langle x \rangle$ . The format of the output is  $\langle x \rangle$ .

```

DEFINE decode_1

[id, notg]

END

```

The function cross\_match takes an input of two vectors of arbitrary length and returns a vector containing all the possible pairs that can be formed from the input. The format of the input is  $<< x_{2^{\frac{n}{2}}-1} \dots x_0 >< y_{2^{\frac{n}{2}}-1} \dots y_0 >>$ . The format of the output is  $<< x_{2^{\frac{n}{2}}-1} \ y_{2^{\frac{n}{2}}-1} > \dots < x_{2^{\frac{n}{2}}-1} \ y_0 >< x_{2^{\frac{n}{2}}-2} \ y_{2^{\frac{n}{2}}-2} > \dots < x_0 \ y_0 >>$ .

```

DEFINE cross_match

concat @

&distl @

```

distr

END

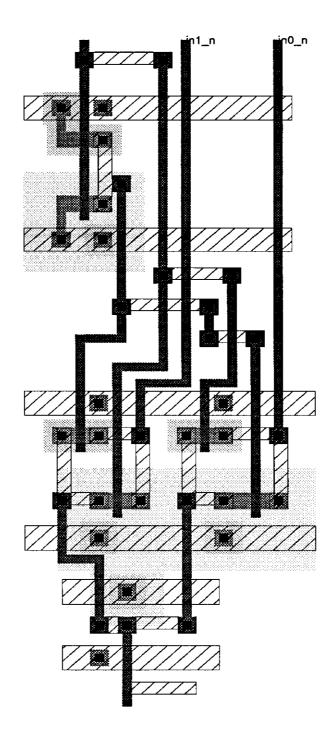

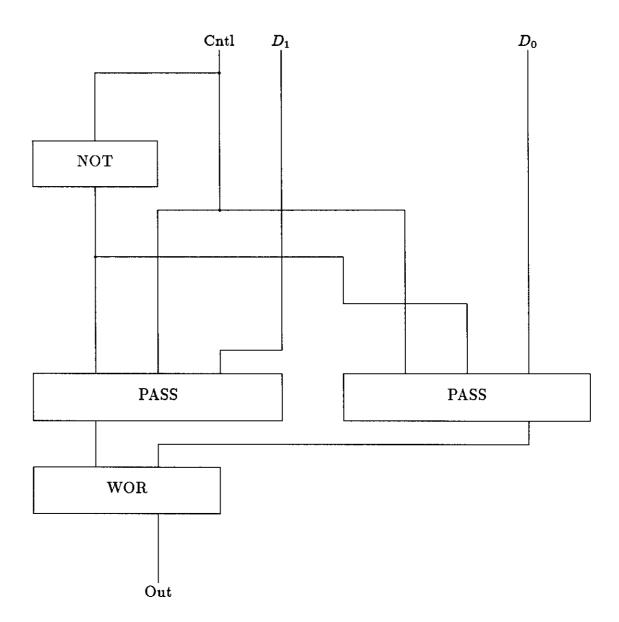

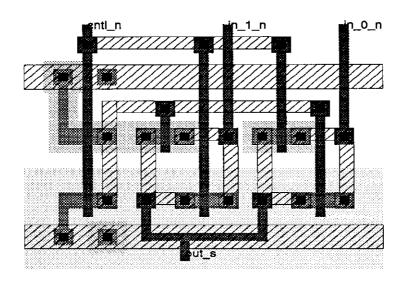

The layout produced from the FP expression is shown in Figure 3.17. The logic diagram of the hand design of a multiplexor is given in Figure 3.18. The layout for the hand design is shown in Figure 3.19. A comparison of the designs for the multiplexor is given in Table 3.6.

Figure 3.16: 2-Input Multiplexor Logic Diagram: FLAG design

Figure 3.17: 2-Input Multiplexor: FLAG layout

Figure 3.18: 2-Input Multiplexor Logic Diagram: Hand design

Figure 3.19: 2-Input Multiplexor: Hand layout

| Multiplexor   | FLAG            | Hand           |

|---------------|-----------------|----------------|

| Area          | $63 \times 165$ | $74 \times 61$ |

| White Space   | 57%             | 53%            |

| Average Delay | 2.5 ns          | 1.3 ns         |

| Maximum Delay | 4 ns            | 2 ns           |

| Design Time   | 30 minutes      | 2 hours        |

Table 3.6: Multiplexor Comparison

### 3.2.3 Encoder

An encoder is a combinational system which performs an encoding function upon  $2^N$  inputs  $\underline{X} = (x_{2^N-1}, ..., x_0)$  to produce a N-bit output vector,  $\underline{Y} = (y_{N-1}, ..., y_0)$ . Only one of the  $2^N$  inputs can be true at any time and  $\underline{Y}$  represents the index of the input line that is true as a binary number. A high level description of an encoder is:

$$\underline{Y} = i \quad \text{if } x_i = 1$$

$$\underline{Y} = \sum_{j=0}^{N-1} y_j 2^j$$

An encoder is typically implemented as a collection of OR-gates. Each bit of the output examines a set of  $2^{N-1}$  of the input lines. If any of the input lines within a set is true, then the output bit associated with that set is true. The set of inputs examined by each output bit varies with bit position. An algorithm for determining the coverage sets is given below.

For the  $K^{th}$  bit of the output (0 is the least significant position).

- Divide the inputs into groups of size  $2^K$

- 'OR' together the 1<sup>st</sup>, 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup>, ... groups starting with the most significant group.

- Result is the K<sup>th</sup> bit of the output.

For the  $(K+1)^{th}$  bit of the output (0 is the least significant position).

- Pair off the groups created for the  $K^{th}$  bit position starting with the most significant group.

- Concatenate the pairs to form new groups of  $2^{(K+1)}$  size.

- 'OR' together the 1<sup>st</sup>, 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup>, ... groups starting with the most significant group.

- Result is the  $(K+1)^{th}$  bit of the output.

A logic diagram for the design of an eight-bit encoder is given in Figure 3.20.

The function **encoder**<sup>5</sup> takes an input of  $2^N$  inputs and performs an encoding function upon them to generate a N-bit output vector. The format of the input is  $\langle x_{2^{2n}-1} \dots x_0 \rangle$ . The format of the output is  $\langle y_{n-1} \dots y_0 \rangle$ . In the functional description, the input is converted into a collection of vectors if it isn't already and the function **encode\_bits** is called.

```

DEFINE encoder

encode_bits ©

&(IF (input is an atom))

THEN [id]

ELSE id

ENDIF

```

The function **encode\_bits** takes a collection of vectors and recursively applies the encoding algorithm presented earlier to generate the output. The format of the input is  $\langle x_{2^{2n}-1} \rangle \ldots \langle x_0 \rangle \rangle$ . The format of the output is  $\langle y_{n-1} \ldots y_0 \rangle$ . The operation of the function can be broken into the following steps.