# Computer Science Department Technical Report University of California Los Angeles, CA 90024-1596

### DISTRIBUTED DATA BASE MANAGEMENT FOR REAL-TIME BMD APPLICATIONS

Wesley W. Chu

M. T. Lan

K. K. Leung

R. C. Lee

M. A. Merzbacher

September 1987 CSD-870059

|   | t . |   |  |

|---|-----|---|--|

|   |     | • |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

| • |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

|   |     |   |  |

## DISTRIBUTED DATA BASE MANAGEMENT FOR REAL-TIME BMD APPLICATIONS

#### FINAL REPORT FOR THE PERIOD

FROM: May 28, 1986

TO: Sept. 30, 1987

Contract No. DASG60-85-C-0059

Prepared For:

US Army Strategic Defense Command

Huntsville, Alabama 35807

Sept. 30, 1987

University of California, Los Angeles

Wesley W. Chu, Principal Investigator

Researchers: M.T. Lan, K.K. Leung, R.C. Lee,

M.A. Merzbacher, C.M. Sit

The views, opinions, and/or findings contained in this report are those of the authors and should not be construed as an official Department of the Army position, policy or decision, unless so designated by other official documentation.

| • | • |   |  |

|---|---|---|--|

|   |   | • |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

#### **Table of Contents**

| CHAPTER I: INTRODUCTION AND SUMMARY I-1                                                                            |

|--------------------------------------------------------------------------------------------------------------------|

| CHAPTER II:                                                                                                        |

| 2.1 MODULE ASSIGNMENT AND PRECEDENCE RELATIONS FOR DISTRIBUTED REAL-TIME SYSTEMS                                   |

| 2.2 MODULE ASSIGNMENT FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS                                                 |

|                                                                                                                    |

| CHAPTER III: A BATCH SERVICE SCHEDULING ALGORITHM WITH TIME-OUT FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS III-1 |

| CHAPTER IV: TESTBED-BASED VALIDATION OF DESIGN TECHNIQUES IV-1                                                     |

| CHAPTER V: PERFORMANCE OF CONCURRENCY CONTROL ALGORITHMS FOR REAL-TIME DISTRIBUTED DATABASE SYSTEMS                |

| CHAPTER VI: A KNOWLEDGE ACQUISITION METHODOLOGY FOR SEMANTIC QUERY PROCESSING                                      |

| DISTRIBUTION LIST                                                                                                  |

|  | ı |   |  |

|--|---|---|--|

|  |   | • |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

### CHAPTER I

### INTRODUCTION AND SUMMARY

#### INTRODUCTION AND SUMMARY

During the past year, we have concentrated our efforts in the following areas of distributed systems: module assignment and scheduling for distributed systems, testbed validation of design techniques, performance of concurrency control algorithm for distributed database systems, and query processing with domain semantic.

#### 1.0 Module Assignment for Real-Time Distributed Processing Systems

Module assignment is a key issue that effects system performance in distributed systems. Response time is intimately related with module assignment. Therefore, we shall use response time as a performance measure in our research. We have investigated two related areas. The first area considers the module precedence effect on module assignment, and the second considers the replicated module assignment to provide load balance and improves response time.

## 1.1 Module Assignment and Precedence Relations for Distributed Real-Time Distributed Systems

It is well known that module assignment should consider module precedence relationships. However, most of the published task allocation work has not considered the precedence effect. This motivates us to study and understand the effects of precedence relationship (PR) among program modules on response time. A new loading function that includes the Intermodule Communication (IMC) and Accumulative Execution Time (AET) of each module is also proposed. Our study reveals that minimizing the most heavily loaded (bottleneck) processor is a good principle for module assignment. Further, the PR module effect can also be integrated into

the above assignment principle. When module PR is considered in the task assignment, it yields better performance than without considering the PR effect. Detailed results are summarized in Chapter 2.

#### 1.2 Module Replication and Assignment for Real-Time Distributed Systems

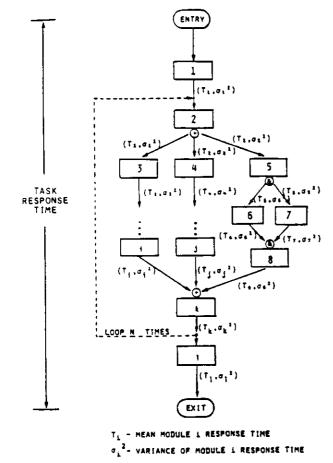

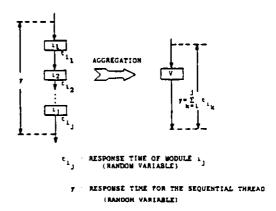

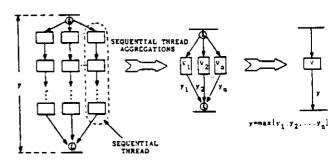

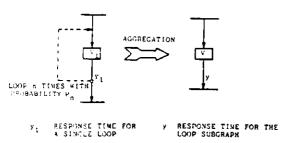

An analytical model is developed to estimate the task response time of distributed systems. The model considers such factors as interprocessor communications, module precedence relationship, module scheduling, interconnection network delay, and assignment of modules and files to computers. A heuristic algorithm for module assignment is developed to iteratively search for module assignments which provide shorter task response times. Assigning replicated modules may reduce task response time. Therefore, the algorithm also considers module replications. Using the sum of task response time and penalty delay for the violations of specified thread response time requirements as the objective function, an "optimal" module multiplicity and module allocation can be determined by the proposed algorithm. The detailed model and algorithm are presented in Chapter 2.

Our study reveals that the task response times for a given module assignment (with replications) generated by the algorithm compare closely with that of the simulation and exhaustive search. A series of experiments is also performed to characterize the behavior of the algorithm.

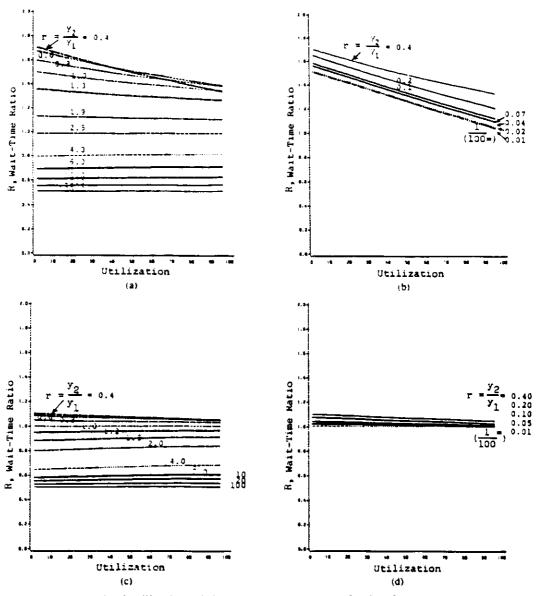

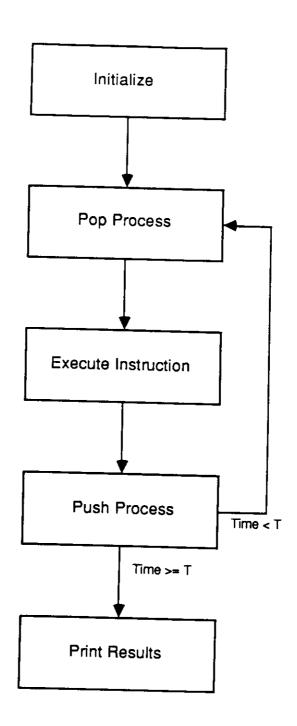

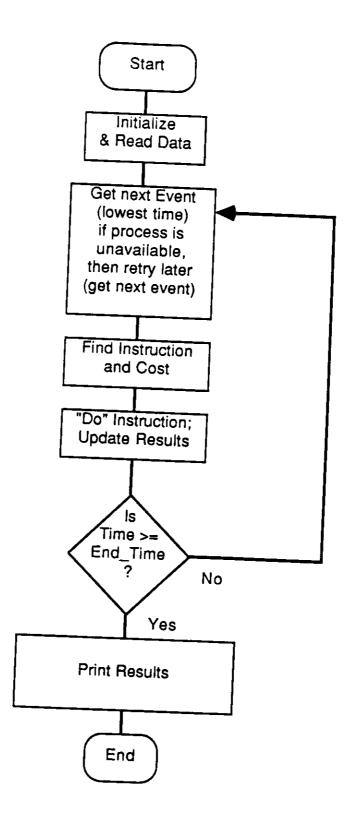

## 2.0 A Batch Service Scheduling Algorithm with Time-Out for Real-Time Distributed Processing Systems

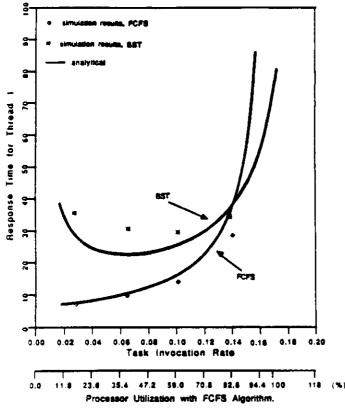

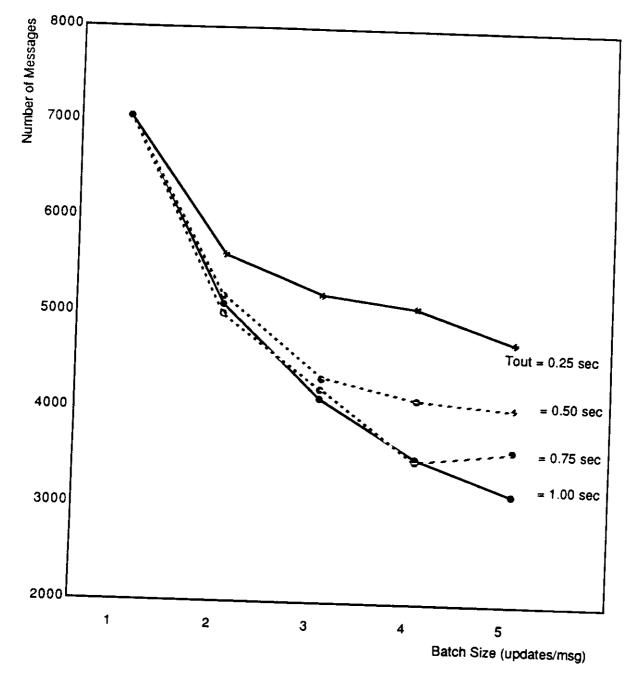

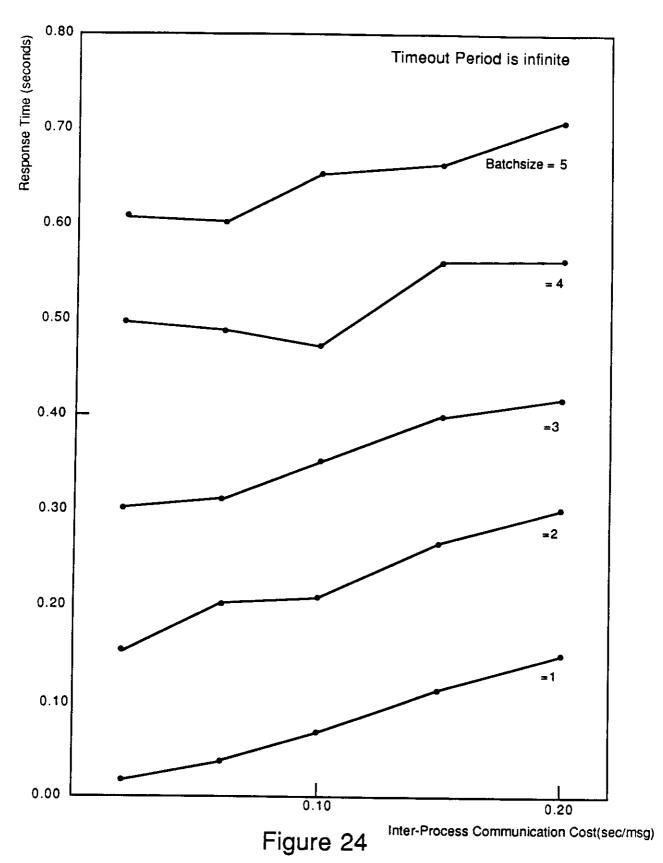

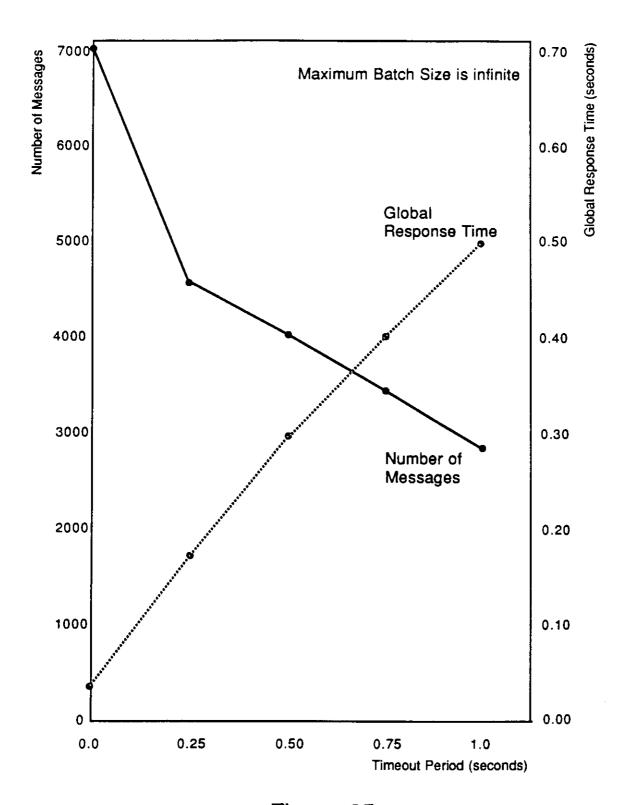

A new scheduling algorithm for reducing overhead and thus response time is proposed for distributed processing systems. The algorithm groups several module invocations into a

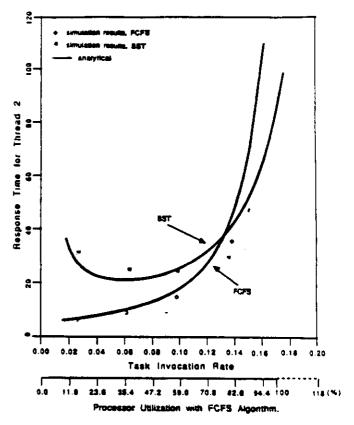

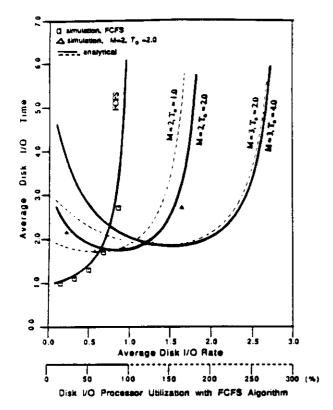

batch and processes them together to reduce certain scheduling overhead. A time-out clock is used to avoid excess delay in forming a batch. The clock is set when the first invocation arrives at the batch queue. The batch is formed when either the number of invocations reaches the prespecified maximum batch size or the time-out period ends. We denote this scheduling algorithm Batch Service with Time- out (BST). An analytical model is developed to estimate response time for this scheduling algorithm. The response time of a module using the BST algorithm depends on the invocation rate, scheduling overhead, execution time, maximum batch size, and time-out period. The assumptions used in the model are validated by simulations.

Comparing performance of a system using BST with that of using first-come-first-served (FCFS) scheduling algorithm, we note that the amount of improvement depends on the ratio of the fixed scheduling overhead to the incremental scheduling overhead. At heavy invocation rates, more batches will be formed when using the BST algorithm, therefore fixed scheduling overhead is reduced and more response time improvement can be achieved (See Chapter 3). As a result of reduction in overhead, the system using BST provides more capacity than that of using FCFS.

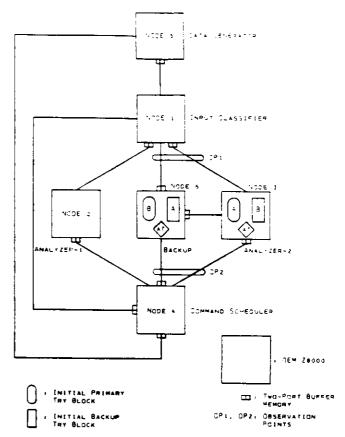

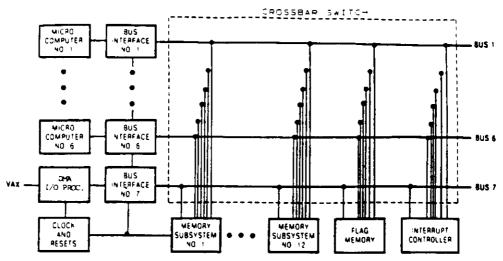

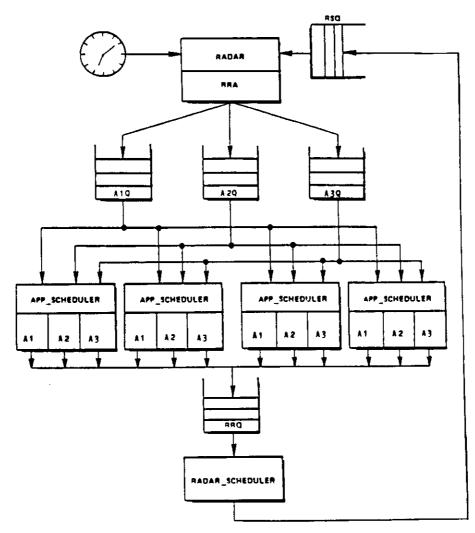

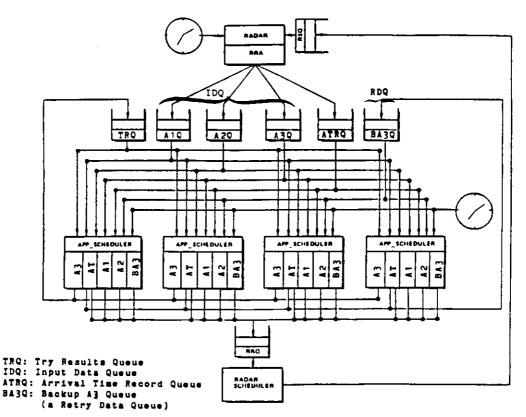

#### 3.0 Testbed-Based Validation of Design Techniques

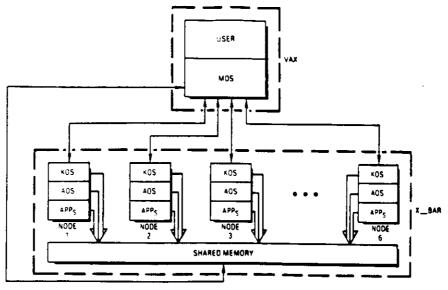

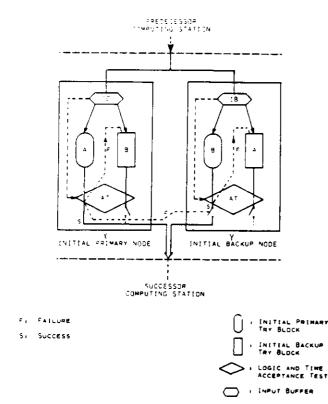

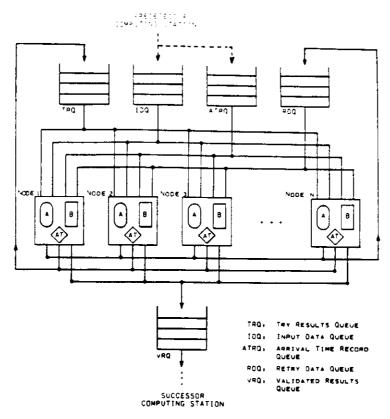

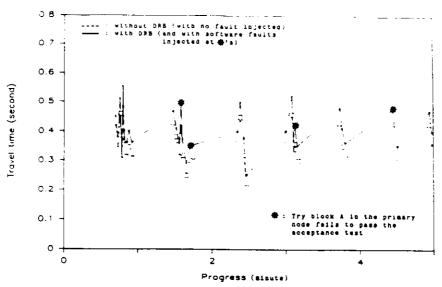

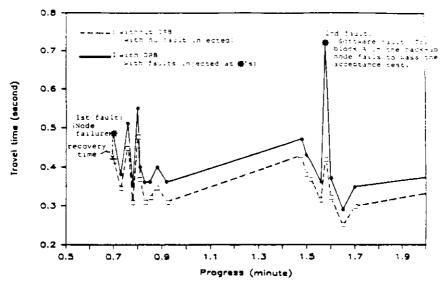

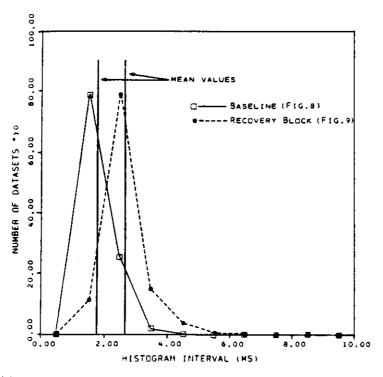

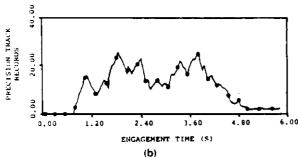

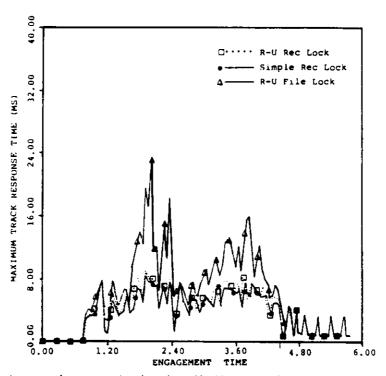

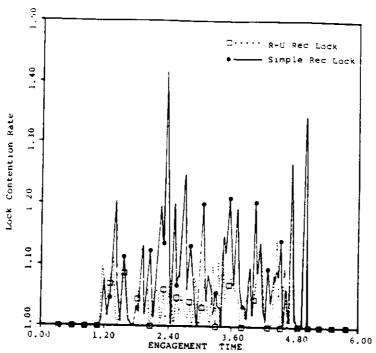

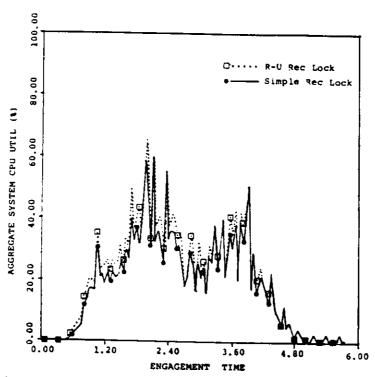

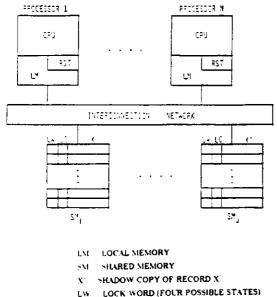

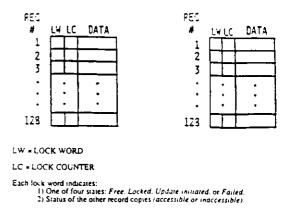

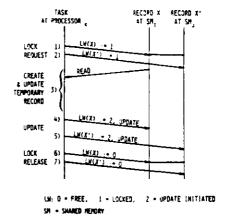

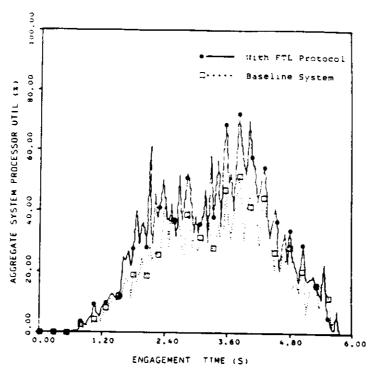

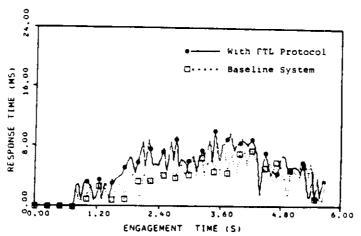

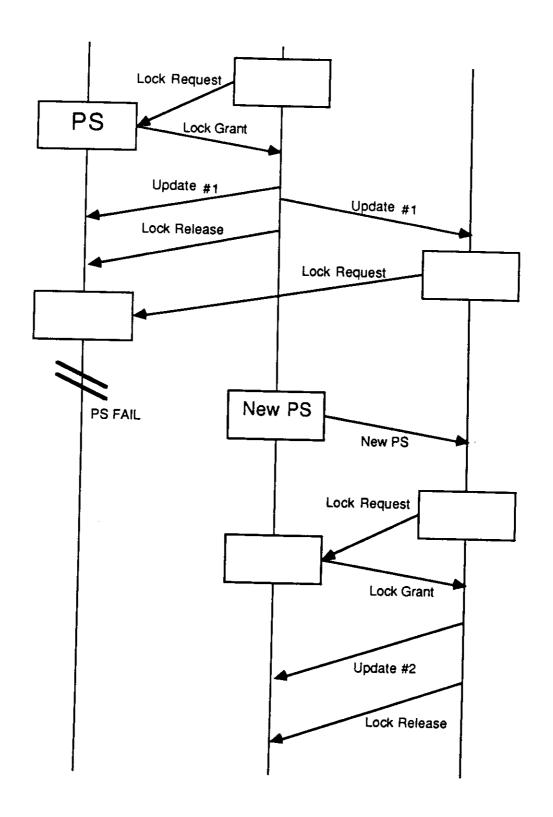

During the past three years, we have been jointly working with Unisys SDC at Huntsville to study and develop design methodology for tightly coupled distributed systems. Experimentation on the testbed provides us with insights on algorithm behavior. We have developed a fault tolerant locking (FTL) algorithm for the tightly coupled multiple processing system [1], designed the experiments, and studied its feasibility and performance. Experimental results reveal that the FTL is capable of detecting a processor failure during update and recovering data inconsistency among replicated copies. The overhead for performing the fault-tolerant locking

protocol depends on the lock frequency and its application. The parameters that may affect system performance are: time-out period, lock granularity (record or a group of records), and lock protocol (e.g., exclusive lock for write and shared for read, or reserve, upgrade, or exclusive lock).

We have also used the testbed for studying the performance of lock granularity (e.g. record, file) and the performance of reserve-upgrade locking protocol. Because of the read/write pattern of the radar tracking application, the results reveal that simple record locking provides better response time than file locking and reserve-upgrade locking. The detailed results are summarized in Chapter 4.

## 4.0 Performance of Concurrency Control Algorithms for Real-Time Distributed Database Systems

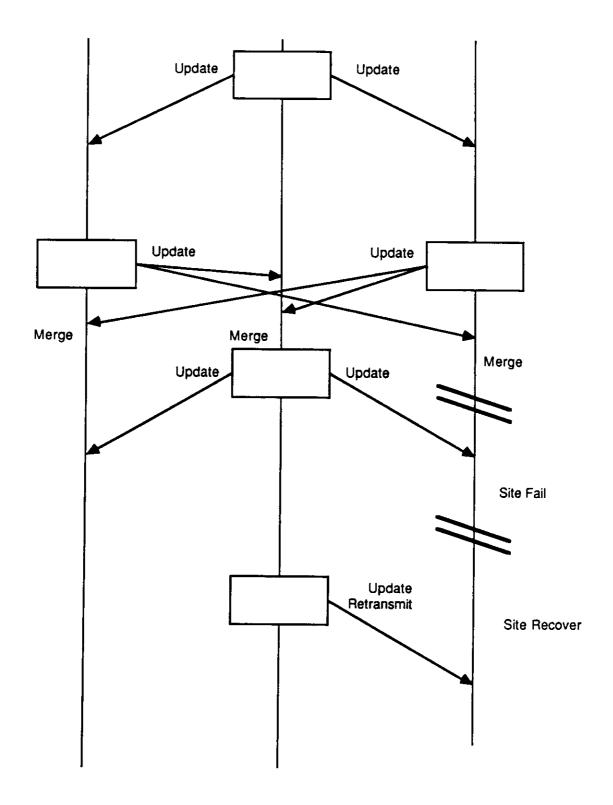

The survivability of distributed systems can be improved with multiple copies of files. When an update is performed on a copy, the update should be written on all other file copies. If the computer that is handling the update fails during the update process, all the copies may not be updated, resulting in mutual inconsistency.

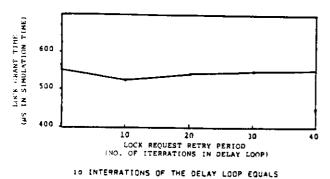

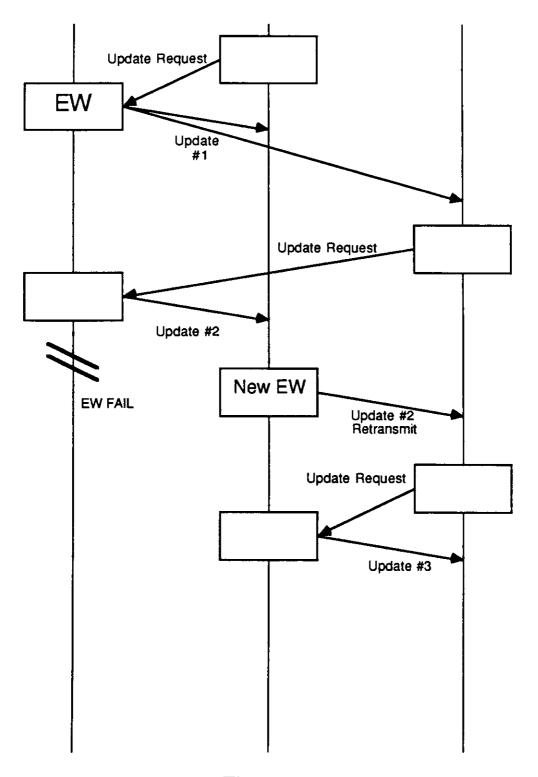

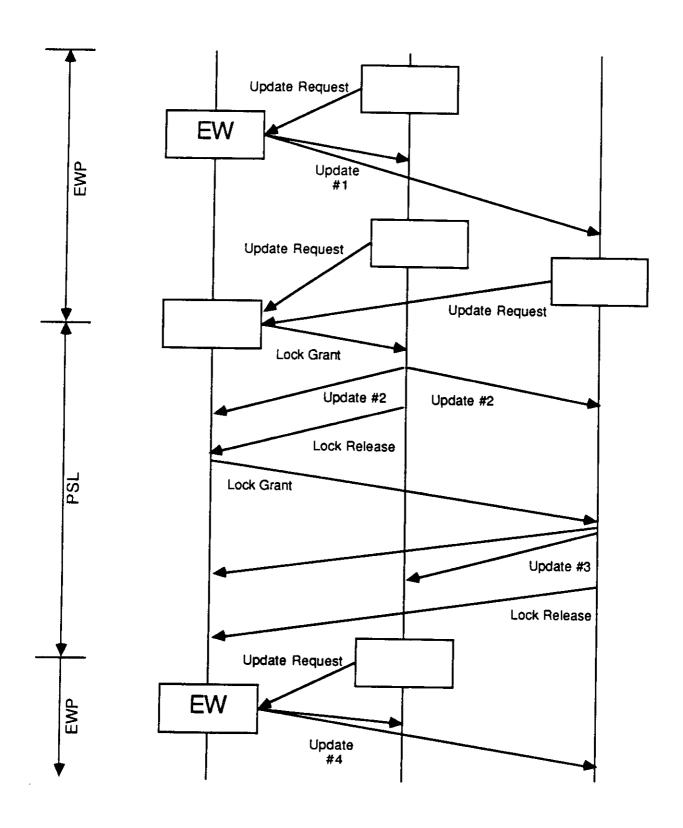

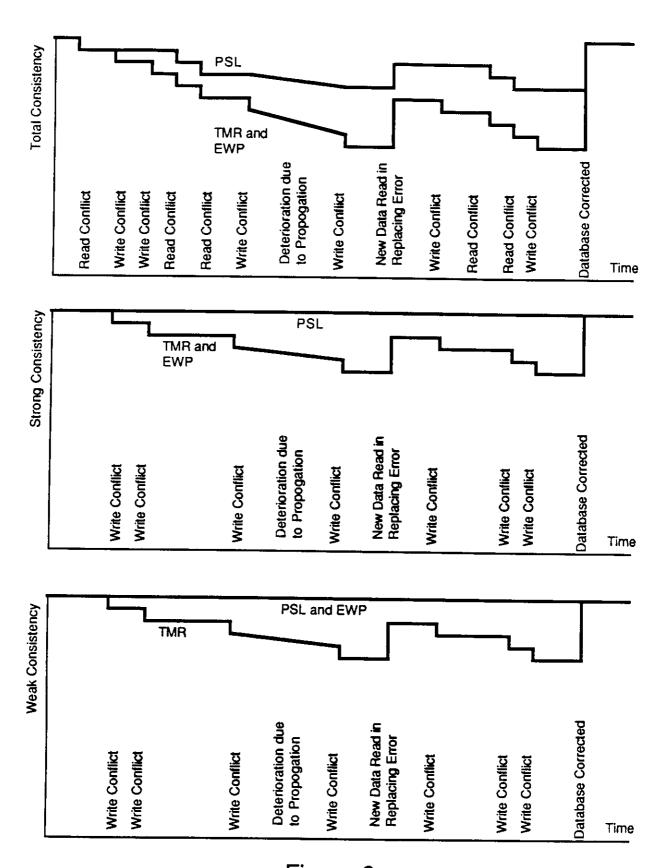

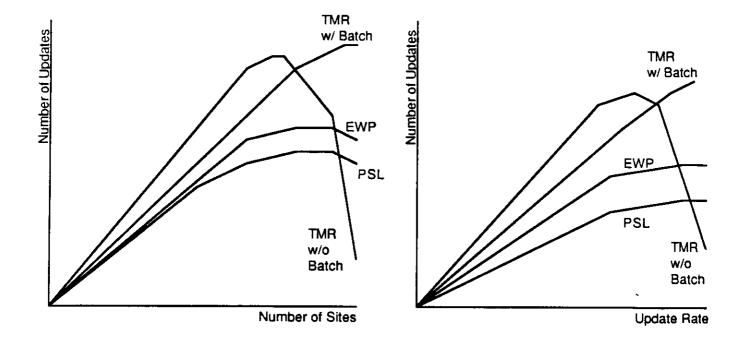

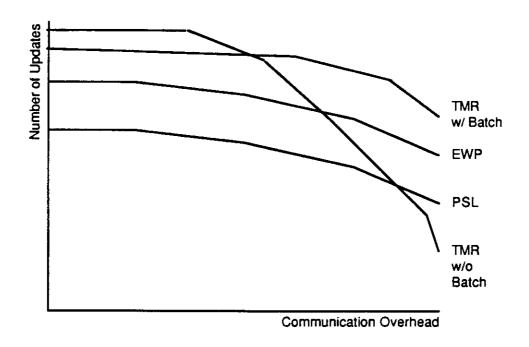

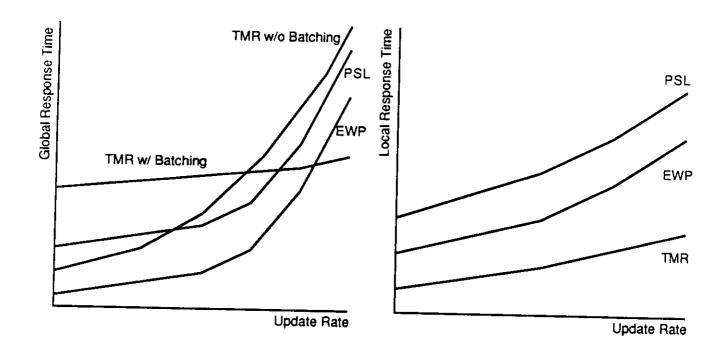

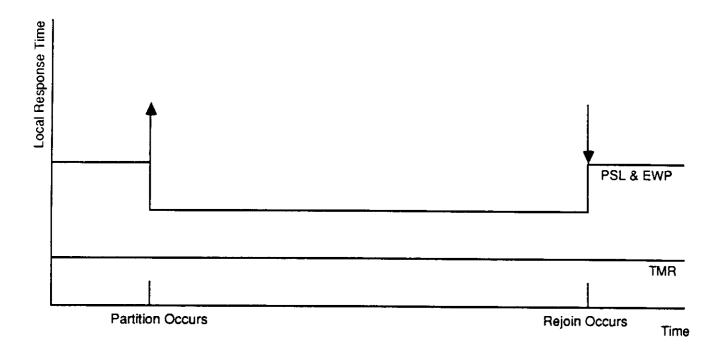

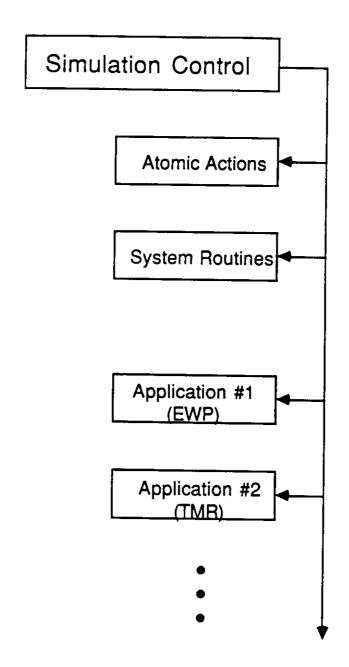

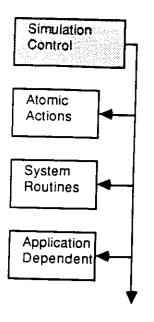

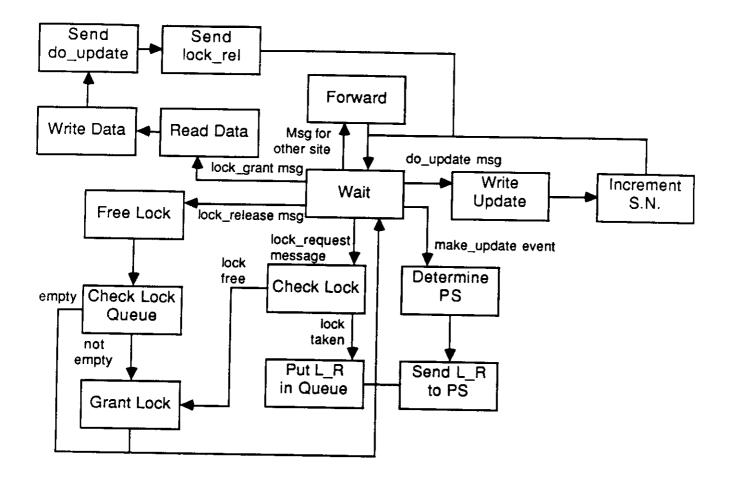

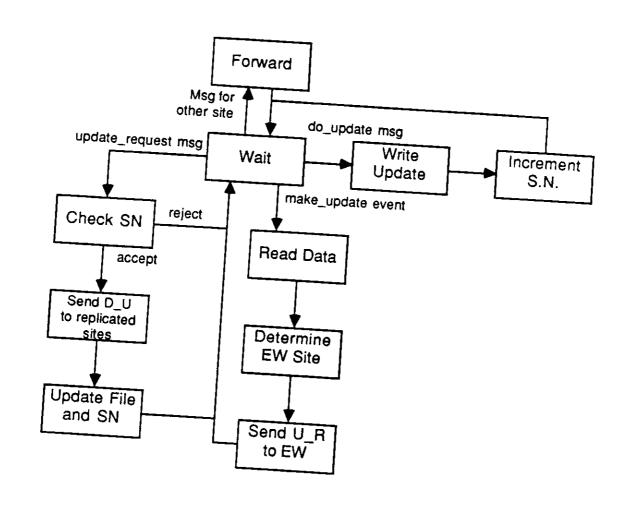

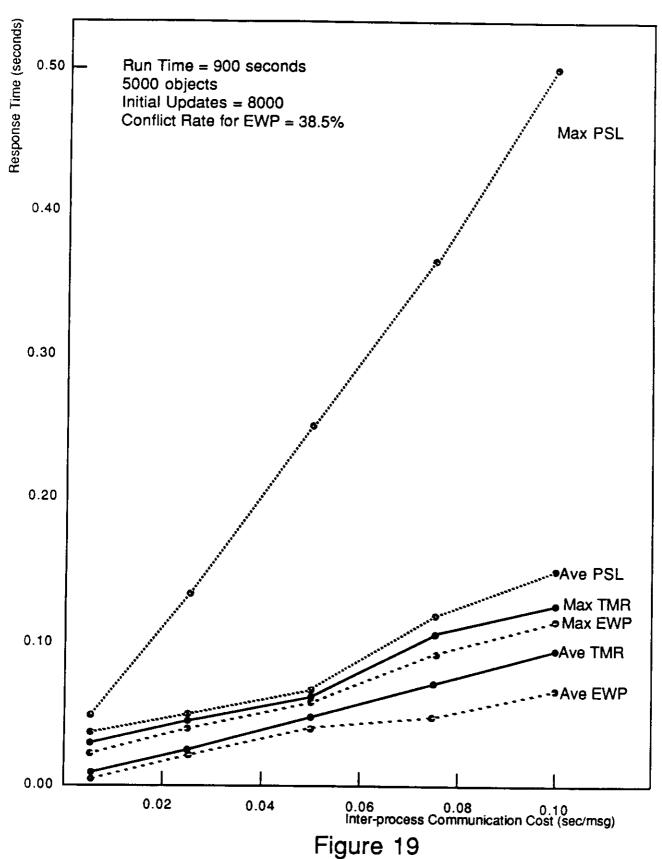

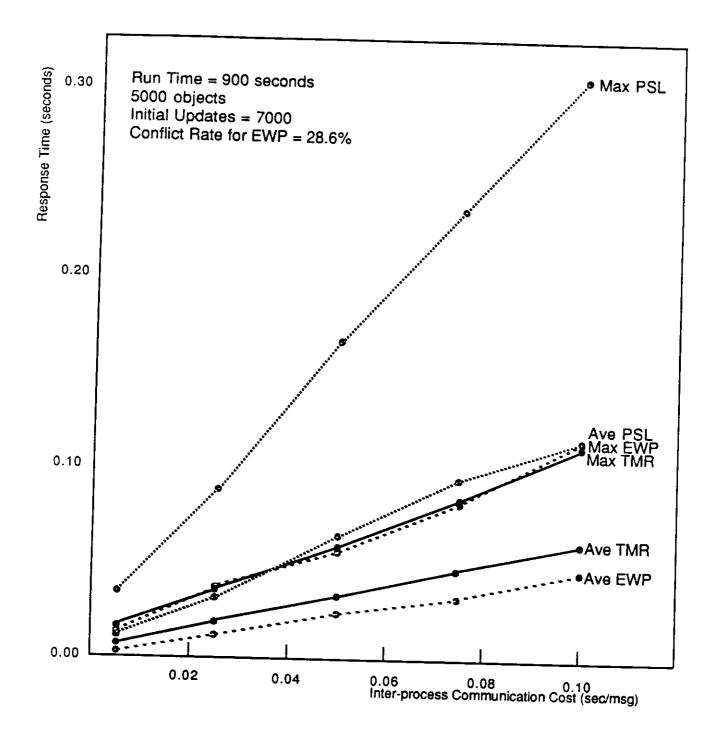

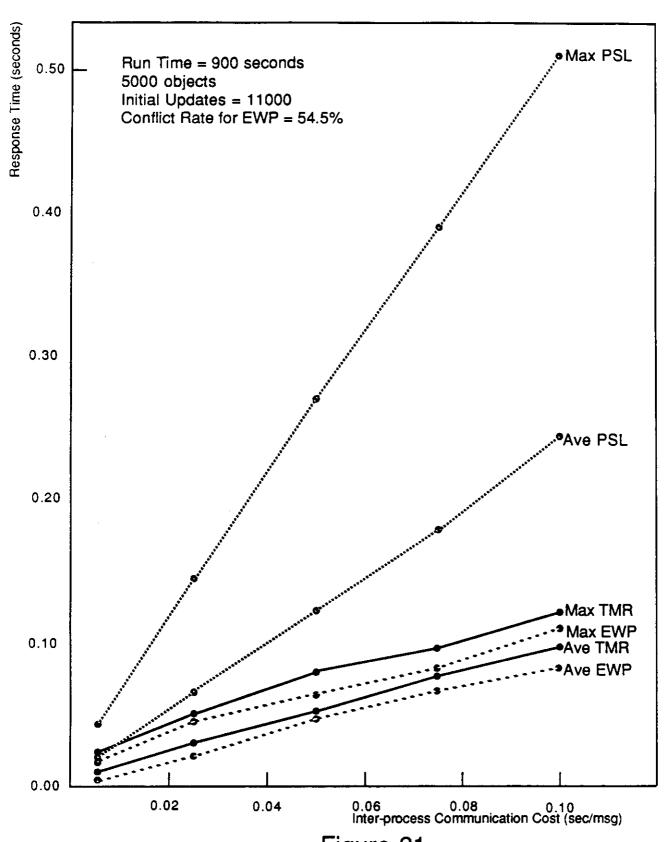

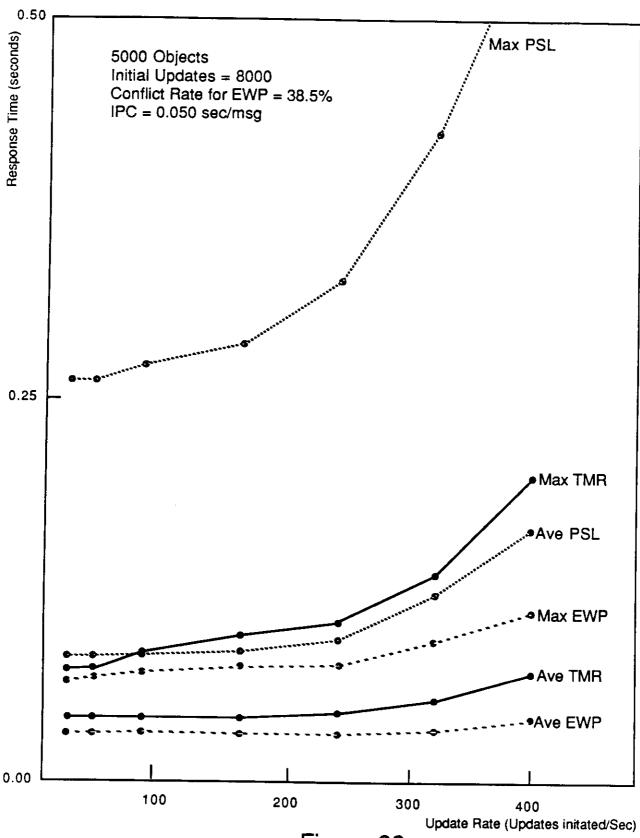

To study the different concurrency control techniques, we introduced new performance measures such as accuracy and weak consistency for characterizing the performance for data consistency. We have experimentally studied three types of protocols via simulation: Primary Site Locking (PSL) [2], Exclusive Writer Protocol (EWP) [3], and Time Stamp with modified Rollback (TMR) [4] and compared their performance in terms of response time, communication overhead, query rate, update/query ratio, consistency, and accuracy. Detailed discussions are given in Chapter 5. Protocols that assure weak consistency yield better performance (response time) than those assuring strong consistency. The data consistency requirement for different

types of data is application dependent. Further, it also depends on how the data is used for decision making. It is possible that when data state is x, weak consistency is sufficient. While data state becomes y, strong consistency is required.

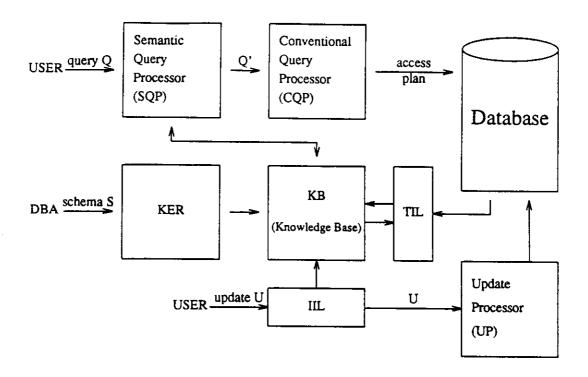

### 5.0 A Methodology of Knowledge Acquisition for Semantic Query Processing

Query processing is a key consideration in database management systems. Conventional approach uses a domain-independent approach for query processing design. Queries are transformed algebraically to determine the optimal access plan for retrieving the answer. Semantic query optimization uses a set of integrity constraints and reasoning to transform a given query into a different but more efficient query yet yields the same answer. It has been shown that this technique has great promise for improving system performance. However, knowledge acquisition problem needed to be solved before this technique can be of practical use.

Data modelling provides a useful tool for database design and usage. Conventional data models such as hierarchical, network, and relational models provide a record-based data structure for modelling database application. However, because of the lack of expressiveness of the conventional data models in modelling various database applications, semantic data models have been developed to provide a rich set of semantic constructs to describe various situations of the application. Database designer then uses his knowledge about the application to define the database schema. Most of the semantic data models focus only on providing structural specification and ignore the importance of knowledge for designing the database. However, this knowledge is very useful to semantic query processing and should be saved and used in query processing.

In this research, a semantic data model is developed that provides a knowledge specification capability associated with the semantic constructs for schema specification. This data model provides not only the necessary semantic expressive capability to model various

database applications, but also specifies domain knowledge which can be used to improve query processing performance. A knowledge acquisition tool is developed for systematically collecting useful domain knowledge for semantic query processing. A semantic database management system (SDBMS) is proposed that integrates semantic data modelling with semantic query processing. SDBMS provides facilities to systematically acquire semantic knowledge and use them to improve query processing. Detailed discussions are given in Chapter 6.

#### References

- [1] Chu, Wesley W. and Jung Min An, "Fault Tolerant Locking (FIL) for Tightly Coupled Systems," Proceedings of the 5th Symposium on Reliability in Distributed Software and Database Systems, Los Angeles, California, January 13-15, 1986.

- [2] Stonebraker, Michael, "Concurrency Control and Consistency of Multiple Copies of Data in Distributed INGRES," *IEEE Transactions on Software Engineering*, vol. SE-5, no. 3, pp. 188-194, May, 1979.

- [3] Chu, Wesley W. and Joseph Hellerstein, "The Exclusive Writer Approach to Updating Replicate Files in Distributed Processing Systems," *IEEE Transactions on Computers*, pp. 489-500, June, 1985.

- [4] Jajodia, Sushil and Catherine A. Meadows, "Mutual Consistency in Decentralized Distributed Systems," *Proceedings Third International Conference on Data* Engineering, vol. 3, pp. 396-404, IEEE, 1987.

|  | 1 |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

#### CHAPTER II

# 2.1 MODULE ASSIGNMENT AND PRECEDENCE RELATIONS FOR DISTRIBUTED REAL-TIME SYSTEMS

| · |   |

|---|---|

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   | • |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

# Task Allocation and Precedence Relations for Distributed Real-Time Systems

WESLEY W. CHU, FELLOW, IEEE, AND LANCE M-T. LAN, MEMBER, IEEE

Abstract—In a distributed processing system with the application software partitioned into a set of program modules, allocation of those modules to the processors is an important problem. This paper presents a method for optimal module allocation that satisfies certain performance constraints. An objective function that includes the intermodule communication (IMC) and accumulative execution time (AET) of each module is proposed. It minimizes the bottleneck-processor utilization-a good principle for task allocation. Next, the effects of precedence relationship (PR) among program modules on response time are studied. Both simulation and analytical results reveal that the program-size ratio between two consecutive modules plays an important role in task response time. Finally, an algorithm based on PR, AET, and IMC and on the proposed objective function is presented. This algorithm generates better module assignments than those that do not consider the PR effects.

Index Terms.—Distributed processing, intermodule communication (IMC), interprocessor communication (IPC), minimum bottleneck, module assignment, parallel processing, precedence relationship (PR), real-time systems, response time, task allocation algorithms.

#### I. INTRODUCTION

Aseveral orders of magnitude in recent decades, the demand for computing capacity increases at an even faster pace. The required processing power for many real-time applications cannot be achieved with a single processor. One approach to this problem is to use distributed data processing (DDP) that concurrently processes an application program on multiple processors. If properly designed and planned, DDP provides a more economical and reliable approach than that of centralized processing systems.

Task partitioning and task allocation are two major steps in the design of DDP systems. If these steps are not done properly, an increase in the number of processors in a system may actually result in a decrease of the total throughput [5]. Assuming the software for an application (a task) has been partitioned into a set of program modules (or subroutines), in this paper we study how to optimally allocate these modules to the set of processors in the DDP system.

Manuscript received September 10, 1985; revised August 11, 1986. This work was supported by the Ballistic Missile Defense Advanced Technology Center under Contracts DASG60-79-C-0087 and DASG60-83-C-0019.

W. W. Chu is with the Department of Computer Science, University of California, Los Angeles, CA 90024.

L. M-T. Lan was with the Department of Computer Science, University of California, Los Angeles, CA 90024. He is now with the Cellular Telecommunications Laboratory, AT&T Bell Laboratories, Whippany, NJ 07981.

IEEE Log Number 8713985.

First, we shall present two important parameters for task allocation: intermodule communication (IMC) and accumulative execution time (AET) of each module. The load of a processor consists of AET and IMC. We propose an objective function for task allocation that is based on minimizing the load on the most heavily loaded processor ("bottleneck"). The precedence relation (PR) among program modules, that specifies the execution sequence of the modules, is another parameter that affects module assignment. It is studied analytically and experimentally. A series of experiments are presented which reveal that the program-size ratio between two consecutive modules plays an important role in determining whether two modules should be colocated. An analytical model is developed that enables us to decide whether to assign consecutive modules to the same processor. Finally, a heuristic algorithm is developed that considers PR, IMC, and AET to search for the minimum-bottleneck assignment. Examples are given to illustrate the performance of the algorithm and also the improvement that may be obtained when considering PR in task allocation.

#### II. A New Objective Function for Task Allocation

In this section we shall first describe the two important parameters, AET and IMC, for task allocation. An objective function based on these parameters that minimizes system bottleneck is proposed. Then, we present the behavior of the proposed objective function.

#### A. IMC and AET

The AET for module  $M_j$  during time interval  $(t_h, t_{h+1})$  is the total execution time incurred for this module during that time interval, i.e.,

$$T_i(t_h, t_{h+1}) = N_i(t_h, t_{h+1}) y_i(t_h, t_{h+1})$$

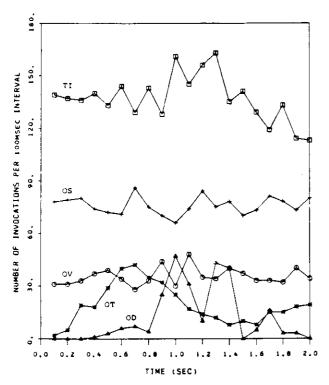

where  $N_j(t_h, t_{h+1})$  = number of times module  $M_j$  executes during  $(t_h, t_{h+1})$ , and  $y_j(t_h, t_{h+1})$  = average execution time of  $M_j$  during  $(t_h, t_{h+1})$ . Both the  $y_j$  and the AET  $T_j$  can be expressed in units of machine language instructions (MLI). Although the execution time of a machine language instruction varies from one instruction to another, based on a given instruction mix we can use the *mean* instruction execution time. Our study reveals that both the number of module executions and the AET are almost independent of module assignments when the load offered to the system is fixed. For example, the AET's produced by five different assignments for a module in a space-defense application, the Distributed

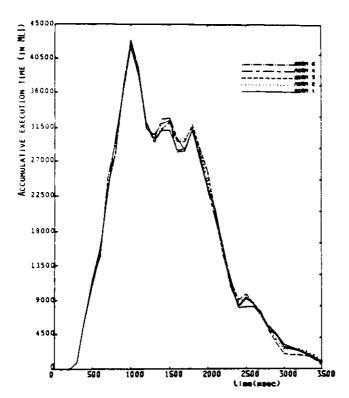

Fig. 1. Accumulative execution time of module  $M_4$ ,  $T_4(t, t + 100 \text{ ms})$ .

Processing Architecture Design (DPAD) system, are almost identical (Fig. 1).

IMC is the communication between program modules and file modules. When a module on a processor writes to or reads from a shared file on another processor, such IMC incurs IPC (interprocessor communication) and requires processing overhead. Control IMC is another type of IMC. As discussed in [8], it can be treated in the same way as the file-access IMC when we consider the control files, as opposed to the application files. The importance of IPC minimization has been recognized by many researchers [5], [14]. IPC can be reduced by assigning a pair of heavily communicating modules to the same processor. Like AET, the IMC can also be assumed to be independent of module assignments [16]. A method for estimating both IMC and AET has been reported in [8].

IPC occurs only when two communicating modules are assigned to different processors. If two modules reside on different processors and communicate through a replicated shared file, then the file is assumed to be replicated on each processor. When a module updates the file, it updates the copy on its local processor and sends the updates to the remote processor. This results in IPC, which requires processing load on both the sending and receiving processors. Even if the actual transfer of the update words is done in the background by some I/O processors, the sending processor still needs to spend time on message formatting and address initialization for the I/O processor. The receiving processor, on the other end, will spend time on extracting the message contents and notifying the destination module. Such IPC overhead is eliminated if the two modules are assigned to the same processor since both modules would share the same local file copy. Module assignments also effect IPC for other file structures such as partitioned files or single-copy files.

#### B. The Objective Function

Assuming each module is assigned to one and only one processor, then there are  $S^J$  different ways to assign J modules to S processors. This can be represented by an assignment tree. This tree has J levels, each representing a module. At each nonleaf node there are S downward branches, each representing the choice of a processor to host the particular module. Therefore, the tree has  $S^J$  leaves, each leaf corresponding to a possible assignment.

An exhaustive search approach for module assignment is to search every leaf of the assignment tree. The optimal module assignment is the one that minimizes (or maximizes, e.g., throughput) a given objective function. Exhaustive search is usually undesirable because of the prohibitive time requirement. For example, if the computation time for a leaf is 250  $\mu$ s on a computer system, then the enumeration for a tree with  $3^{20}$  leaves requires about 10 days of processing time.

Existing approaches to task allocation can be divided into three categories: graph-theoretic [15], [20], [2], [3], integer 0-1 programming approach [4], [6], [18], and the heuristic approach [13], [10]. Many of these methods try to minimize a task's total cost which is defined as the sum, over all processors, of both the processing cost (i.e., AET) and the IPC cost of that task. This might be acceptable for a distributed system shared by multiple simultaneous nonreal-time applications (tasks), each having program modules running on some or all of the multiple processors. Such applications attempt to maximize the total throughput. For a distributed system with identical processors, this formulation is equivalent to the minimization of IPC since the total AET is fixed.

For real-time systems, response time is the most important performance measure. A computer system is designated solely for a specific application, i.e., the system is not shared by any other application. The system is required to finish a certain task within a specified time limit. Minimizing IPC alone may not produce a good assignment. In fact, in a homogeneous system where all processors are identical, a minimum-IPC assignment will assign all program modules to a single processor (thus, zero IPC) which will saturate that processor and thus yield poor response time.

The processor with the heaviest loading in a distributed system is the one that causes the bottleneck. For instance, for a system with three processors, an assignment resulting in 58, 60, and 61 percent of processor utilizations might have a better response time than another assignment yielding 20, 40, and 90 percent utilizations, although the total processor utilization of the first assignment is higher than the second. This is mainly due to the fact that the second assignment has a bottleneck processor more heavily loaded than the first assignment, and queueing delay is a nonlinear function that rises rapidly with the level of bottleneck (processor load).

The processor load consists of the loads due to program module execution and IPC. Therefore, both AET and IPC play important roles in module assignment and influence task response time. AET is usually represented in machine lan-

guage instruction (MLI). The number of transferred IPC words can be converted into the MLI's spent by both the processor that sends the IPC and the processor that receives it.

For a given assignment X, the workload L(r; X) on a given processor r is

$$L(r; X) = \sum_{j=1}^{J} \chi_{jr} T_j + \sum_{\substack{i=1\\i \neq r}}^{S} [IPC(r, s; X) + IPC(s, r; X)]$$

$$= AET(r; X) + IPC(r; X)$$

(1)

where  $X = [x_{jr}]$  is the assignment matrix in which  $x_{jr} = 1$  or 0 indicates whether module  $M_j$  is assigned to processor r. The first term in the equation is the AET for all modules assigned to processor r. The second term is IPC overhead due to both the IPC originated from processor r to other processors, and incoming IPC destined to processor r from other processors. For a system whose file-update messages dominate the IPC traffic, we can ignore other types of IPC such as module-enablement messages and system-control messages. The total overhead due to outgoing IPC at processor r is

$$\sum_{\substack{s=1\\s=r}}^{S} IPC(r, s; X) = \omega \sum_{j=1}^{J} \chi_{jr} \sum_{k=1}^{K} V_{jk} \sum_{\substack{s=1\\s=r}}^{S} \delta_{ks}$$

(2)

where K is the number of files used in the distributed system;  $V_{jk}$  is the IMC message volume sent from  $M_j$  to update the replicated file  $F_k$ ;  $\delta_{ks}$  indicates whether a replicated copy of  $F_k$  resides at processor s; the term  $\sum_{s=1}^{S} \delta_{ks}$  gives the number of

remote copies of  $F_k$  that must be updated; and  $\omega$  is a weighting constant for converting the message volume into MLI's. For a system with message-broadcasting capability, a file update need only be sent out *once*; thus, the term  $\sum_{s=1}^{S} \delta_{ks}$  in (2) should be replaced by the constant *one*.

The AET.  $T_j$ , for a module  $M_j$  is represented as a single value in (1). Also, the IMC between a module and a file,  $V_{jk}$ , in (2) is represented as a single value. However, the measured  $T_j$  and  $V_{jk}$  vary from one time interval to another (e.g., see Fig. 1). Since we are concerned with system performance during the peak-load period, we shall use the average  $T_j$  and  $V_{jk}$  values during the peak-load period for the terms  $T_j$  and  $V_{jk}$  in (1) and (2) to compute our objective function.

Similar to (2), the total overhead at processor r for incoming IPC from all remote sites is

$$\sum_{\substack{s=1\\s\neq r}}^{S} IPC(s, r; X) = \omega \sum_{\substack{s=1\\s\neq r}}^{S} \sum_{j=1}^{J} \chi_{js} \sum_{k=1}^{K} V_{jk} \delta_{kr}.$$

(3)

Based on the above discussion, we propose to use the workload of the bottleneck processor (in unit of MLI) as the objective function for module assignment, i.e.,

Bottleneck

$$(X) = \max_{1 \le r \le S} \{L(r; X)\}.$$

(4)

We want to find the assignment that yields the minimum

bottleneck [7] among all possible assignments in the assignment tree, i.e.,

$$\min_{X} \{ \text{Bottleneck } (X) \}, \tag{5}$$

Substituting (1) and (4) into (5) yields

$$\min_{X} \left\{ \max_{1 \le r \le S} [AET(r; X) + [PC(r; X)] \right\}$$

(6)

where AET (r; X) and IPC (r; X) are the total module execution time and total IPC overhead incurred at processor r.

A good assignment can be obtained by reducing IPC while balancing processor loads among the set of processors. A minimum-bottleneck assignment generally has low IPC and fairly balanced processor loads because of the following.

- 1) If the given assignment resulted in a large volume of IPC, the sum of processor loads over all processors would be high, which would yield high bottleneck.

- 2) If the loads were not fairly balanced for an assignment, the bottleneck (highest load of all processors) would be high which would not yield a minimum-bottleneck assignment.

Our minimum-bottleneck approach, (6), is different from the commonly used measure of minimizing the sum of processor loads (e.g., [20]),

$$\min_{X} \left\{ \sum_{r=1}^{5} \left[ AET \left( r; X \right) + IPC \left( r; X \right) \right] \right\}. \tag{7}$$

An assignment obtained from (7) can be quite unbalanced. In a homogeneous system all modules will be assigned to a single processor as discussed before. Our minimax principle [7] is also used in [21] which considers only the single execution of a task, instead of using the processor load. Since each external stimulus causes a task execution in our formulation, the processing load is based on multiple executions of a task.

#### C. Behavior of the Proposed Objective Function

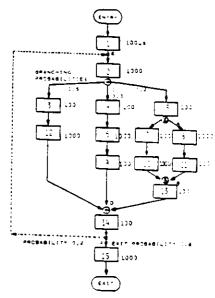

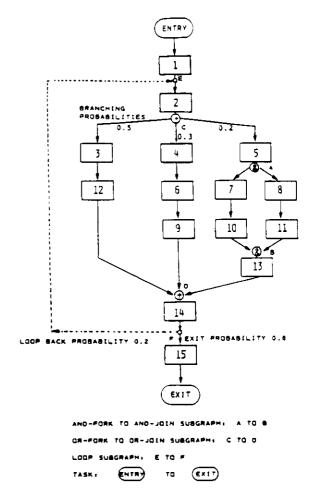

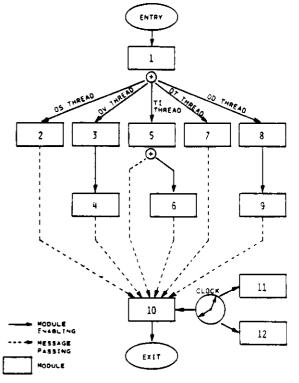

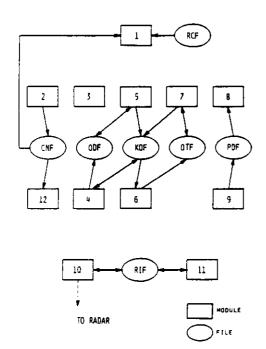

To illustrate the characteristics and performance of the proposed objective function, we apply the objective function to the Distributed Processing Architecture Design (DPAD) system. The DPAD system was developed to manage the data processing and radar resources for a space-defense application [11], [12], [18], [19]. The control-and-data-flow graph (similar to Fig. 12) consists of 23 modules which are to be assigned to three processors.

The average AET  $(T_j)$  and IMC  $(V_{jk})$  during the peak-load period (from 1.0 to 2.0 s of mission time) for all modules of the DPAD system are calculated. For example,  $T_8 = 32~055$  MLI is the average of ten measured AET values for  $M_8$  within the period at each increment of 100 ms.

A program was developed to compute the proposed objective function for every assignment (corresponding to a leaf of the assignment tree), performing an exhaustive search for the minimum-bottleneck assignment. When an assignment yields a bottleneck value lower than the smallest bottleneck obtained so far, that assignment is recorded. The last ten recorded assignments, denoted as assignment 1-10, are shown in Table I. The 23 digits under the "assignment" column represent the

- 1 -

|         | TABLE (                            |

|---------|------------------------------------|

| TOP TEN | ASSIGNMENTS FROM EXHAUSTIVE SEARCH |

|        |         |            | -         |                  |        |        |            |            |

|--------|---------|------------|-----------|------------------|--------|--------|------------|------------|

|        |         | SS(GYHENT  |           | LOAD-1           | LOAD-2 | LOAD-1 | BOTTLENECK | TOTAL LOAD |

|        | 1:37431 |            |           | 22224            | ****** |        | ********   | ********   |

| 10th   | 11111 1 | 1121 00330 | 12322 123 | 75512            | 75546  | 70420  | 75612      | 221575     |

| 9 tm   | 11111 1 | 1121 10330 | 12322 323 | 75323            | 75546  | 70700  | 75544      | 221579     |

| 9 t n  | 11112 1 | 1121 30110 | 11222 221 | 75413            | 75752  | 71541  | 75413      | 224404     |

| 12.0   | 11112 1 | 2131 10220 | 13231 132 | 75174            | 74275  | 71429  | 75174      | 223292     |

| bin    | 11112 1 | 2131 JA229 | 13231 232 | <u> 1571)</u>    | 71564  | 77929  | 75017      | 223406     |

| Sth    | 11112 1 | 2111 00220 | 13211 112 | 74414            | 78275  | 74023  | 74414      | 222712     |

| 46.5   | 11112 1 | 2111 00220 | 33211 312 | 71747            | 711275 | 74312  | 74712      | 222436     |

| 301    | 12123 2 | 1212 10110 | 21122 113 | - 4 3 n <b>9</b> | 73973  | 74275  | 74304      | 222456     |

| 201    | 12121 2 | 1212 30130 | 21322 213 | रधर्म र दे       | 7/1038 | 74275  | 74275      | 222112     |

| HTHIM. | 12213 1 | 3121 00330 | 11122 221 | 74004            | *3905  | 74275  | 74275      | 222094     |

| of the |         |            | ,         |                  |        |        |            | • •        |

| HECK   |         |            |           |                  |        |        |            |            |

MOTE: 1, LOAD-L IS EACH PROCESSOR'S LOAD PER 100 MSEC (IN HMIT OF HLT).

2. AN ASSIGNMENT WITH THE MINIMUM TOTAL LOAD

IS NOT THE ASSIGNMENT WITH THE MINIMUM BOTTLENECK.

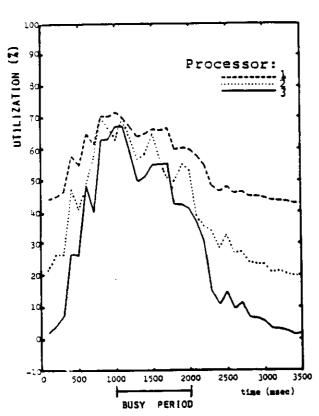

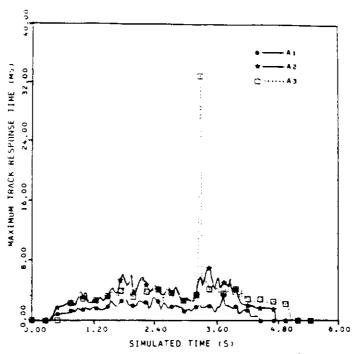

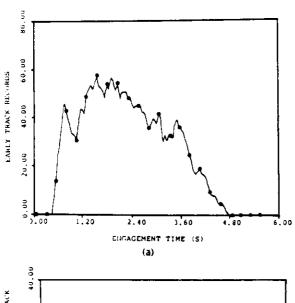

Fig. 2. Processor utilization for the best module assignment selected by exhaustive search.

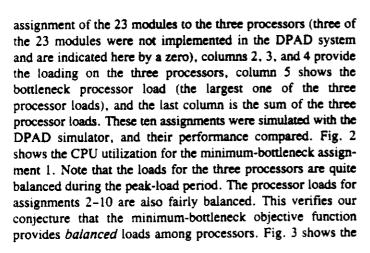

Fig. 3. Precision-Tracking Thread response times—compare the best assignment from exhaustive search, Algorithm P-I-A, and the four assignments from Ma et al. [18].

Precision-Tracking port-to-port time (response time for a task thread) for assignment 1 (curve 1). The assignments MA-1-MA-4, reported in [18] for the DPAD system, minimize the sum of AET and IPC and, thus, do not generate balanced-load assignments as discussed in Section II-B. As a result, their response times (curves 3-6) are higher than that generated by our objective function. (Curve 2 will be discussed later.)

#### III. PRECEDENCE RELATIONSHIP AND MODULE ASSIGNMENT

The precedence relationship (PR) among program modules is another important factor that needs to be considered in task allocation. In this section we shall present several experiments to illustrate the effect of PR on response time. These experiments provide us with enough insight to formulate an

analytical model to quantitatively study the PR effect on task allocation. The quantitative PR effect will be used in module grouping in our module-assignment algorithm.

#### A. PR Experiments

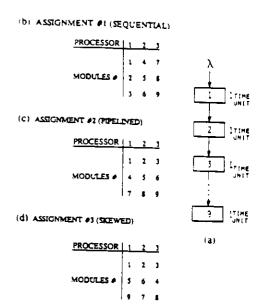

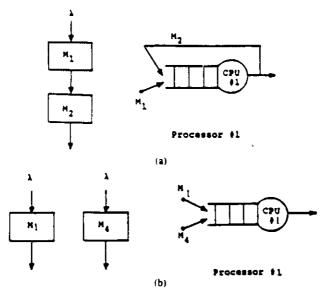

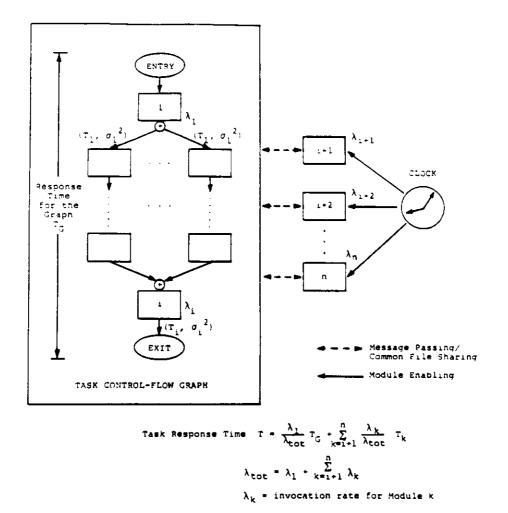

In experiment 1, we compare three assignments of a task. consisting of nine modules, to three processors. The controlflow graph [Fig. 4(a)] shows the strong PR relationship among the modules. Assume that the task arrival is a Poisson process with rate  $\lambda$ . When a module completes its execution, it enables its succeeding module according to the control-flow graph. The enabled module is placed at the end of the ready queue of its residence processor in a first-come-first-served manner. Let the execution times for all modules be identical and equal to one time unit. To clearly observe the PR effect on response time we further assume there is no IMC between the modules and thus there is no IPC overhead among the processors. Three assignments [Fig. 4(b), (c) and (d)] were simulated using the PAWS simulator [1]. The results are presented in Fig. 5. Note that assignment 2 (pipelined) yields the best task response time. The vertical bars in the figure represent 90 percent confidence intervals for each simulation point. The response time varies substantially among these assignments in spite of the fact that all the three assignments have equal and balanced loads and there is no IPC overhead. This discrepancy is solely due to the PR effect among modules.

In experiment 2, the execution time of each module is exponentially distributed (instead of being a constant), with an average of one time unit. All other parameters remain unchanged from experiment 1. Experimental results reveal that the task response times for the three assignments are comparable (Fig. 5). Due to the memoryless property of the exponential distribution, the job queue at each processor can be approximated by an M/M/1 queue. Since the service-time distributions of all modules are identical and all modules are invoked for execution at identical arrival rate, the three load-balanced processors can be represented as three identical queueing systems. Thus, the wait-time is the same for all modules and all three assignments yield the same response times.

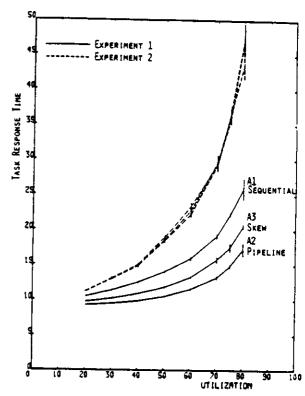

Experiment 1 reveals that precedence relationship does have an impact on task response time. Experiment 2 shows that the PR effect on response time is also influenced by module-execution-time distributions. In experiment 3, we shall study the effect of module size on response time. We assume that every module's execution time is exponentially distributed, but with a different mean value, as shown in Fig. 6. The simulation results for the three assignments reveal that assigning two consecutive modules to the same processor yields good response times if the execution time of the second module is much larger than that of the first module (Fig. 7). We shall denote this as PR Principle 1. For example, because  $y_2$  is considerably greater than  $y_1$ ,  $M_1$  and  $M_2$  should be assigned to the same processor. This principle was used in assignment 1 (Fig. 6) which yielded the best performance. Likewise, in assignment 1 module pairs  $(M_3, M_4)$  and  $(M_5, M_4)$  $M_6$ ) are allocated to processors 2 and 3, respectively.

If the second module is much smaller than the first one,

Fig. 4. Precedence-relationship experiment 1. (a) Task control-flow graph. (b) Sequential assignment. (c) Pipelined assignment. (d) Skewed assignment.

Fig. 5. Compare the response time of three module assignments. Experiment 1 uses deterministic execution time. Experiment 2 uses exponential execution time.

separating the two consecutive modules and assigning them to two different processors yields better response time. We shall denote this as PR Principle 2. Since  $y_3$  is much less than  $y_2$  in this example,  $M_2$  and  $M_3$  should be assigned to different processors. Assignment 1 satisfies the PR Principles for all pairs of consecutive modules. Therefore, it yields the best response time. Assignment 2 is the worst of the three assignments because it violates the PR Principles for all module pairs. Assignment 3 violates PR Principle 1 for some

Fig. 6. (a) Task control-flow graph and (b) module assignments for PR experiment 3.

Fig. 7. Performance of three module assignments for PR experiment 3.

module pairs (e.g., separation of  $M_1$  from  $M_2$ ) and satisfies PR Principle 2 for some other pairs (e.g., separation of  $M_2$  from  $M_3$ ), therefore its performance lies between that of assignments 1 and 2. We repeated these experiments with deterministic execution times and obtained similar results.

Let us now discuss the reasons why good response time can be obtained from following the PR Principles. When a job arrival process is deterministic, the workload is *evenly spread* over time. The average queue length at every processor and thus, the average module wait time, should be smaller than that of a bursty arrival process. If two consecutive modules are

assigned to the same processor and if the execution time of the second module is much larger than that of the first, the second one will act as a regulating valve which controls the task flow into the next processor. This makes the arrival process at the next processor more deterministic than the arrival process of the first module at the first processor. It is well known from queueing theory that for a given queueing system with a given arrival rate, the deterministic-arrival case yields less wait time than that of the bursty arrival case.

We can explain the results of experiment 3 based on the above reasoning. In assignment 1,  $M_2$  at processor 1 has a large execution time, regulating the task flow into processor 2. Therefore, even though there are bursty arrivals for  $M_1$ , the invocation arrivals for  $M_3$  at processor 2 are spread fairly evenly over time. As a result, the queue that contains invocations for  $M_3$  and  $M_4$  at processor 2 would be short and thus yield short wait times for  $M_3$  and  $M_4$ . Likewise,  $M_4$  acts as a regulating valve for the task flow into processor 3.

Assignment 2 yields poor response time. Since the size of  $M_1$  is small, each group of bursty invocation arrivals for  $M_1$ results in bursty arrivals for  $M_2$  at processor 2 (i.e., there is no regulating valve between processors 1 and 2). As a result, there is a high probability of having many arrivals for  $M_2$ waiting in the queue at processor 2. A newly arrived invocation for  $M_2$  (called  $M_2$  invocation) at processor 2 has a high probability of finding other previously arrived  $M_2$ invocations in the queue. Execution of the first  $M_2$  invocation in the queue generates an invocation for  $M_3$  which is placed at the end of the queue at processor 2. There is a long wait time for the execution of this  $M_1$  invocation due to the large number of  $M_2$  invocations in front of it. This process is repeated with the execution of other  $M_2$  invocations in the queue, thus contributing to the large response time. Furthermore, since  $M_3$ (at processor 2) is small, the consecutive  $M_3$  invocations finish their execution rapidly (although they each have a long wait time). This generates bursty invocations for  $M_4$  at processor 3. again causing long wait time for those modules assigned at processor 3.

From these experiments, we note that module-size (service time) distribution and the *module-size ratios* of consecutive module pairs influence response time. In the following, we shall use analytical methods to derive quantitative guidelines for determining whether or not a consecutive module pair  $M_i$  and  $M_j$ , with given module-size distributions and average sizes  $y_i$  and  $y_j$ , should be colocated in the same processor.

#### B. PR Analysis

Consider the control-flow graph with two separate threads in Fig. 8(a) where all modules have deterministic execution times. Assume no IMC exists among modules. Let  $y_1 = y_3$ ,  $y_2 = y_4$ . Thus, the module-size ratio  $r = r_{1,2} = y_2/y_1 = r_{3,4} = y_4/y_3$ . Furthermore, let the job arrival rates  $\lambda_1 = \lambda_2 = \lambda$ . Under the above condition, both assignments 1 and 2 [Fig. 8(b)] yield equal processor loads. However, they yield different response times. We wish to derive analytical results so that the module-size ratio r can be used as a parameter for determining whether  $M_1$  and  $M_2$  (also  $M_3$  and  $M_4$ ) should be colocated; that is, if r is greater than some threshold value,  $M_1$

Fig. 8. PR analytical study. Two threads of consecutive modules for studying wait-time ratio between assignments 1 and 2 as a function of size ratio between the consecutive modules.

and  $M_2$  should be assigned to the same processor; otherwise they should be separated.

The response time for the left control thread in Fig. 8(a) is  $w_1(A, r) + y_1 + w_2(A, r) + y_2$  while the response time for the right thread is  $w_3(A, r) + y_3 + w_4(A, r) + y_4$ , where  $w_i(A, r)$  is the queueing wait time experienced by module  $M_i$ . The queueing wait time is a function of both the assignment A and the module-size ratio r. Because of the symmetry of the two threads and the balanced loading on both processors, both threads have the same response time for assignment 1, denoted as  $A_1$ . The two threads also have the same response time for  $A_2$ . Therefore, it is sufficient to compare  $A_1$  and  $A_2$  using the response time of only one thread. The left thread is chosen for the following analysis.

The thread response times for  $A_1$  and  $A_2$  are  $w_1(A_1, r) + y_1 + w_2(A_1, r) + y_2$  and  $w_1(A_2, r) + y_1 + w_2(A_2, r) + y_2$ , respectively. Since the values of  $y_1, y_2, y_3$ , and  $y_4$  are fixed and independent of module assignment, they need not be considered. Thus, the wait-time ratio between assignments 1 and 2 is defined as

$$R = R(r) = \frac{w_1(A_1, r) + w_2(A_1, r)}{w_1(A_2, r) + w_2(A_2, r)}.$$

(8)

If R < 1, then assignment 1 yields better response time than assignment 2. The response-time improvement is due to better handling of the PR effect. Under such conditions, we should assign the pair of consecutive modules  $M_1$  and  $M_2$  to the same processor, and the other pair  $M_3$  and  $M_4$  to the alternate processor. If R > 1, then assignment 2 has better response time than assignment 1 and the consecutive modules should be assigned to different processors. Thus, R [see (8)] allows us to select the better module assignment.

Let us now discuss how to compute  $w_i(A, r)$  and thus, R. For a given control-flow graph, module assignment, and module-size distributions, the wait-time  $w_i$ 's for all modules can be estimated via the analytical model reported in [9]. The Appendix shows how to use the model to derive the numerator and denominator for (8). Therefore, we are able to determine the wait-time ratio R for various module-size ratios r. When all the modules have constant service times, we can

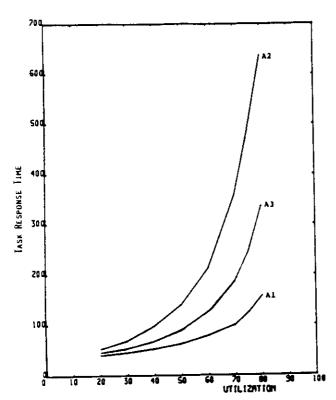

compute R as a function of processor utilization  $\rho$  for executing  $M_1$  and  $M_2$  [Fig. 9(a) and (b)]:  $\rho = \rho_1 + \rho_2$ ,  $\rho_1 = \lambda_1 y_1$  and  $\rho_2 = \lambda_1 y_2$ . Note that R increases as r decreases from 100 to 0.4 [Fig. 9(a)]. As r further decreases from 0.4. R then reverses the trend and starts to decrease [Fig. 9(b)]. Note that R = 1, occuring at r = 2.5, is the threshold value that determines whether two consecutive modules should be colocated. R varies slightly with processor utilization. In the same manner, when the module execution times are exponentially distributed, we can derive the relationship between the wait-time ratio R and the module-size ratio r, as shown in Figs. 9(c) and (d). In this case, the threshold value R = 1 occurs at r = 1.

Note from Fig. 9 that when each module execution time is exponentially distributed, R is less sensitive to r, as compared to the case of deterministic module execution time. Results from the analytical model also confirm our observation in experiments 1 and 2 that response time is more sensitive to precedence relationship when module service times are deterministic than when they are exponentially distributed.

We have extended the above analysis to encompass the case where each control thread consists of *three* consecutive modules.  $M_1$ ,  $M_2$ ,  $M_3$  are consecutive modules in one thread and  $M_4$ ,  $M_5$ ,  $M_6$  in another. Let  $y_1 = y_4$ ,  $y_2 = y_5$ ,  $y_3 = y_6$ , and  $\lambda_1 = \lambda_2$ . Assignment 1 allocates all the consecutive modules to the same processors, i.e.,

Processor 1:  $M_1$ ,  $M_2$ ,  $M_3$

Processor 2: Ma. Ms. Ms.

Assignment 2 allocates the consecutive modules to different processors, i.e.,

Processor 1:  $M_1$ ,  $M_2$ ,  $M_3$

Processor 2:  $M_4$ ,  $M_2$ ,  $M_6$ .

Note that both assignments yield balanced loads. The wait-time ratio can be expressed similar to (8). The analytical results show that if we hold  $y_1(=y_4)$  fixed, then as module-size ratio  $r_{2,3} = y_3/y_2(=y_6/y_5)$  decreases, the wait-time ratio R between assignments 1 and 2 increases to a point and then reverses the trend and starts to decrease. This is similar to the case with two-module threads (Fig. 9). Similar relationships are observed for a control-flow graph consisting of four consecutive modules in a thread. All of these suggest that one way to handle the cases with more than two consecutive modules is to treat each pair of consecutive modules in a control-flow graph independently. Using the PR relation (Fig. 9) one can decide whether to allocate the two modules to the same processor. Our experience shows that assignments generated by such an approach yield good task response time.

#### IV. MODULE ASSIGNMENT ALGORITHM

#### A. The Algorithm

Using exhaustive search to select an assignment from an entire assignment tree is prohibitively time consuming. Therefore, we shall propose a heuristic algorithm for module

Fig. 9. Wait-time ratio between two assignments as a function of programmodule-size ratio, for (a) and (b) deterministic execution times and (c) and (d) exponentially distributed execution times.

assignment (Fig. 10) that considers PR, IMC, and AET. We shall call it Algorithm P-I-A. This algorithm assumes that

- 1) there are J modules,  $M_1, M_2, \dots, M_J$ , and S processors;

- 2) the AET (an average during the peak-load period) for each module  $M_i$ ,  $T_i$ ,  $(j = 1, \dots, J)$  is given:

- 3) the IMC (an average during the peak-load period) between each module pair  $M_i$  and  $M_j$ , IMC<sub>ij</sub>,  $(i = 1, \dots, J; j = 1, \dots, J)$  is given. Each IMC<sub>ij</sub> can be derived from the  $V_{ik}$ 's [8].

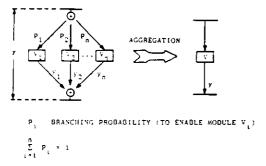

The algorithm consists of two phases. Phase I reduces J modules to G groups (G < J) which corresponds to a much smaller assignment tree for Phase II. This grouping can be done with very little computation. Each group generated at the end of Phase I is a set of modules which will be assigned as a single unit to a processor. In Phase II these groups are assigned to the processors such that the bottleneck (in the most heavily utilized processor) is minimized.

The grouping of modules in Phase I is based on several factors. To reduce IPC, heavily communicating modules may be combined into groups. To do this, communicating module pairs are listed in descending order of the IMC volume (Step 1.1). Module pairs with large IMC are considered first.

Next, the PR effects are considered. The decision of whether to group two consecutive modules should be based on the two possibly conflicting factors: IMC volume and the effect of PR (i.e., module-size ratios). For a module pair  $(M_i, M_j)$ , we propose to use IMC index  $\gamma_{IMC}(i, j) = IMC_{ij}/\overline{AET}$  and PR index  $\gamma_{PR}(i, j) = 1 - R(r_{ij})$ , as defined in the initialization in the algorithm, to evaluate these conflicting factors. The IMC index indicates the relative IMC size normalized by the average module size in terms of the execution time. The typical index value should be between 0.1 and 0.5. An IMC with an index value below 0.1 may be considered negligible. Grouping two modules with the small IMC saves little IPC. The wait-time ratio R in the PR-index

```

locustization

0. Compute average AET, \overline{AET}, and average processor load, \overline{PL}

\overline{AET} \leftarrow \hat{\Sigma} T, J

\overline{PL} \leftarrow \hat{\Sigma}T_i : S

Compute the IMC index and the PR index:

T_{\text{MC}}(i,j) = \frac{IMC_{ij}}{4ET} i = 1,...,J + 1,...,J

Y_{PR}(i,j) = 1 - R(r_{ij}) i = 1, ..., J, ..., j = 1, ..., J

Do \alpha = \alpha_1 to \alpha_2, with increment \Delta \alpha

Do \beta = \beta_1 to \beta_2, with increment \Delta \beta

Phase I \rightarrow Combine modules with large IMC into groups to reduce total system load (i.e., to reduce the sum of processor loads):

1.1. List all module pairs (M_i, M_j) in the descending order of IMC volume

Let each program module form a distinct group (a set):

G_j \leftarrow \{M_j\} j = 1,...,J

1.2 If no more pairs exist in the module-pair list

go to Phase II.

Pick the next pair of modules, M<sub>1</sub> and M<sub>2</sub>, and delete this pair from the list.

13 If \alpha \times \gamma_{IMC}(i,j) + \gamma_{PR}(i,j) \leq 0

go to Step 1.2.

1.4 Find the group G_t that contains M_t, and the group G_t that contains M_f (i.e., M_t \in G_t, M_f \in G_t).

If s = t (i.e., if M_t and M_f are already in the same group) go to Step 1.2.

15 If T_s + T_t > (\overrightarrow{PL} \times \beta)

1.6 Combine the two groups G_T and G_t into a single one: \begin{array}{ccc} G_T & \leftarrow & G_T & \cup & G_T \\ G_T & \leftarrow & \mathcal{O} \\ T_T & \leftarrow & \mathcal{O} \\ T_t & \leftarrow & 0 \end{array}

1.7 Go to Step 1.2.

Phase II — Assign module groups to processors:

2.1 Perform an exhaustive search through the new assignment tree for the assignment

2.2 Record the minimum-bottleneck assignment.

end

```

Fig. 10. The Algorithm P-I-A.

can be computed from (8). For deterministic and exponential module execution times, from Fig. 9, R ranges between 0 and 2. R=1 is the threshold value for deciding whether to group two consecutive modules. The condition R<1 corresponds to a positive PR index  $\gamma_{PR}(i,j)$ , which favors the grouping of modules  $M_i$  and  $M_j$ . Likewise, R>1 indicates a negative PR index favoring separation of  $M_i$  and  $M_j$ . Since the IMC index has a range between 0.1 and 0.5 and the PR index has a range between -1 and 1, a scaling factor  $\alpha$  is introduced to combine the two indexes (Step 1.3). The  $\alpha$  value can range from 1 to 10 and thus is a variable in Algorithm P-I-A.

Another factor to be considered is the size of a new group. If the new group, resulting from combining two subgroups, becomes too large, it would be impossible to obtain a balanced-load assignment during Phase II. Therefore, the concept of processor-load threshold ( $\overline{PL} \times \beta$ ) is introduced (Step 1.5), where  $\overline{PL}$  is the average processor load and  $\beta$  is a scale constant. If the size of a candidate new group is greater than the threshold, the two subgroups should not be combined. Note that a too small  $\beta$  would retard proper beneficial module grouping while a too large  $\beta$  makes it impossible to balance processor loads during Phase II. Our experiences on DPAD

Fig. 11. Task control-flow graph for example 1.

and other systems reveal that a good range for  $\beta$  is between 0.6 and 1.2 times of the average processor load.

For each pair of  $\alpha$  and  $\beta$  values the algorithm generates a minimum-bottleneck assignment. We should select the assignment which corresponds to the *smallest* minimum-bottleneck among all sets of  $(\alpha, \beta)$ . If several assignments yield the same smallest minimum-bottleneck value, then we select the one with the smallest *total* processor load.

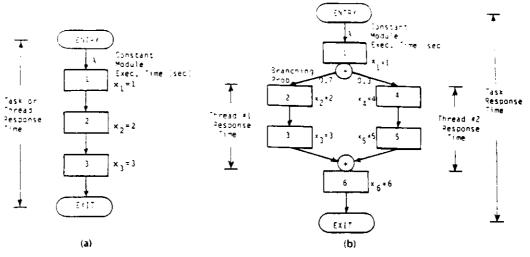

#### B. Examples

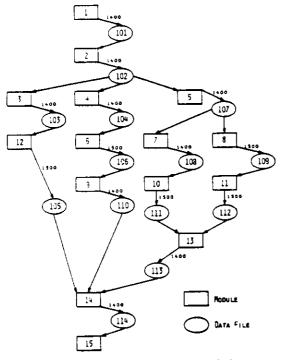

In this section, we shall use an example (denoted "example I") to show that significant response-time improvement can be achieved when PR is considered in module assignment. Consider the control-flow graph in Fig. 11 where each program module has a deterministic execution time of either 100 or 1000 µs. Thus, the size ratios of most consecutive module pairs are either 0.1 or 10 (except for four pairs whose size ratios are 1.0). The job interarrival time is assumed to be exponentially distributed, with a rate of one hundred arrivals per unit interval. Each arrival makes an invocation to the entire control-flow graph. Some modules are executed more frequently than the others. Using the model presented in [8], the AET can be estimated for a specified time interval for each module. The estimated AET for each unit interval is shown in column 2 of Table II. Let us assume that the IMC sizes for all communicating module pairs are about equal, either 1400 or 1500  $\mu$ s (see Table II and Fig. 12) which implies that IMC plays a lesser role than PR does. Given the PR, IMC, and AET, the module assignment generated by Algorithm P-I-A is shown in Table III along with the processor loads. In order to compare the PR effect, we generate a second assignment (also shown in Table III) which excludes the PR effect by replacing the Step 1.3 of Algorithm P-I-A with

1.3 If

$$\gamma_{\text{IMC}}(i, j) \leq 0.1$$

TABLE II AET  $T_i$  and File-Update IMC  $V_{ik}$  for example (

| Write+<br>Module j | AET°T <sub>]</sub> | file k<br>Updated | (MC * V<br>(k + in ls) | Read-<br>Modules |

|--------------------|--------------------|-------------------|------------------------|------------------|

| 1                  | 10,000             | 101               | 1400                   | 2                |

| 2                  | 125,000            | 102               | 1400                   | 3,4,5            |

| 3                  | 6,250              | 103               | 1400                   | 12               |

| 4                  | 1,750              | 104               | 1400                   | 6                |

| 5                  | 2,300              | 137               | 1400                   | 7.8              |

| 5                  | 37,500             | 106               | 1500                   | 9                |

| •                  | 3,500              | : 18              | 1400                   | 10               |

| э                  | 25,000             | 109               | 1500                   | 1.1              |

| 7                  | 3,750              | 110               | 1400                   | 14               |

| 10                 | 25,000             | 111               | 1500                   | 1.1              |

| 11                 | 2,500              | 112               | 1500                   | 11               |

| 1.2                | 62,500             | 105               | 1500                   | 14               |

| 13                 | 2,500              | 113               | 1400                   | 14               |

| 1.4                | 12,500             | 114               | 1400                   | 15               |

| 1.5                | 100,000            |                   |                        |                  |

\* AET and Total IMC during a 100-arrival period

Fig. 12. Data-flow graph for example 1.

When  $\gamma_{IMC}(i, j) \leq 0.1$ , the IMC effect is negligible. We called this Algorithm I-A.

Note that in the assignment generated by Algorithm P-I-A, most module pairs are assigned (either colocated or separated) according to our PR Principles rather than the IMC sizes. For example, the module-size ratio  $r_{4,6} = y_6/y_4 = 10$ , thus  $M_4$  and  $M_6$  are colocated on processor 3. On the other hand,  $r_{6,9} = 0.1$ , thus  $M_6$  is separated from  $M_9$  although IMC<sub>6,9</sub> is larger than IMC<sub>4,6</sub>.

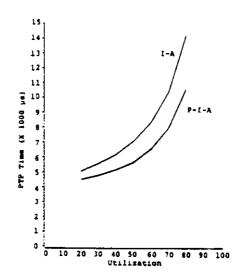

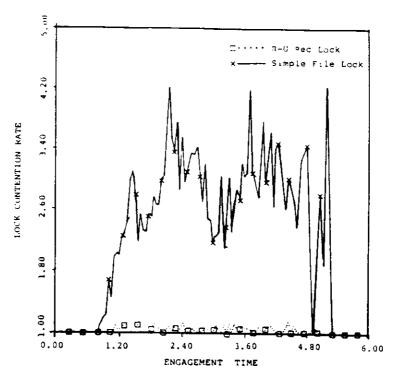

These two assignments are simulated via the PAWS simulator. The average response time for each job arrival is measured from when the job arrives at the system until it finishes the execution of  $M_{15}$ . Fig. 13 portrays the response time for the two assignments. Note that the assignment generated by Algorithm P-I-A yields better response time

than that generated by Algorithm I-A, with 10.8 percent improvement at processor utilization  $\rho=0.2$  and 25.7 percent improvement at  $\rho=0.8$  percent. Both assignments yield fairly balanced processor loads with similar bottleneck values. The difference in response time is due to the consideration of PR in module assignment.

We have applied both Algorithms P-I-A and I-A to the DPAD module assignment problem. The assignment generated from Algorithm P-I-A is the same as that generated from Algorithm I-A. This is due to the fact that there are very few consecutive modules in the DPAD system. Note that if a module is enabled by another through an or branch with a low probability (say less than 0.5), the PR effect of such a module pair is greatly reduced. Therefore, they can logically be viewed as nonconsecutive modules because the second module is not always invoked for execution after the first module finishes its execution. Many module pairs in the DPAD belong to this type. The result also reveals that the performance of the best assignment obtained from Algorithm P-I-A is comparable with that of the exhaustive search (see Fig. 3). This demonstrates that the heuristic Algorithm P-I-A can generate an assignment which yields response time comparable to that of using the time-prohibitive exhaustive search method.

#### V. SUMMARY

The three important parameters that influence task allocation are accumulative execution time (AET) of each module, intermodule communication (IMC), and precedence relationship (PR) among program modules. AET contributes to processor load and is independent of task allocation. IMC is the communication between program modules through shared files. When a module on a processor writes to or reads from a shared file on another processor, IMC becomes IPC (interprocessor communication) which requires extra processing and communication overhead. A task-allocation algorithm should minimize the IPC by assigning heavily communicating modules to the same processor.

An objective function for minimizing the bottleneck processor load (consisting of IMC and AET) has been proposed for task allocation. It is shown to generate load-balanced assignments with small IPC.

The third parameter for task allocation is the precedence relationship (PR). Due to PR, a program module cannot be enabled before its predecessor(s) finish executing. Both simulation and analytical study revealed that the module-size ratio of two consecutive modules affects task response time. Two principles were observed: 1) assigning two consecutive modules to a same processor yields good response times if the execution time of the second module is much larger than that of the first module; 2) if the second module is much smaller than the first one, the two consecutive modules should be separated and assigned to two different processors.

An analytical model was proposed to study the PR effect on response time which quantitatively determines whether two consecutive modules should be colocated in a processor. Our study reveals that this depends on the size ratio of the two consecutive modules, module-execution-time distribution, and processor load.

|        | TABLE III       |          |   |

|--------|-----------------|----------|---|

| MODULE | ASSIGNMENTS FOR | FYAMPI F | 1 |

|                        | ASSIGNODIT I-A<br>(W/O CONSIDERING PR) |              |                             | ASSIGNOUNT P-I-A<br>(CONSIDERING PR) |                           |                      |

|------------------------|----------------------------------------|--------------|-----------------------------|--------------------------------------|---------------------------|----------------------|

| MODULES                | 1<br>2<br>4                            | 6<br>9<br>15 | CPU3 3 5 7 6 10 11 12 13 14 | 1<br>2<br>9                          | 7<br>10<br>13<br>14<br>15 | CPU3 3 4 5 6 8 11 12 |

| PROCESSOR<br>LOADS     | 141550                                 | 144050       | 146850                      | 143050                               | 148300                    | 147300               |

| PERCENTAGE<br>OF LOADS | 32.73X                                 | 33.319       | 33.96%                      | 32.61X                               | 33.81%                    | 33.54%               |

Fig. 13. Task-response-time comparison between assignments with and without PR consideration for example 1.

A heuristic algorithm that considers PR, IMC, and AET was developed for task allocation. In determining whether two consecutive modules should be colocated on the same processor, the effect of PR on response time may be in conflict with the effect of IMC. Therefore, the allocation algorithm jointly considers the effect of IMC and PR. Using the minimum bottleneck as an objective function, the algorithm was applied to two example systems. The results revealed that module assignments considering PR may yield better response time than assignments without PR consideration.

Further investigation is needed to generalize the algorithm to handle the assignment of replicated program modules. This could have a significant effect on task response time [22].

#### GLOSSARY

$F_k$ —the kth file in the system IMC—intermodule communication IPC—interprocessor communication J—number of program modules

K-number of files

L-processor loading

MLI-machine language instruction

$M_i$ —the jth program module

$N_j(t_h, t_{h+1})$ —number of times module  $M_j$  executes during  $(t_h, t_{h+1})$

R-wait-time ratio of two assignments

S—number of processors (sites)

$T_j(t_h, t_{h+1})$ —accumulative execution time (AET) for module  $M_j$  during  $(t_h, t_{h+1})$

$V_{jk}$ —IMC message volume sent from  $M_j$  to update the file  $F_k$   $X = \{x_{jr}\}$ —module assignment matrix in which  $x_{jr}$  (= 1 or 0) indicates whether module  $M_j$  is assigned to processor r

$r_{i,j}$ —size ratio between modules  $M_i$  and  $M_i$

$w_j(A, r)$ —the queueing wait-time of module  $M_j$  for assignment A and module-size ratio, r

$y_i$ —average execution time of module  $M_i$  per execution

$\delta_{ks}$ —indicating function to specify whether a copy of  $F_k$  resides at processor s

Fig. 14. Queuing model for computing module waiting time for (a) Assignment 1 and (b) Assignment 2.

λ-task arrival rate

ρ-processor utilization

$\omega$ —a normalizing constant for converting IMC to MLI's.

#### APPENDIX

#### I. DERIVATION OF THE NUMERATOR FOR (8) (ASSIGNMENT 1)

According to [9], the average wait-time  $w_1(A_1, r)$  and  $w_2(A_1, r)$  at Processor 1 for Assignment 1 can be obtained as follows. The mean wait-time for a given invocation of  $M_1$  under FCFS scheduling policy is the average time to complete the executions of both the module invocation currently being served by the processor and all module invocations waiting in the job queue when the given  $M_1$  invocation arrives. [See Fig. 14(a)]. Thus, we have

$$w_1(A_1, r) = w_{r1} + \overline{n_1} \overline{y_1} + \overline{n_2} \overline{y_2}$$

(A-1)

where

$w_{r1}$  = mean residual module-execution time at processor 1 for assignment 1.

$$= \frac{1}{2} (\lambda \overline{y_1^2} + \lambda \overline{y_2^2})$$

$$= \frac{1}{2} \lambda [(1 + c_1^2) y_1^2 + (1 + c_2^2) y_2^2]$$

$c_i$  = coefficient of variation for the execution time of  $M_i$   $\overline{n_i}$  = average number of  $M_i$  invocations waiting in the job queue.

To find the waiting time for  $M_2$ , we need to keep track of the queueing behavior starting from the arrival of the invocation for  $M_1$ . Let us consider a particular tagged invocation for  $M_1$ . After the completion of this tagged  $M_1$  execution, its succeeding tagged invocation for  $M_2$  is placed at the end of the job queue. The waiting time for this tagged  $M_2$  invocation consists of three components. The first component is the total

execution time of the new invocations for  $M_1$  that arrive during the waiting and execution time of the tagged  $M_1$  invocation. The second component is due to the executions of all the  $M_2$  invocations which are enabled by the  $M_1$  invocations that wait in the job queue when the tagged  $M_1$  invocation arrives at processor 1. The last component is due to the execution of a  $M_2$  invocation (with a probability of  $\rho_1 = \lambda \overline{x_1}$ ). This  $M_2$  invocation is enabled if module  $M_1$  is in execution at the arrival of the tagged  $M_1$  invocation. By adding these components, we have

$$w_2(A_1, r) = [w_1(A_1, r) + \overline{y_1}]\lambda \overline{y_1} + \overline{n_1}\overline{y_2} + \rho_1\overline{y_2}.$$

(A-2)

Since  $\overline{n_i} = \lambda w_i$  (Little's result [23]) and  $\rho_i = \lambda y_i$ , (A-1) and (A-2) become

$$w_1(A_1, r) = w_{r1} + \rho_1 + w_1(A_1, r) + \rho_2 + w_2(A_1, r)$$

(A-3)

and

$$w_2(A_1, r) = (w_1(A_1, r) + \overline{y_1})\rho_1 + \rho_2 + w_1(A_1, r) + \rho_1 \overline{y_2}.$$

(A-4)

From (A-3) and (A-4),  $w_1(A_1, r)$  and  $w_2(A_1, r)$  can be solved as

$$w_1(A_1, r) = \frac{w_{r1} + \rho_1 \rho_2 (\overline{y_1} + \overline{y_2})}{1 - \rho_1 - \rho_2 (\rho_1 + \rho_2)}$$

(A-5)

anc

$$w_2(A_1, r) = \frac{w_{r1} + \rho_1 \rho_2(\overline{y_1} + \overline{y_2})}{1 - \rho_1 - \rho_2(\rho_1 + \rho_2)} (\rho_1 + \rho_2) + \rho_1(\overline{y_1} + \overline{y_2}). \quad (A-6)$$

Therefore, the numerator of (8) is the sum of (A-5) and (A-6).

#### II. DERIVATION OF THE DENOMINATOR FOR (8) (ASSIGNMENT 2)

With Assignment 2, Processor 1 can be treated as an M/G/1 queueing system with two types of "customers,"  $M_1$  and  $M_4$ . [See Fig. 14(b)]. The mean wait-time for these customers is given by

$$w_1(A_2, r) = w_4(A_2, r) = \frac{w_{r2}}{1 - \rho} = \frac{w_{r2}}{1 - \rho_1 - \rho_4} = \frac{w_{r2}}{1 - \lambda \overline{y_1} - \lambda \overline{y_4}}$$

(A-7)

where

$\rho_i = \text{processor utilization due to module } i$

$w_{r2}$  = mean residual module execution time at processor 1 for assignment 2

$$= \frac{1}{2} (\lambda \overline{y_1^2} + \lambda \overline{y_4^2})$$

$$= \frac{1}{2} \lambda [(1 + c_1^2) \overline{y_1^2} + (1 + c_4^2) \overline{y_4^2}].$$

Due to the symmetry in module threads (See Fig. 8),  $w_2(A_2, r) = w_4(A_2, r)$ . Thus, the denominator of (8) is equal to  $2w_1(A_2, r) = 2w_{r2}/(1 - \lambda \overline{y_1} - \lambda \overline{y_4})$ .

#### ACKNOWLEDGMENT

The formulation of the wait-time ratio as a function of module assignment and module-size ratio, was first proposed and studied by K. K. Leung at UCLA. The Appendix is

adapted from his dissertation [17]. The authors would also like [23] J. D. C. Little, "A proof of the queueing formula  $L = \lambda W$ ," Oper to thank the referees for their comments which improved the organization of this paper.

Res., vol. 9, pp. 383-387, 1961.

#### REFERENCES

- [1] R. Berry, K. M. Chandy, J. Misra, and D. Neuse, PAWS 2.0-Performance Analyst's Workbench System: User's Manual, Inform. Res. Ass., Austin, TX, Dec. 1982.

- [2] S. H. Bokhari, "Dual processor scheduling with dynamic reassignment." IEEE Trans. Software Eng., vol. SE-5, pp. 341-349, July

- [3] T. C. K. Chou and J. A. Abraham, "Load balancing in distributed systems." IEEE Trans. Software Eng., vol. SE-8, pp. 401-412, July 1982.

- [4] W. W. Chu, "Optimal file allocation in a multiple computer system," IEEE Trans. Comput., vol. C-18, pp. 885-889, Oct. 1969.

- [5] W. W. Chu, D. Lee, and B. Iffla, "A distributed processing system for navai data communication networks," in Proc. AFIPS Nat. Comput. Conf., vol. 47, 1978, pp. 783-793.

- [6] W. W. Chu, L. J. Holloway, M. T. Lan, and K. Efe, "Task allocation in distributed data processing," Computer, vol. 13, pp. 57-69, Nov. 1980.

- [7] W. W. Chu, J. Hellerstein, M. T. Lan, J. M. An, and K. K. Leung, "Database management algorithms for advanced BMD applications. Dep. Comput. Sci., Rep. UCLA-ENG-84-07 (CSD-840031), Univ. California, Los Angeles, Apr. 1984.

- [8] W. W. Chu, M-T. Lan, and J. Hellerstein, "Estimation of intermodule communication (IMC) and its applications in distributed processing systems." IEEE Trans. Comput., vol. C-33, pp. 691-699, Aug.

- [9] W. W. Chu and K. K. Leung, "Task-response-time model and its applications for real-time distributed processing systems," in Proc. 5th Real-Time Syst. Symp., Austin, TX, Dec. 1984, pp. 255-236.

- [10] K. Efe. "Heuristic models of task assignment scheduling in distributed systems," Computer, vol. 15, pp. 50-56, June 1982.

- [11] M. L. Green, E. Y. S. Lee, S. Majumdar, and D. C. Shannon, "A distributed real-time operating system," in Proc. Symp. Distributed Data Acquisition, Comput. Contr., Dec. 1980, pp. 175-184.

- -, Phase III of Distributed Processing Architecture Design (DPAD) System-The DDP Underlay Simulator Experiment: Tactical Applications and d-RTOS Models, TRW Defense Space Syst. Group, Special Rep. 35010-79-A005, May 15, 1980.

- [13] V. B. Gylys and J. A. Edwards, "Optimal partitioning of workload for distributed systems," in Proc. COMPCON Fall 76, Sep. 1976, pp. 353-357.

- [14] K. B. Irani and K-W. Chen, "Minimization of interprocessor communication for parallel computation," IEEE Trans. Comput., vol. C-31, pp. 1067-1075, Nov. 1982.

- [15] C. J. Jenny, "Process partitioning in distributed systems," in Proc. NTC 1977, pp. 31:1-1-31:1-10.

- [16] L. M-T. Lan, "Characterization of intermodule communications and heuristic task allocation for distributed real-time systems," Ph.D. dissertation, Rep. CSD-850012, Univ. California, Los Angeles, Mar. 1985.

- [17] K. K. Leung, "Task response time and module assignment for real time distributed processing systems," Ph.D. dissertation, UCLA, Dec.

- [18] P. Y. R. Ma, E. Y. S. Lee, and M. Tsuchiya, "A task allocation model for distributed computing systems," IEEE Trans. Comput., vol. C-31, pp. 41-47. Jan. 1982.

- [19] D. Palmer, "On the design of distributed data processing systems," in Proc. COMPSAC 78, Chicago, IL, invited paper.

- [20] G. S. Rao, H. S. Stone, and T. C. Hu, "Assignment of tasks in a distributed processing system with limited memory," IEEE Trans. Comput., vol. C-28, pp. 291-299, Apr. 1979.

- [21] C. C. Shen and W. H. Tsai, "A graph matching approach to optimal task assignment in distributed computing systems using a minimax criterion." IEEE Trans. Comput., vol. C-34, pp. 197-203, Mar. 1985.

- [22] W. W. Chu and K. K. Leung, "Module replication and assignment for real-time distributed processing systems," Proc. IEEE, May 1987.

|  | ٠ |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

### CHAPTER II

# 2.2 MODULE ASSIGNMENT FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS