SYNTHESIS OF CUSTOM INTEGRATED CIRCUITS FROM A HIGH-LEVEL BEHAVIORAL DESCRIPTION

Steven Hennick Kelem

July 1987 CSD-870028

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# UNIVERSITY OF CALIFORNIA

# Los Angeles

Synthesis of Custom Integrated Circuits

From a High-Level Behavioral Description

A dissertation submitted in partial satisfaction of the requirement for the degree of Doctor of Philosophy in Computer Science

by

Steven Hennick Kelem

| • |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

© Copyright by

Steven Hennick Kelem

|   |  | • |

|---|--|---|

|   |  |   |

|   |  |   |

|   |  |   |

|   |  |   |

| · |  |   |

|   |  |   |

|   |  |   |

The dissertation of Steven Hennick Kelem is approved.

Bill Mitchell

Arme Adhachd

Bruce Rothschild

Bruce Rothschild

Vance Tyree

Vance Tyree

Wance Tyree

Wiln D. Ercege

Milos Ercegovac, Committee Co-Chair

University of California, Los Angeles

1987

|   | - |

|---|---|

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

| • |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

# TABLE OF CONTENTS

| 1 | Int | roduct                | ion                             |

|---|-----|-----------------------|---------------------------------|

| 2 |     | CS Language           |                                 |

|   | 2.1 | Relat                 | ion of the Language to Hardware |

|   | 2.2 | Level                 | of Description                  |

|   | 2.3 | Algor                 | ithmic Language Footunes        |

|   | 2.0 | 2.3.1                 | ithmic Language Features        |

|   |     | $\frac{2.3.1}{2.3.2}$ | Data and Data Types             |

|   |     | 2.3.2                 | Arrays                          |

|   |     |                       | 2.3.2.1 Array Declarations      |

|   |     |                       | 2.3.2.2 Array Denotations       |

|   |     |                       | 2.3.2.3 Array Operators         |

|   |     |                       | 2.3.2.4 LEB Operator:           |

|   |     |                       | 2.3.2.5 RIB Operator:           |

|   |     |                       | 2.3.2.6 LWB Operator:           |

|   |     |                       | 2.3.2.7 <b>UPB</b> Operator:    |

|   |     |                       | 2.3.2.8 @ Operator:             |

|   |     |                       | 2.3.2.9 Array Element Access:   |

|   |     |                       | 2.3.2.10 <b>REV</b> Operator:   |

|   |     |                       | 2.3.2.11 APPEND Operator:       |

|   |     |                       | 2.3.2.12 PREPEND Operator:      |

|   |     |                       |                                 |

|   |     | 2.3.3                 | 6                               |

|   |     | 2.3.4                 | <b>D</b> 44                     |

|   |     | 2.3.5                 | I fanis and a                   |

|   |     | 2.3.6                 | (A) = = = 4 : (P) (P)           |

|   |     | 2.3.7                 | Flow of Control                 |

|   |     | 2.0.1                 | Flow of Control                 |

|   |     |                       |                                 |

|   |     |                       |                                 |

|   |     | 990                   | 2.3.7.3 Sequential Iteration    |

|   |     | 2.3.8                 | Flow of Data                    |

|   |     | 2.3.9                 | Communication                   |

|   | 0.4 | 2.3.10                | Semantics                       |

|   | 2.4 | Target                | Language Features               |

|   |     | 2.4.1                 | Operators                       |

|   |     | 2.4.2                 | Flow of Control                 |

|   |     | 2.4.3                 | Flow of Data 44                 |

|   |     | 2.4.4                 | Data Objects and Structuring    |

|   |     | 2.4.5          | Communication                                    |

|---|-----|----------------|--------------------------------------------------|

|   |     | 2.4.6          | Storage                                          |

|   |     | 2.4.7          | Technology-Dependent features                    |

| 3 | Syn | thesis         |                                                  |

| • | 3.1 |                | round                                            |

|   | 3.2 |                | E Language Analysis                              |

|   | 0.2 | 3.2.1          | Lexical Analysis                                 |

|   |     | 3.2.2          | Parsing                                          |

|   |     | 3.2.2          |                                                  |

|   | 3.3 |                | Determining Program Structure                    |

|   | ა.ა | 3.3.1          |                                                  |

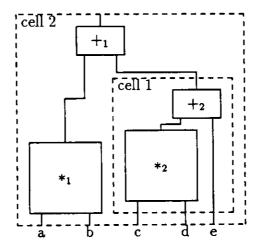

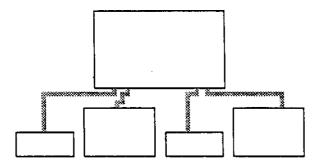

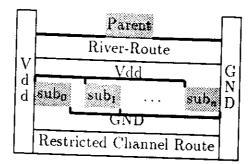

|   |     | 3.3.2          | Hierarchical Layout                              |

|   |     | 3.3.3          | Standard Cells                                   |

|   |     | 3.3.4          | Hierarchical Standard Cells                      |

|   |     | 3.3.5          | Power and Ground Distribution                    |

|   |     | 3.3.6          | Hierarchical Placement                           |

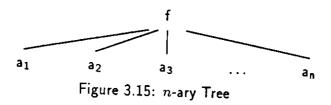

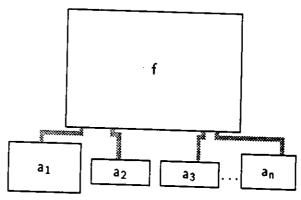

|   |     | 3.3.7          | n-ary Trees                                      |

|   |     |                | Conditional Expressions                          |

|   |     | 3.3.8<br>3.3.9 | Converting Arrays to Sequences                   |

|   |     |                | Converting Sequences to Arrays                   |

|   |     | 3.3.10         | Sequential Iterations                            |

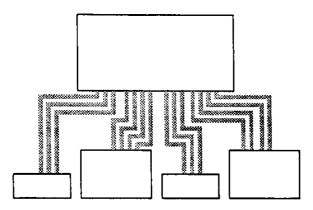

|   |     | 3.3.11         | Routing                                          |

|   |     |                | 3.3.11.1 River Routing                           |

|   |     |                | 3.3.11.2 Permutation Routing                     |

|   |     |                | 3.3.11.3 One-to-Many Channel Routing             |

|   |     |                | 3.3.11.4 Routing for $n$ -ary Trees              |

|   | 0.4 | D ()           | 3.3.11.5 Routing for Conditional Expressions 107 |

|   | 3.4 |                | ating Non-Behavioral Attributes                  |

|   |     | 3.4.1          | Area                                             |

|   |     | 3.4.2          | Power                                            |

|   |     | 3.4.3          | Delay                                            |

|   | 3.5 |                | ty of the Approach                               |

|   | 3.6 | Summ           | ary                                              |

| 4 | Tim | e Con          | plexity of the Synthesis Method 116              |

|   | 4.1 |                |                                                  |

|   | 4.2 |                |                                                  |

|   | 4.3 |                | ure Tree Construction                            |

|   | 4.4 |                | ure Tree Traversal                               |

|   | 4.5 |                | t                                                |

|   | 4.6 |                | g                                                |

|   | 1.0 | 4.6.1          | Terminology and Assumptions:                     |

|   |     | 4.6.2          | Determining Channel Height-Previous Work         |

|   |     |                | Problems                                         |

|   |     | T-11-11        |                                                  |

|                  |       | 4.6.4 Creation of the Wires                                 |   |

|------------------|-------|-------------------------------------------------------------|---|

|                  |       | 4.6.5 Signal Routing                                        |   |

|                  | 4.7   | Summary                                                     |   |

| 5                | Exa   | mples 128                                                   | ļ |

|                  | 5.1   | Switching Expressions                                       | 3 |

|                  | 5.2   | Conditional Expressions                                     | ) |

|                  | 5.3   | Equals                                                      |   |

|                  | 5.4   | Another Equals                                              |   |

|                  | 5.5   | Two's Complement Ripple-Carry Adder                         |   |

|                  | 5.6   | Redundant-Digit Adder                                       |   |

| 6                | Con   | ıclusions                                                   | Ł |

|                  | 6.1   | Contributions                                               |   |

|                  | 6.2   | Limitations                                                 |   |

|                  | 6.3   | Future Research                                             |   |

|                  | 6.4   | Conclusions                                                 |   |

| $\mathbf{R}_{0}$ | efere | nces                                                        | L |

| A                | Sen   | nantics for the Row Data Type Constructor and Primitive Op- |   |

|                  | erat  | ors                                                         | 3 |

|                  |       | Introduction                                                |   |

|                  | A.2   | Background                                                  | 7 |

|                  | A.3   | Representations                                             |   |

|                  | A.4   | Extensions                                                  | ) |

|                  | A.5   | Semantics                                                   |   |

| R                | Syn   | tay of ATICS                                                | 0 |

.

# LIST OF FIGURES

| 2.1                                          | Syntax of an Array Declaration                                    | )                          |

|----------------------------------------------|-------------------------------------------------------------------|----------------------------|

| 2.2                                          | Parallel Application of OR to Two Bit Arrays                      | )                          |

| 2.3                                          | Serial Application of <b>OR</b> to Two Bit Arrays                 | )                          |

| 2.4                                          | Syntax of a Function Definition                                   | 2                          |

| 2.5                                          | Syntax of a Operator Definition                                   | 3                          |

| 2.6                                          | Syntax of an ELIF Clause in an IF-Expression                      |                            |

| 2.7                                          | General Form of a CASE Expression                                 | ;                          |

| 2.8                                          | General Form of a Parallel Expression                             | 3                          |

| 2.9                                          | Expansion of Parallel Iteration                                   | 7                          |

| 2.10                                         |                                                                   | 7                          |

| 2.11                                         | Expanded Parallel Iteration for a Permutation                     | 7                          |

|                                              | Expanded Parallel Iteration for a Permutation                     | 3                          |

|                                              | General Form of a Sequential Iteration                            | 3                          |

| 2.14                                         | Specification of a State Machine                                  | )                          |

|                                              | General Specification of a Moore Machine                          | )                          |

| 2.16                                         | General Specification of a Mealy Machine                          | )                          |

|                                              | Specification of a Moore Machine Ripple-Carry Adder 40            | )                          |

|                                              | Specification of a Mealy Machine Ripple-Carry Adder 41            | 1                          |

| 2.19                                         | Chisel SCMOS Technology File                                      | 7                          |

|                                              | Additional Chisel Parameters for Routable Layers Specification 48 |                            |

|                                              | Additional Chisel Parameters for Metal Migration Specification 48 |                            |

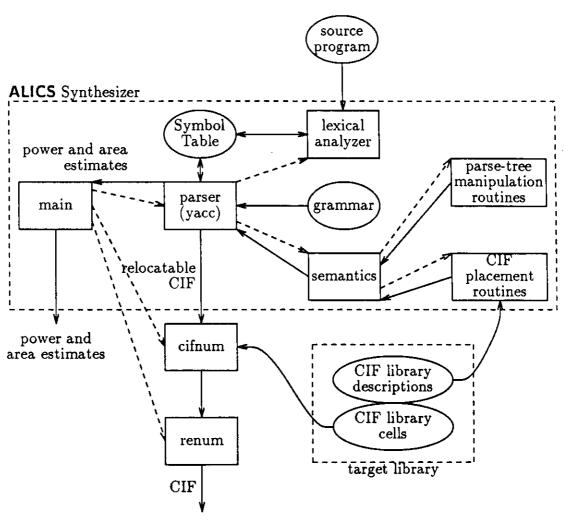

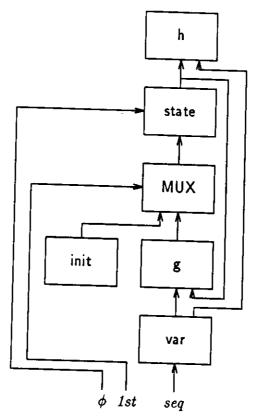

| 3.1                                          | Flow of Data and Control in the ALICS Synthesizer                 | ስ                          |

| 3.2                                          | ALICS Program Fragment                                            |                            |

| $\frac{3.2}{3.3}$                            | Tokens Representing the Program Fragment in Figure 3.2 55         |                            |

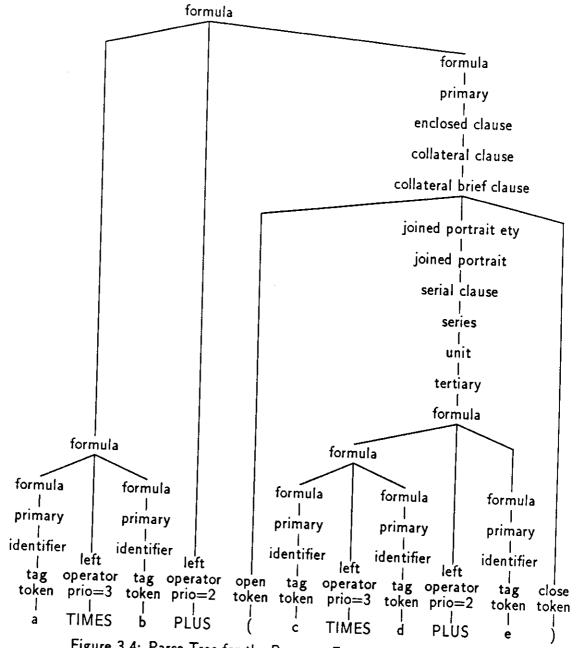

| 3.4                                          | Parse Tree for the Program Fragment in Figure 3.2                 |                            |

| 3.4                                          | Grammar Rule for an enclosed clause                               |                            |

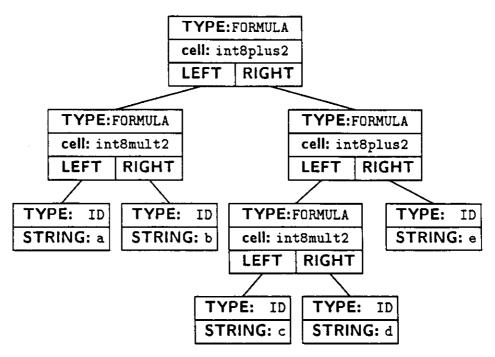

|                                              | Structure Tree Node for a Formula                                 |                            |

| 3.6                                          | Structure Tree for the ALICS Program Fragment in Figure 3.2 5     |                            |

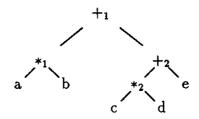

| 3.7                                          |                                                                   | o                          |

| 3.8                                          |                                                                   | c                          |

| ~ ~                                          | Structure Representing a Simple Computation                       |                            |

| 3.9                                          | Structure Representing a Simple Computation                       | 6                          |

| 3.10                                         | Structure Representing a Simple Computation                       | 6<br>9                     |

| 3.10<br>3.11                                 | Structure Representing a Simple Computation                       | 6<br>9                     |

| 3.10<br>3.11                                 | Structure Representing a Simple Computation                       | 6<br>9<br>1                |

| 3.10<br>3.11<br>3.12                         | Structure Representing a Simple Computation                       | 6<br>9<br>1                |

| 3.10<br>3.11<br>3.12<br>3.13                 | Structure Representing a Simple Computation                       | 6<br>9<br>1<br>3           |

| 3.10<br>3.11<br>3.12<br>3.13<br>3.14         | Structure Representing a Simple Computation                       | 6<br>9<br>1<br>3<br>4<br>5 |

| 3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15 | Structure Representing a Simple Computation                       | 6<br>9<br>1<br>3           |

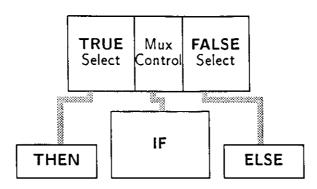

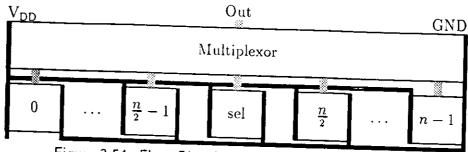

| 3.17 | Block Diagram for an IF-expression                                   | 69  |

|------|----------------------------------------------------------------------|-----|

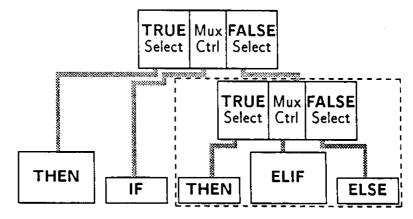

| 3.18 | Schematic for a CMOS IF-expression                                   | 69  |

|      | Structure for an IF Expression Containing an ELIF Clause             | 70  |

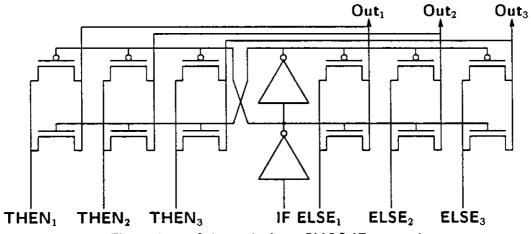

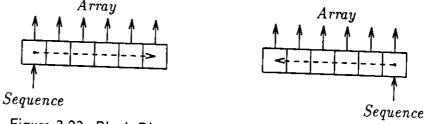

| 3.20 | Block Diagrams for Array to Sequence Operators                       | 71  |

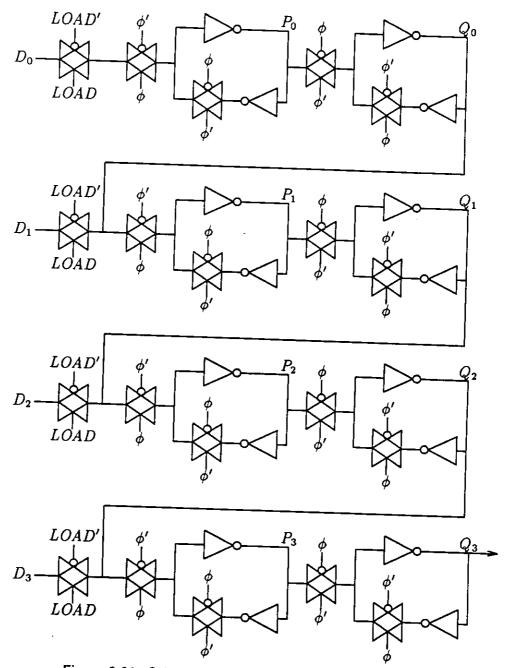

| 3.21 | Schematic for Four Bits of a Shift Register                          | 72  |

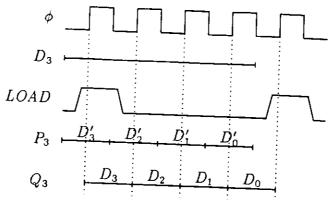

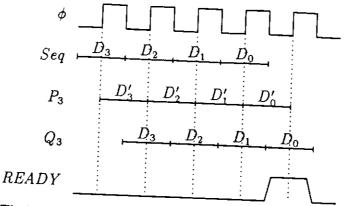

| 3.22 | Timing Diagram for a 4-Bit Shift Register in Figure 3.21             | 73  |

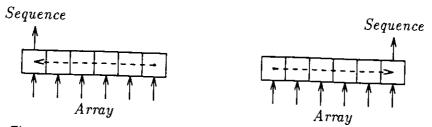

|      | Block Diagrams for Sequence to Array Operators                       | 73  |

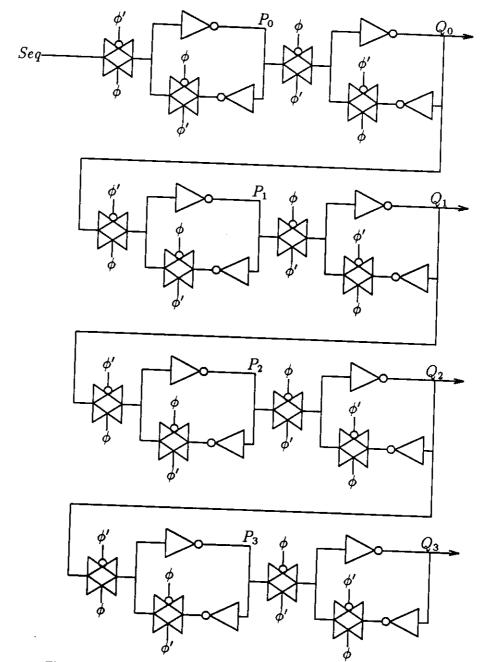

|      | Schematic for Four Bits of a Shift Register                          | 74  |

|      | Timing Diagram for a 4-Bit Serial-In, Parallel Out Shift Register in |     |

|      | Figure 3.24                                                          | 75  |

| 3.26 | General Form of a Sequential Iteration                               | 75  |

|      | Layout for a Sequential Iteration                                    | 76  |

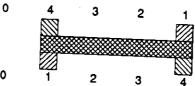

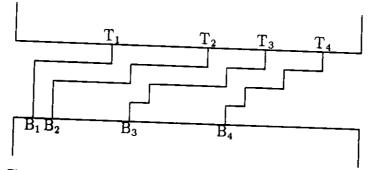

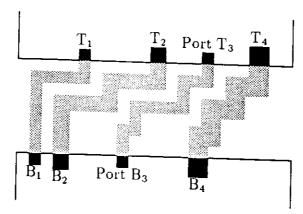

|      | A River Route with Two Bends per Wire                                | 78  |

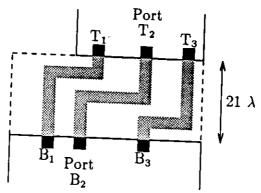

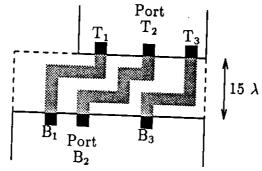

|      | A Minimum-Height River Route                                         | 78  |

|      | River Routing for an <i>n</i> -ary Tree                              | 79  |

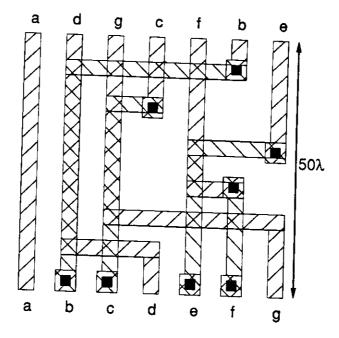

|      | Wide Datapath River Routing for an n-ary Tree                        | 80  |

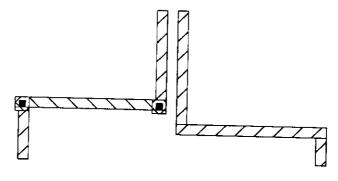

|      | A Route-Sinister and a Route-Dexter                                  | 83  |

|      | Simple-Minded Routing Strategy                                       | 84  |

|      | Simple-Minded Routing Strategy Blocks Routes 3 and 2                 | 84  |

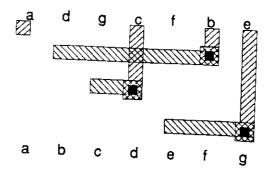

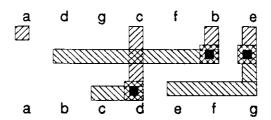

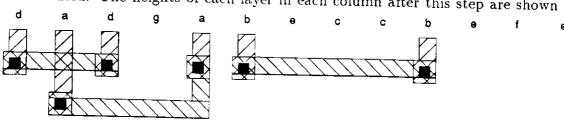

|      | Simplified Routing Step 1 for × 5 in Residue 1-of-7                  | 87  |

|      | Simplified Routing Step 2 for × 5 in Residue 1-of-7                  | 88  |

|      | Simplified Routing Step 3 for × 5 in Residue 1-of-7                  | 89  |

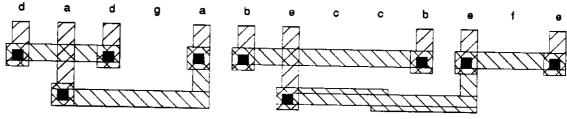

|      | Compressed Route-Sinister and Route-Dexter                           | 90  |

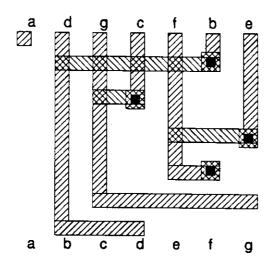

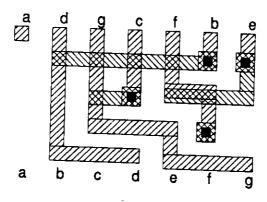

|      | Routing Step 1 for × 5 in Residue 1-of-7                             | 91  |

|      | Routing Step 2                                                       | 92  |

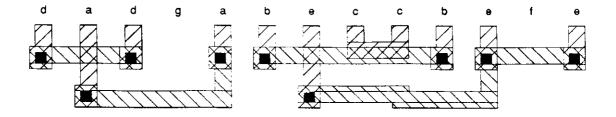

|      | Routing Step 3                                                       |     |

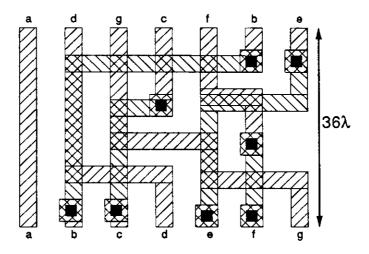

|      | Channel After Signals d, b, and a Have Been Routed                   |     |

|      | Channel Routing After Step 7                                         |     |

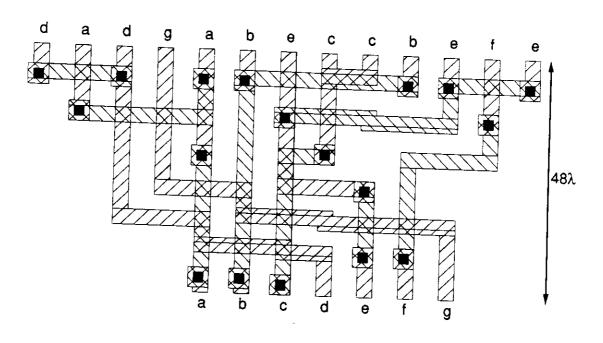

|      | Completed Multi-Port Signal Route                                    |     |

|      | A Channel Route for a One-to-Many Function                           |     |

|      | A Function Definition                                                |     |

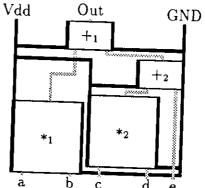

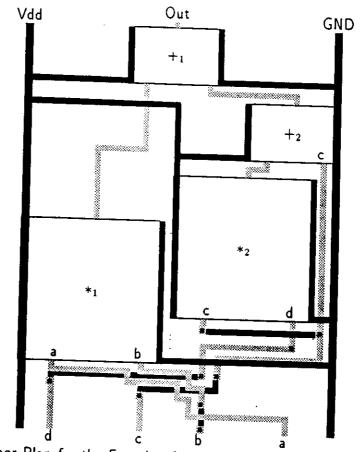

|      | Floor Plan for an <i>n</i> -ary Tree                                 |     |

|      | Floor Plan for the Function in Figure 3.46 with Power and Ground     |     |

|      | Another Function Definition                                          |     |

|      | Input Wire Permutation for *2                                        |     |

|      | Floor Plan for the Function from Figure 3.46 with Power, Ground,     |     |

| 3.02 | and Permuted Inputs                                                  | 106 |

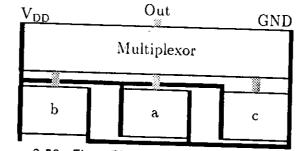

| 3.52 | General Form of an IF Expression                                     |     |

|      | Floor Plan for a General IF Expression                               |     |

|      | Floor Plan for a General CASE Expression                             |     |

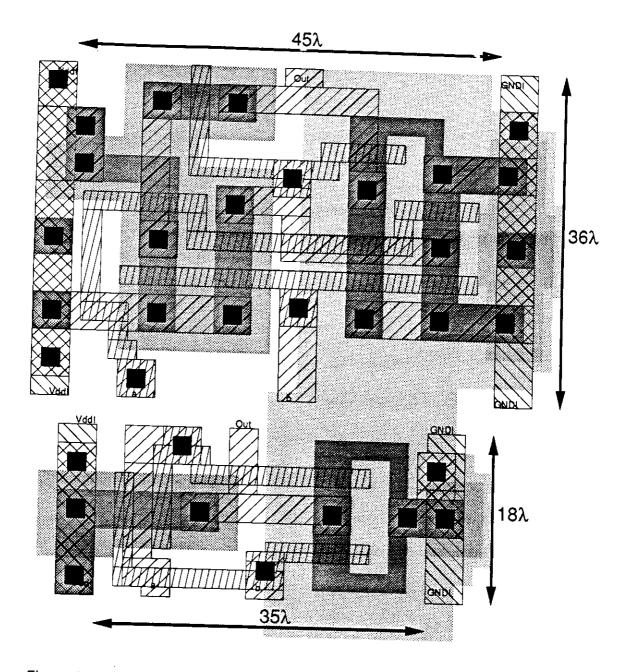

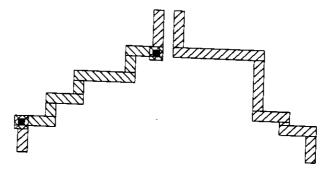

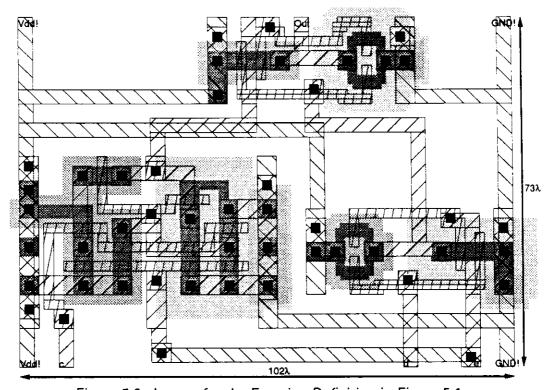

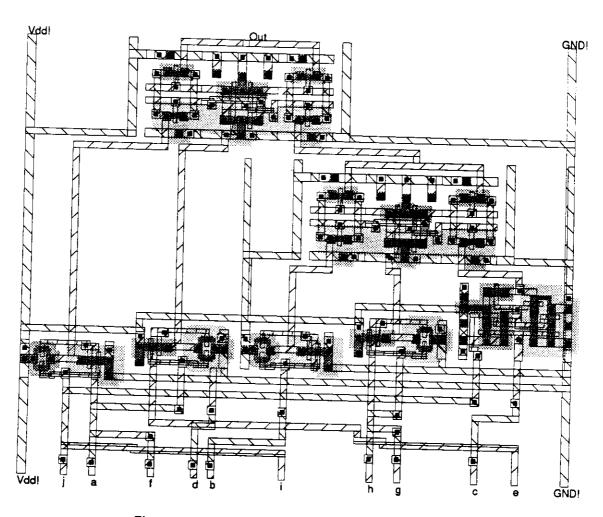

|      | Manually Laid Out Ripple-Carry Adder                                 |     |

| 2.33 | •                                                                    |     |

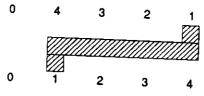

| 4.1  | River Routing Expressed as Lines on a Grid                           |     |

| 4.2  | River Routing with Differing-Width Wires                             | 122 |

| 5.1  | A Function Definition Containing Switching Expressions 129             |

|------|------------------------------------------------------------------------|

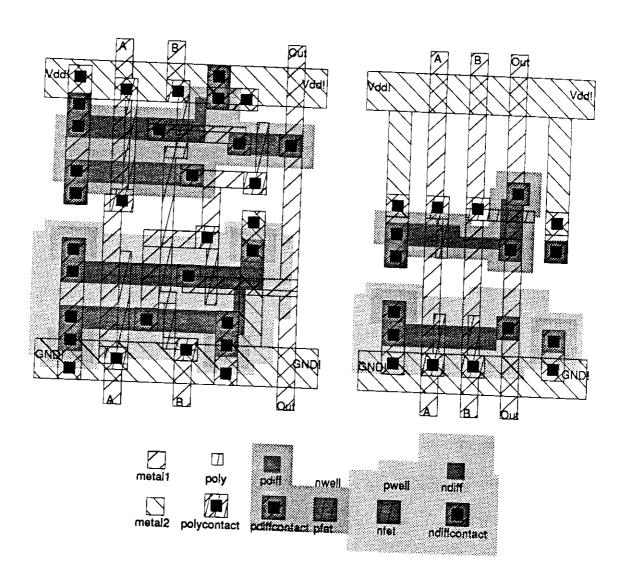

| 5.2  | Layout for the Function Definition in Figure 5.1                       |

| 5.3  | Specification of a Conditional Expression                              |

| 5.4  | Layout for the Function in Figure 5.3                                  |

| 5.5  | Definition of a Generic-Length Equality Operator                       |

| 5.6  | An Implementable Function                                              |

| 5.7  | A Specification for an Circuit for Computing Equals on Two Arrays      |

|      | of BITs                                                                |

| 5.8  | Eight-Bit Equals Using 2-Input Nands                                   |

| 5.9  | Definition of a Generic-Length Equality Operator Using 2, 3, and       |

|      | 4-Input Nands                                                          |

| 5.10 | Definition of a Generic-Length Equality Operator Using 2, 3, and       |

|      | 4-Input Nands (cont.)                                                  |

| 5.11 | Eight-Bit Equals Using 2, 3, and 4-Input Nands 141                     |

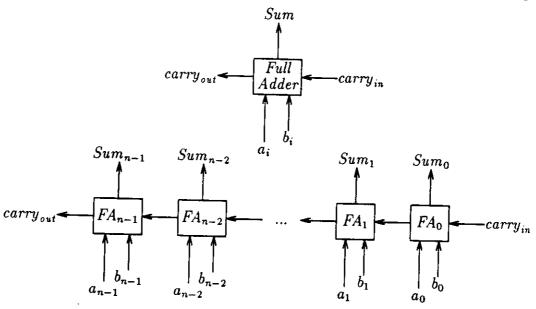

| 5.12 | Two's Complement Ripple-Carry Adder                                    |

| 5.13 | Functional Description of a Ripple-Carry Adder                         |

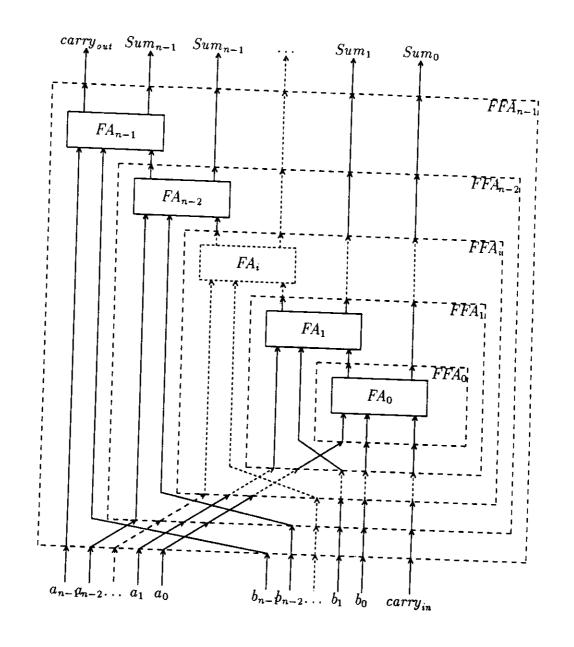

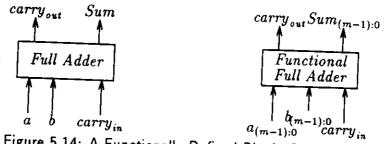

| 5.14 | A Functionally-Defined Ripple-Carry Adder                              |

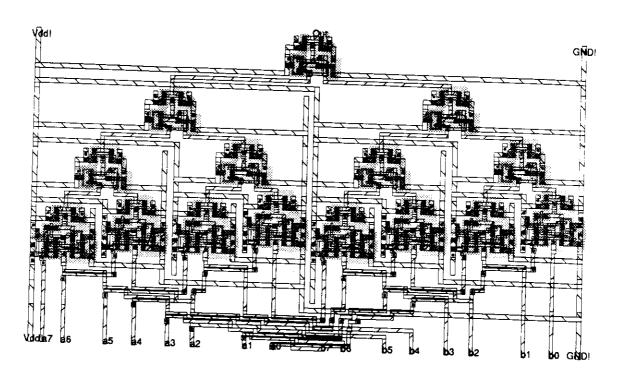

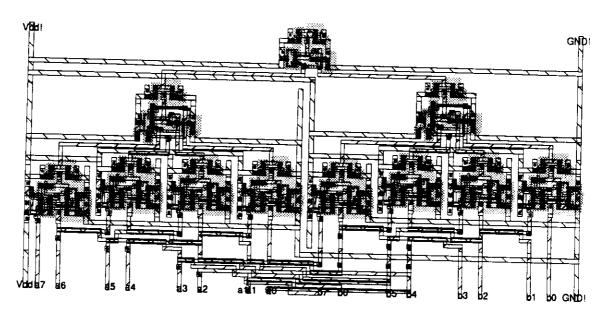

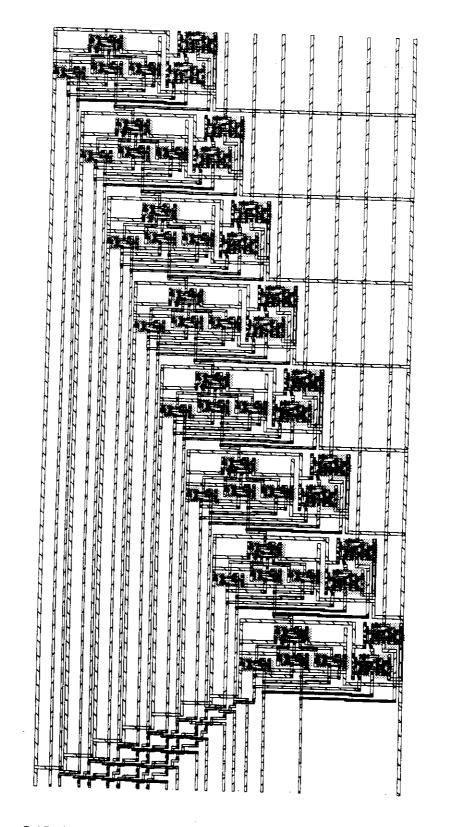

| 5.15 | Layout For an 8-Bit Two's Complement Ripple-Carry Adder 146            |

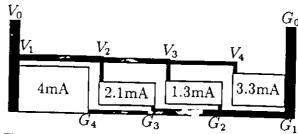

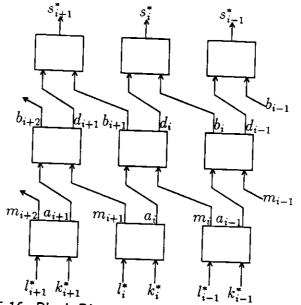

| 5.16 | Block Diagram for a Redundant-Digit Adder                              |

| 5.17 | Logic Equations for the Redundant Digit Adder                          |

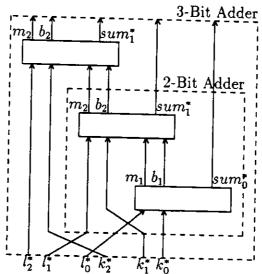

|      | Block Diagram for a Functional Three-Bit Redundant-Digit Adder . $150$ |

| 5.19 | Functional Description of a Redundant-Digit Adder                      |

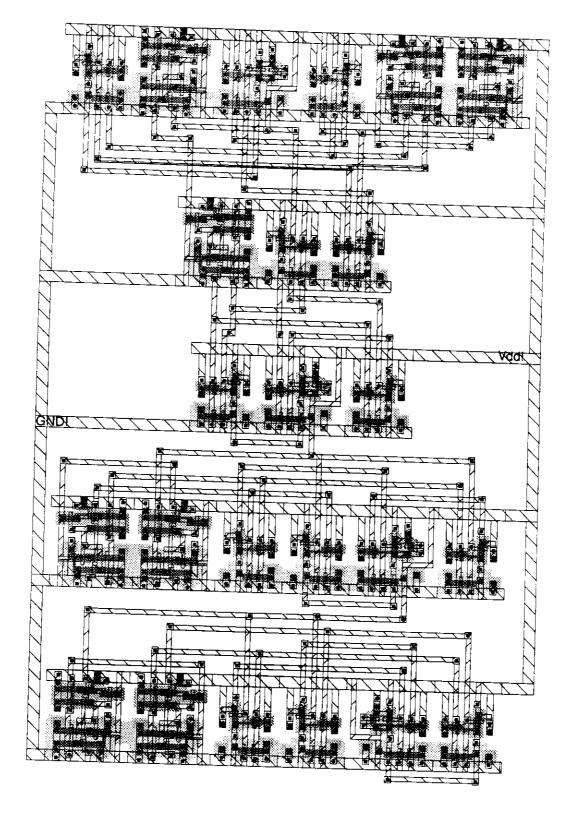

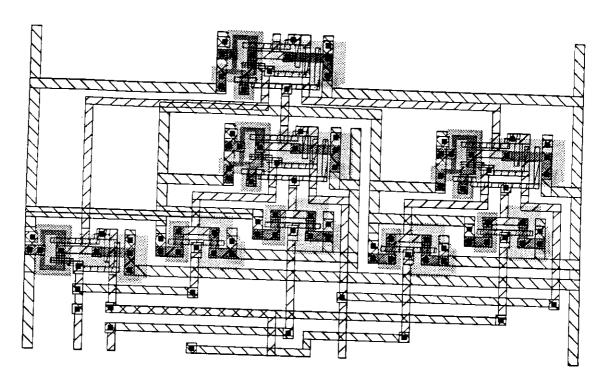

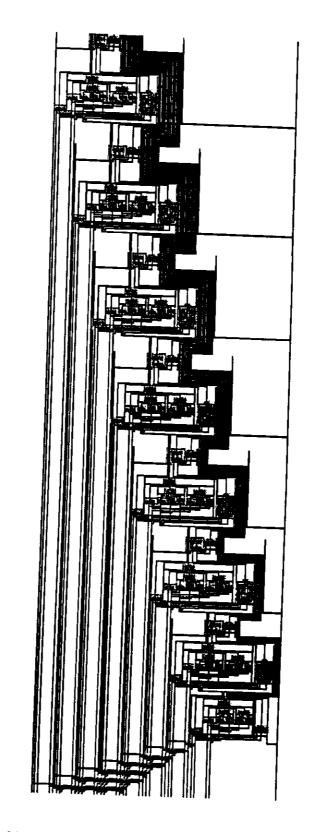

| 5.20 | Layout for an Eight-Bit Redundant Digit Adder                          |

# LIST OF TABLES

| 3.1  | Minimum Widths for Power and Ground Wires for Figure 3.14 66   |

|------|----------------------------------------------------------------|

| 3.2  | Lists of Ports                                                 |

| 3.3  | Lists of Ports                                                 |

| 3.4  | Initial Heights of L1 and L2 Layers in Each Column 96          |

| 3.5  | Heights of L1 and L2 Layers in Each Column After Step 4 97     |

| 3.6  | Heights of L1 and L2 Layers in Each Column After Step 5 98     |

| 3.7  | Lists of Ports after Step 5                                    |

| 3.8  | Heights of L1 and L2 Layers in Each Column After Step 6 99     |

| 3.9  | Heights of L1 and L2 Layers in Each Column After Step 7 100    |

| 3.10 | Heights of L1 and L2 Layers in Each Column After Step 8 100    |

| 3.11 | Top and Bottom Port Alignment Tests                            |

|      | Areas and Delays for Manually Laid-Out Ripple-Carry Adders 113 |

| 3.13 | Comparison of Areas and Delays for Automatically Laid-Out and  |

|      | Manually Laid-Out Ripple-Carry Adders                          |

| 4.1  | Complexity of Synthesis Algorithms Used                        |

| 5.1  | Areas and Delays for BIT-Array Equals Operators                |

| 5.2  | Areas and Delays for BIT-Array Equals Operators                |

| 5.3  | Areas and Delays for Ripple-Carry Adders                       |

| 5.4  | Encodings for Signed Digits                                    |

| 5.5  | Truth Table for Redundant Digit Adder                          |

| 5.6  | Complete Truth Table for Redundant Digit Adder                 |

| 5.7  | Areas and Delays for Redundant Digit Adders                    |

#### **VITA**

November 12, 1952 Born, North Hollywood, California

1976 B.S. Mathematics-Computer Science, University

of California, Los Angeles

1978 M.S. Computer Science, University of California,

Los Angeles

# **PUBLICATIONS**

Steven H. Kelem, A Compiler for Silicon: An Automatic Method for the Translation of High-Level Algorithms into Integrated Circuit Masks, Technical Report ATR-85(8497)-1, The Aerospace Corporation (September 1982).

Robert Cuykendall, Anton Domic, William H. Joyner, Steve C. Johnson, Steve Kelem, Dennis McBride, Jack Mostow, John E. Savage, and Gabriele Saucier, Design Synthesis and Measurement, VLSI \cap Software Engineering Workshop Report (October 1982).

Robert Cuykendall, Anton Domic, William H. Joyner, Steve C. Johnson. Steve Kelem, Dennis McBride, Jack Mostow, John E. Savage, and Gabriele Saucier, Design Synthesis in VLSI and Software Engineering, *The Journal of Systems and Software*, 4(1):7-12 (April 1984), This is a reprint of the workshop report.

John J. Helly, Jr., William V. Bates, Mel Cutler, and Steve Kelem, A Representational Basis for the Development of a Distributed Expert System for Space Shuttle Control, Technical Report, NASA, Houston, Texas (May 1984).

Steven H. Kelem, A Method for the Automatic Translation of Algorithms From a High-Level Language into Self-Timed Integrated Circuit Masks, Technical Report TR-0084A (5920-03)-1, The Aerospace Corporation (March 1985).

Steven H. Kelem, A Method for the Automatic Translation of Algorithms from a High-Level Language into Self-Timed Integrated Circuits, *IEEE Circuits and Devices Magazine*, 1(2):17-19,44 (March 1985).

Steven H. Kelem, A Method for Compact Two-Layer Routing of Permutations in Less Than n<sup>2</sup> Time, Technical Report TR-0086A (2920-03)-1, The Aerospace Corporation (February 1987).

#### ABSTRACT OF THE DISSERTATION

Synthesis of Custom Integrated Circuits

From a High-Level Behavioral Description

by

#### Steven Hennick Kelem

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 1987

Professor Bertram Bussell, Co-Chair

Professor Miloš Ercegovac, Co-Chair

This dissertation describes an innovative method for synthesizing error-free prototype integrated circuit masks from a behavioral-level algorithmic specification. The designer expresses algorithms and data types without having to specify a layout for their implementation or having to rely on time-consuming methods to obtain an implementation. The layout of the designed circuit is not explicitly specified by the designer, and it is determined from the algorithmic description. The circuits are produced quickly, but not necessarily as compactly as can

be done with exhaustive, time-consuming, automatic or manual techniques. The circuits produced are properly formed (i.e. obey the fabrication design rules) so non-behavioral attributes such as area, speed, and power can be estimated directly from these designs. When the data types in a design are changed, different operators corresponding to the new types are utilized and the non-behavioral attributes of the resulting circuit change. Comparisons of these attributes are the basis for choosing one design over others.

This method of designing digital circuits is intended to meet the needs of a specialized set of problems, namely the design of special-purpose computing circuits. Such circuits typically are non-standard designs which require many iterations in the design process to obtain a cost-effective design. Therefore a rapid-prototyping design method, mapping algorithms given at a high level into circuit structures is highly desirable. This work is motivated by these needs and attempts to provide such a design tool.

#### CHAPTER 1

#### Introduction

This dissertation proposes a novel solution to a fundamental problem in the design of special-purpose integrated circuits. Because such circuits are often non-standard, as are the subcircuits from which they are constructed, many iterations through the design process are needed to produce cost-effective designs. The hypothesis of this dissertation is that the higher the level of description, the easier it is for a designer to specify an algorithm that is to be implemented as an integrated circuit that meets an even higher-level requirement specification. A behavioral, functional level of description allows the designer to choose between variations on details of a given algorithm. Using existing design methods to determine whether a particular implementation of a functional description meets the design requirements is a difficult and lengthy task.

Many IC design systems translate logic or transistor schematics (or a textual equivalent) into IC masks. Specifying these schematics is a time-consuming and tedious process (even with the aid of a computer) and the schematic is not related closely to the algorithm that the schematic implements. If a data type or some other aspect of the algorithm is changed, it is often difficult to apply those changes to the schematic without changing much (or all) of the schematic. When a designer

implements an algorithm that will be on an integrated circuit, it is important for the designer to experiment with variations on the desired algorithm. Designers experiment to find a form of an algorithm that will fit in the desired area of a chip, meet the power budget for the chip, and operate at or above the desired speed. Other possible variations on an algorithm might result in a circuit that is more testable, fault tolerant, reliable, or temperature insensitive.

This thesis discusses a method for specifying an algorithm that will be implemented on a custom integrated circuit. The synthesis process described here has time complexity of less than  $n^2$ , and so scales well for large problems. The circuits produced by this method are not as area-efficient as manually-designed circuits. Once several variations on an algorithm are produced, a designer can select the few that best meet the specifications and then apply more exhaustive methods to make those variations more area-efficient.

To set the stage for the thesis, it is useful to examine the integrated circuit design process. An integrated circuit can be described at several different levels of abstraction. In top-down design, one starts with a very abstract description of the desired system and then carefully refines the description until the desired complexity is reached. The desired complexity for a complete description contains the target primitives or predefined descriptions that contain the target primitives. Some of the levels of abstraction for the systematic definition (refinement) of integrated circuits were given in [Cuyk82,Cuyk84] and are repeated here.

Requirements: The specification of the overall performance, area, and I/O for

the circuit.

Abstract Algorithms: The behavior of the circuit without a binding for the actual operations and data types.

Concrete Algorithms: The behavior of the circuit expressed in a machine-independent programming language. The operators and data types are specified.

Programming: The machine language for the circuit if it is programmable.

Register Transfer: The behavior described in terms of states during which data is transferred between registers in the circuit.

Logic: The circuit description in terms of logic components and their interconnections.

Discrete Circuit: Logic functions in terms of transistors, resistors, capacitors, etc.

**Topography:** A circuit in which physical dimensions are absent, but in which relative positioning is expressed.

Masks: Transistors are defined by the intersections of polygonal areas on masks that are used in the fabrication process for integrated circuits.

This list stops short of the steps required for integrated circuit fabrication.

Typically a design is specified at one of these levels, and one or more designs at a lower level is synthesized from that specification. If some of these designs meet the

requirements specification, then they can be further refined into lower-level designs. It is difficult to know whether a component of a design at some level of abstraction will meet the requirements specification unless it is designed down to some level where the design attributes can be measured, estimated, or simulated. Then they can be compared to the requirements specification. This means that integrated circuits have to be designed down to the mask level before a designer can determine whether the design meets the requirements. Unfortunately each transition between layers of abstraction results in many different design alternatives. If there were only two design possibilities at each of the seven levels, then 128 designs would have to be created and analyzed for adherence to the requirements specification. In reality, there are many more than two design possibilities at each level, and so the number of designs that need to be analyzed is enormous.

#### Mask Topography

Several techniques have been developed to reduce the number of design options at different levels of abstraction. At the lowest level of abstraction—the integrated circuit mask level, several efforts of note have resulted in techniques with fewer design alternatives for the production of IC masks. The first is the lambda-based simplified design rules [Mead80,Sequ82]. These rules have the following characteristics.

The number of fabrication layers available to the designer to design with is reduced.

- The interactions between fabrication layers is simplified.

- The designer's idealized masks are isolated from physical masks by the introduction of a scale factor named lambda (λ).

- All dimensions are integral multiples of lambda.

- Designs are isolated from peculiarities of individual IC manufacturers' design rules and fabrication lines.

Another method that has reduced the number of mask design alternatives is the gate array. These are large arrays of gates which have been fabricated except for the metal layers which serve to interconnect the inputs, outputs, and power. The gates are those which the manufacturer believes will be easily incorporated into a design. Typically the gates are as simple as transistors or multiple-input nand or nor gates. In any case, these gates are prearranged in two-dimensional arrays with space between the rows and columns for the designer-specified routing. The set of masks for the pre-fabricated layers of the gates are the same for all of the wafers for a gate array, and only the masks for the metal layers are customized for a particular design. This reduces the overall cost of producing the circuits since the cost of the pre-fabricated layers can be amortized over many designs.

## Topography

A method that reduces the number of design alternatives at the topographical level is a graphical method called *sticks* [Will77]. This method represents tran-

sistors and wires as thin lines instead of rectangles. Topological information is represented in the relative positions of the elements in a design.

## Logic and Topography

At the logic and topographical levels, some particular layouts are used to simplify design, which has the effect of reducing the number of design alternatives. These are *Programmable Logic Arrays* (PLA), *Standard Cells*, and *Datapaths*. PLA's are compact structures for implementing sums of product terms. With the addition of clocked registers, finite-state machines can be built from PLA's.

Standard Cells that are circuits laid out with a common height but may have differing widths. The cells are placed horizontally adjacent to one another. Cell rows are separated by wire routing which interconnects the functions' inputs and outputs.

A datapath is an organization at the system layout level. This results from the separation of data and control operators in a processor. These two sections are created separately and then the appropriate wires run between them. Usually all the data operators operate on the same sized data and so it is convenient to arrange all these operators in a row, or path, with buses running above and below the row.

## Silicon Compilers

Finally, at the higher levels of abstraction, there are several translation methods called *silicon compilers*. These compilers translate between different levels of abstraction. The only thing common to all of the silicon compilers is that they take a textual representation of a design at some level of abstraction and translate it to a design at a lower level of abstraction.

Johannsen's Bristle Blocks compiler [Joha78] enables a designer to specify an algorithm for defining the layout of cells and placing and routing these cells. His compiler synthesizes only cells that can be abutted, thus avoiding the routing problem. Cells are stretched vertically or horizontally so that the input and output ports on adjacent cells will line up when placed next to each other.

Similarly, Johnson's language Xi [John83] is an extension of the programming language C [Kern78] that allows a designer to specify algorithms for interconnecting cells. Assignment statements correspond to bindings to signals or registers. The output of xi is a list of cells and nets that are interconnected. This information is fed to a place and route program which searches exhaustively for a placement of the cells and a routing of the wires that interconnect them.

Ayres' language RELAY (REcursive Logic ArraYs) [Ayre79,Ayre83] is a language for describing behavior in terms of synchronous logic. RELAY, written in the general-purpose language ICL (Integrated Circuit Language) [Ayre79,Ayre83]. gives the designer full access to the ICL language. The logical formulae in the synchronous logic are translated into an optimized disjunctive form. From this

form, ICL is used to simulate the logic and to translate the logic into clocked PLA structures. RELAY programs are an unusual marriage between logic and layout. The designer needs to simultaneously specify a circuit's behavior and its geometric implementation.

The input to Hamachi's language PEG (PLA Equation Generator) [Hama85] is a specification of a finite state machine that is isomorphic to a Moore machine [Moor55]. States are explicitly described. Sequential state transitions are implicit in the ordering of the states in the specification. Non-sequential state transitions are explicitly stated. The finite state machines descriptions produced contain only the control and state portions of the machine.

Siskind, et al [Sisk81] produced a language and translator called *MacPitts*<sup>1</sup>. This language is at the register transfer level of abstraction, allowing specification of parallel communicating processes in a Lisp-like syntax. The target architecture is a combination of finite state machines, one for each of the parallel processes in the source code, and a data path unit. The datatypes consist only of the integer and Boolean types. A functional simulator detects simultaneous write attempts to the same register.

Patel, Schlag, and Ercegovac [Pate85,Schl84,Schl86] designed and implemented  $\nu FP$ , an extension of Backus' functional programming language, FP [Back78]. This allows the multi-level specification, evaluation, and synthesis of hardware from an applicative language. Layouts and routing at the schematic (block diagram)

<sup>&</sup>lt;sup>1</sup>MacPitts is not an acronym. The name is an "in-joke" of some sort.

level or at the mask level can be obtained. The applicative language is especially amenable to formal transformation methods. Transformations are applied to programs to reduce the overall area of a circuit and to improve routing.

Pangrle and Gajski have programs called *SLICER* (a state synthesizer) and *SPLICER* (resource allocator) [Pang86]. SLICER transforms an algorithm specified at the register transfer or concrete algorithm level into a dependency graph. It then performs a critical path analysis of the graph to find the longest path through the graph. When the critical path has been found, all computations in the algorithm are assigned to (possibly multiple) states. SPLICER then performs a (backtracking) algorithm to allocate resources (computational elements) to the different states. The backtracking aspect of this program might try all possible mappings between the computational elements and the dependency graph nodes. This program synthesizes a circuit with the least amount of resources while executing as fast as the critical path will allow.

The system described here takes a description written in a functional language and produces integrated mask specifications for prototyping. A fixed layout procedure is executed for each construct in the language, but these procedures include some heuristics that quickly find a viable layout. Fast routing techniques and the hierarchical nature of the language and specifications allow circuits to be synthesized quickly so that their speed, power, and area can be quickly determined.

## Design Correctness

If the synthesis process is manual (or automatic but not trustworthy), then it is necessary to ensure the process has been done correctly. This involves one of the following techniques.

verification A formal proof that certain properties hold in the both the source and target levels of abstraction.

validation Exhaustive simulation of both levels of abstraction and comparison of the results.

simulation Modeling both levels of abstraction at some subset of the possible input cases and comparison of the results.

The next chapter describes a language (ALICS—Algorithmic Language for Integrated Circuit Specification) for the specification of the behavior of algorithms to be implemented in integrated circuitry. The language is based on Algol 68 [Wijn75] and FP [Back78], with some features borrowed from  $\nu FP$  [Mesh85,Schl86]. The data-typing features and procedural organization were taken from Algol 68. Algol's general assignment operators (and main memory) were removed as in FP—assignment through the "von Neumann bottleneck" is not an easily specified operation. However, well-structured assignments are reintroduced inside sequential domains. Sequential constructs from  $\nu FP$  were unified into a single construct. This construct packages sequential behavior within a domain so that it appears to be functional from outside the domain.

The third chapter discusses the synthesis method. A method is given for efficiently analyzing an ALICS source program. This consists of lexical analysis, parsing, and the transformation of these expressions into a structural representation of the program. This structure is mapped onto a tree of interconnected cells that implement the functions in the program. A method is demonstrated for placing cells hierarchically and for routing of functions and conditional expressions. Efficient methods are defined for routing of permutations and one-to-many mappings. These mappings are needed for the routing of signals from a function's formal parameters to the points where the parameters are referenced. Finally, methods for measuring non-behavioral attributes of the designs and the validity of this prototyping method are discussed.

Chapter four shows the time complexity of the synthesis algorithm to be  $n^2$ . To be useful, a prototyping system needs to work quickly. The time complexity gives a good indication of how long it will take for a chip design to be synthesized from an algorithmic description. The complexity gives a more important indication of how much longer a larger design will take to be synthesized. A synthesizer might operate quickly for small designs, but if its complexity is exponential and the circuits are large, it will probably be infeasible to compare design alternatives. Less complex synthesis algorithms facilitate faster synthesis of large designs, and so more design alternatives can considered by a designer.

The fifth chapter illustrates the synthesis method through some examples. Features of ALICS are demonstrated a few at a time. First some simple switching

expressions are expressed in the context of an ALICS program. This shows how to declare operators and how to bind pre-defined circuitry with ALICS operators. Next the switching expressions are included inside conditional expressions. The third example illustrates the definition of an operator that will work on any length operand through the use of compile-time recursion. The next example shows the definition of an operand that makes the best use of available 2, 3, and 4-input nand gates in order to efficiently implement a reduction tree. Finally, the definition of new data types is illustrated with the definition of two types of adders. Simulation of the resulting circuitry allows trade-offs to be made between the two designs.

The concluding chapter summarizes the main ideas of the method, its implementation, and its key features. Several open questions and research topics are also identified.

#### CHAPTER 2

#### The ALICS Language

## 2.1 Relation of the Language to Hardware

This chapter discusses the relationship of the algorithmic language ALICS (Algorithmic Language for Integrated Circuit Specification) to the specification of hardware that is synthesized. ALICS is a programming language in which an abstraction of the desired digital behavior is specified.

The placement and routing of components on the target integrated circuit are not specified in the algorithmic language. Instead, this information is automatically derived from the specified behavior of each algorithm.

Each construct in ALICS has semantics that is either interpreted at compiletime or translated into circuitry which, when activated, implements the semantics of the constructs. The choice of which type of semantics depends not only on the individual constructs but on the actual values in the constructs.

## 2.2 Level of Description

ALICS is a means for expressing the digital behavior of the circuitry that will be built. ALICS supports hierarchical behavioral description. The lowest level of description is that of switching expressions and a form of state-machines. The highest level of description consists of the programmer-defined functions, similar to procedures defined in the programming language Algol 68. The levels of description result from applying the concept of modularity, which simplifies the specification of complicated programs. Modules are specified as function declarations. These facilitate the encapsulation of behavioral descriptions into units that are used as primitive functions in other functions, making these new functions easier for the designer to understand and use. This modularity, mapped into modules at the hardware level, is useful for designers and some analysis tools, but is not essential for the fabrication of the circuits.

The following sections discuss properties of the algorithmic language and of the target circuit architecture. A hardware designer might want to know about both of these if effective designs are to be produced. Knowledge of the algorithmic language is essential because the designs will be expressed in this language. A designer's knowledge of the target language is not as important as is proficiency with the algorithmic language, but, nonetheless, it is useful for the designer to know which types of circuitry are produced.

# 2.3 Algorithmic Language Features

The algorithmic language is the vehicle for specifying an algorithm that will be implemented by an integrated circuit. Before a designer can design an integrated circuit effectively, the capabilities of ALICS and the translator needs to be understood. The designer needs to know

- which kinds of algorithms can be expressed in the language,

- how to re-use previously-designed algorithms in the language,

- how good the resulting designs are, and

- the kinds of errors the system will catch.

The following features of a language determine which kinds of algorithms can be expressed in the language: data objects, data structuring constructs, operators, flow of control, flow of data, communication, and storage.

The major features of ALICS are presented next.

#### 2.3.1 Data and Data Types

An important part of a hardware specification language is the provision for specifying the datatypes of the entities in a design. In ISP [Barb79], the primitive datatype is the bit. The structuring constructs provide a way of forming an array of bits (called words) and then forming an array of words. Unfortunately for designers, it is not possible to treat these structures as data types, and so an ISP parser cannot detect type mismatches, except for the ones in which the number of bits differ. Thus, assigning a 32-bit stack pointer to an 8-bit character register would be detected as an error. However, assigning a 32-bit stack pointer to the 32-bit program counter would not be flagged as an error, even though it is unlikely to be a meaningful operation. Loading the program counter with a 32-bit program address addressed by the stack pointer is a sensible operation.

These three examples can be checked by declaring the stack pointer and program counter to be of the appropriate types in Algol 68. Algol 68 [Wijn75] has four basic data types (or modes, as they are called in the Algol 68 Revised Report)—integer, real, boolean, and character. The Algol 68 Revised Report makes the assumption that Algol 68 programs will be run on machines that support these types. When custom hardware is designed, it is often advantageous to use various numeric representations rather than the standard two's complement integer. These will affect non-behavioral characteristics such as speed, area, power, testability, reliability, and fault tolerance. Therefore, it is assumed in ALICS that the supporting hardware does not provide these datatypes since custom hardware is designed for which there are no standard representations or sets of operators. Instead, a facility for the definition of new datatypes is provided.

Algol 68's provision for describing any datatype and the operators that can operate on that datatype has been incorporated into ALICS. Once a datatype has been defined and operators designed to manipulate the datatype, the operators can be placed in a library for use in other designs. So while the integer, character, and real datatypes are not built into ALICS, there is the ability to define them when needed, or recall them from a library if they have already been designed.

The types of all functions' actual and formal parameters are checked for consistency to ensure that the proper types of values are passed to all functions. For digital circuits, it is important not only that outputs are connected only to inputs, but that the output types match the input types. The first consistency check is

specified in the syntax of ALICS and checked by its parser. Type-checking is the second semantic consistency check performed by the ALICS parser. For example, type-checking ensures that integer values are not passed to floating-point operators without proper conversion.

The Algol 68 Revised Report avoids discussing the representations for values. At a low-level of algorithm design, representation is of great importance. As mentioned before, a change in representation can result in operations that run faster, require less power or area, are more testable, reliable, or fault tolerant than a given implementation in two's complement (not all at once, of course). ALICS has two aspects to representing values, or constants. The first is how values are denoted. The second is how a value's representation is denoted.

Values are denoted as numbers in ASCII. The default radix is decimal, but can be changed by prepending the number with desired radix (expressed in decimal) and the character r. For example, the value 42 can be represented as 2r101010, 4r222, 8r52, 13r33, or 16r2a.

A value's representation is denoted as a list of the values that make up the representation. The target representation is in the domain of digital integrated circuits, where all values are groups of zeros and ones. This is represented in ALICS by the BIT datatype and the structuring mechanisms that enable more complex datatypes to be built (section 2.3.1). For example, the value 41 can be represented in radix arithmetic as MODULUS(1,2,1,6) with respect to the moduli (2,3,5,7), where the datatype called MODULUS can be defined to be a structure

of four arrays of bits. Each of the residues is represented in binary. The first array is defined with one bit; the second, two bits; and the third and fourth, four bits each. Another possibility for a representation of the value 41 in radix arithmetic is MOD\_OON(1,2,1,6) with respect to the moduli (2,3,5,7), where the datatype called MOD\_OON is defined to be a structure of four arrays of bits. Each of the residues can be represented in one-of-n code. The first array is defined with two bits; the second, three bits; the third, five bits; and the fourth, seven bits.

#### Defining New Datatypes

One of the most important features of this language is the support of extensible data-types. The designer can define new data types from existing data types through the use of one of four data type constructors—arrays (collections of homogeneous types, indexed by a numerical position) (also called rows), sequences (arrays whose elements are accessed monotonically sequentially), structures (collections of non-homogeneous types), unions (alternative types), and functions (executable code that take values from a set of types and returns a value of a given type).

#### 2.3.2 Arrays

Elements in arrays are numbered both to provide access to the elements and to provide an ordering for the elements. The numbering provides access to the elements in the array in a logical fashion, whether numbering of the elements is to be from the right or the left. What is considered a logical fashion depends on what type of data the array is modeling and how the denotations for values are to look like. Array indices increasing from left-to-right are more logical when the arrays contain time or western reading-order dependent data. In arrays containing weighted numeric representations such as radix number systems, the same order is useful for fractional numbers, while the opposite ordering is more logical for integers. A specification method and associated semantics for both of these specification styles are presented in Appendix A.

#### 2.3.2.1 Array Declarations

The syntax for an array declaration is shown in Figure 2.1. Where variable is

$[bound pair-list] \textit{MODE}\ variable$

Figure 2.1: Syntax of an Array Declaration

the variable name; MODE is the mode (data type) from which this array is built; and boundpair-list is a comma-separated list of boundpairs, one for each dimension in the array. A boundpair is a pair of bounds for an array consisting of a left and a right bound. There is no restriction on which bound should be the greater of the two. If one of the bounds is omitted from a declaration, it is assumed to be 1. For instance, in the declaration [4,-3:5,2:-4]BITS x the first bound is from 1 to 4, the second from -3 to +5, and the third bound is from +2 to -4. Thus x is a three-dimensional array of 252 BITs ( $4 \times 9 \times 7$ ).

#### 2.3.2.2 Array Denotations

Arrays of values are denoted as a parenthesized list of values that are separated by commas, e.g., (a, SKIP, a OR b, TRUE) is a one-dimensional four-element array of bits. The second element in this array is non-existent. Multi-dimensional arrays of bits can be described by specifying a list of bound pairs. An example of a two-dimensional value is

$$((b, 4+3, 8), (3, 5, -7), (-4, 17, -2), (0, 0, a+1)).$$

#### 2.3.2.3 Array Operators

The operators for array data types are now discussed. These consist of operators which extract attributes of an array (such as its bounds), operators for extracting elements from an array, and operators for constructing larger arrays from two arrays. The construction operators maintain the precision of the operands, as specified by the array bounds.

#### 2.3.2.4 LEB Operator:

The left-bound operator is both a monadic and a dyadic operator. The dyadic version takes two operands. The first operand is the boundpair number (from the left, beginning at one), and the second operand is an array. The monadic version takes one operand, the array, and returns all the left bounds for the array. For the declaration [4,-3:5,2:-4]BITS a, the following relationships hold:

**LEB** a =

$$(1, -3, 2)$$

1 LEB

$$a = 1$$

2 LEB  $a = -3$

3 LEB  $a = 2$ .

## 2.3.2.5 RIB Operator:

The RIB operator is similar to the LEB operator except that it returns the right-bound. For the declaration [4,-3:5,2:-4]BITS a, the following relationships hold:

RIB a =

$$(4,5,-4)$$

1 RIB a = 4

2 RIB a = 5

3 RIB a = -4.

## 2.3.2.6 LWB Operator:

The LWB operator returns the lower bound of an array. It is similar to the LEB operator except that it returns the smaller of the left and right bounds. For the declaration [4,-3:5,2:-4]BITS a, the following relationships hold:

LWB a =

$$(1, -3, -4)$$

1 LWB a = 1

2 LWB a =  $-3$

3 LWB a =  $-4$ .

## 2.3.2.7 UPB Operator:

The UPB operator returns the upper bound of an array. It is similar to the LWB operator except that it returns the larger of the left and right bounds. For

the declaration [4,-3:5,2:-4]BITS a, the following relationships hold:

UPB a = (4,5,2) 1 UPB a = 4 2 UPB a = 5 3 UPB a = 2.

#### 2.3.2.8 @ Operator:

The @ operator is called the revised lower-bound operator, and is a dyadic operator that creates a new copy of an array, changing only the lower-bound (not necessarily the left-bound). The corresponding upper-bound is also modified so that that there are still the same number of elements in the array. The first operand is the array whose bounds will be copied and modified, and the second operand is a one-dimensional array with as many entries as the first array has dimensions. If one of the revised lower-bounds is SKIP, the corresponding bounds is not modified. For the declaration [4,-3:5,2:-4]BITS a, a @(0,SKIP,0) has the bounds [0:3,-3:5,6:0].

#### 2.3.2.9 Array Element Access:

Elements of arrays can be extracted by subscripting the array. Subscripts are enclosed in square brackets following an array and select single items from the array. If the integer array variable c has the value

then c[1,1] = 2, and c[4,1] = 7.

#### 2.3.2.10 REV Operator:

The REV operator reverses the left and right bounds of an array. REV is both a dyadic and monadic operator. The dyadic version takes two operands. The first operand is the boundpair number, and the second is the array. The monadic version of the operator reverses all the boundpairs. For the declaration [4,-3:5,2:-4]BITS a, the following relationships hold.

REV a has bounds [4:1,5:-3,-4:2]

1 REV a has bounds [4:1,-3:5,2:-4]

2 REV a has bounds [1:4,5:-3,2:-4]

3 REV a has bounds [1:4,-3:5,-4:2]

## 2.3.2.11 APPEND Operator:

This operator provides an intuitive method for concatenating two arrays that represent numbers with weighted digits. The APPEND operator creates a new array by copying the second operand to the right of a copy of the first operand. The resulting array has a lower bound identical to the lower bound of the first operand. The new right bound is computed from the length of the new array extending in the direction of the boundpair of the first argument. If the direction of the second argument's boundpair is different from that of the first argument, the elements of the second array argument are copied in reverse order.

For example, two arrays can be appended as follows.

$$(1,0,2,3)$$

APPEND  $(0,0,4)$ @89 =  $(1,0,2,3,0,0,4)$

The array (0.0,4) (with bounds [89:91]) is appended to the right of array (1,0,2,3) (which has bounds [1:3]). The resulting array has the value (1,0,2,3,0,0,4), which has bounds [1:7].

Two arrays representing numbers in a weighted digit number system can be appended as follows.

$$REV(1,0,2,3)@0$$

APPEND  $REV(0,0,4)@89 = REV(1,0,2,3,0,0,4)@-3$

If the array represents a radix five number<sup>1</sup>, the append operation represents appending  $004 \times 5^{89}$  to the right of  $1023_5$ .  $004 \times 5^{89}$  is effectively scaled so that the high-order digit (0) will be in the  $5^{-1}$  position and then added to  $1023_5$  to yield  $1023.004_5$ .

The arrays in this example are (1,0,2,3) which has bounds [3:0] and (0,0,4) which has bounds [91:89]. The value returned from **APPEND**, is (1,0,2,3,0,0,4) which has bounds [3:-3].

#### 2.3.2.12 PREPEND Operator:

This operator provides an intuitive method for concatenating two arrays that might represent radix numbers. This is similar to the APPEND operator, except that the bounds of the second operand are preserved after the first operand is prepended to the left of the second operand.

The PREPEND operator creates a new array by copying the first argument to the left of a copy of the second argument. The resulting array has a right bound

<sup>&</sup>lt;sup>1</sup>The particular radix is irrelevant to the APPEND operator.

identical to the right bound of the second argument. The new left bound is computed from the length of the new array extending in the direction of the boundpair of the second argument. If the direction of the first argument's boundpair is different from that of the second argument, the elements of the first argument array are copied in reverse order.

For example, two arrays, not necessarily representing radix numbers, can be prepended as follows:

$$(1,0,1,1)$$

@0 PREPEND  $(0,0,1)$ @89 =  $(1,0,1,1,0,0,1)$ @0.

The array (1,0,1,1), (which has bounds [0:3]), is prepended to the left of array (0,0,1), which has bounds [89:91]. The resulting array has the value (1,0,1,1,0,0,1), which has bounds [96:102].

Two arrays representing radix numbers can be prepended as follows:

$$REV(1,0,1,1)@0 PREPEND REV(0,0,1)@89 = REV(1,0,1,1,0,0,1)@-3.$$

If the array represents a radix five number<sup>2</sup>, this represents prepending  $1023_5$  (131<sub>10</sub>) to the left of  $001 \times 5^{89}$ .  $1023_5$  is effectively scaled by  $5^{92}$  and then added to  $001 \times 5^{89}$  to yield  $1023001_5 \times 5^{89}$ .

The arrays in this example are (1,0,2,3), which has bounds [3:0] and (1,3,1), which has bounds [92:89]. The value returned from **PREPEND** is (1,0,2,3,1,3,1), which has bounds [95:89].

<sup>&</sup>lt;sup>2</sup>The particular radix is irrelevant to the PREPEND operator.

#### 2.3.2.13 slicing:

Slicing is the process of extracting a contiguous portion of an array. (This is known as a *subrange* in some languages.) Slicing is indicated by a list of ranges within square brackets. A range consists of two optional integer expressions separated by a colon. If one (or both) of these expressions is missing, it is replaced by the corresponding left or right bound. The new left and right bounds will be in the same order that is specified in the slice. The bounds cannot be reversed if one of the bounds is missing in the slice range.

When a slice is taken from an array, the boundpair is not adjusted automatically so that it has a revised lower bound of 1 if a revised lower bound is not specified<sup>3</sup>.

A slice accesses a contiguous portion of an array. The middle three elements of the array (2,3,5,7,11) can be selected with the operation (2,3,5,7,11)[2:4], yielding the value (3,5,7). This value is an array which has bounds [2:4], so that the operation (2,3,5,7,11)[2:4][3] will yield the value 5. The operation (2,3,5,7,11)[4:2] yields the value (3,5,7), which has the bounds [4:2]. If a bound in a slice is missing, the corresponding left or right (or both) bound is (are) used in its place. Thus, (2,3,5,7,11)[4:] yields the value (7,11), which has bounds [4:5].

<sup>&</sup>lt;sup>3</sup>The lower bound of a slice is automatically changed to 1 in Algol 68, but seems arbitrary. This has the effect of extracting the slice and performing a numeric shift on the resulting value. This malformation can be accomplished in ALICS with the revised lower-bound operator ©, defined here, if desired. In Algol 68, maintaining the array indices in a slice is awkward for the programmer because the indices need to be specified twice—once in the slice and again in the revised lower-bound.

#### 2.3.3 Sequences

Sequences provide a way to access elements of an array sequentially. The addition of time sequences to the functional language FP was discussed in [Mesh85].

Eight operators convert between arrays and sequences. The first four are necessary to access the two types of array organization. The remaining four operators can be derived from the first four, but are provided as a convenience for the designer. Four operators convert between arrays and sequences. Their names reflect the four ways to choose the first element of a sequence—leftmost, rightmost, lowest index, or highest index. The four sequence-to-array operators reflect the four ways to map the first element of a sequence into an array. This element can be either the lowest numbered or highest numbered element of the array, and the element can be in the leftmost or the rightmost position of the array.

PISOLE This monadic operator converts an array to a sequence, beginning with the lowest numbered element. (Parallel in, serial out, leftmost element first.)

PISORI This monadic operator converts an array to a sequence, beginning with the rightmost element. (Parallel in, serial out, rightmost element first.)

element of the sequence is the first in the sequence and becomes the leftmost array element. The left bound of the array is 1. (Serial in, parallel out. lowest index first becomes leftmost element.)

SIPOHILE This monadic operator converts a sequence to an array. The elements

of the sequence are assumed to arrive in reverse order, that is, last element (highest index) first. This last element of the sequence becomes the leftmost array element. The right bound of the array is 1. (Serial in, parallel out, highest index first becomes leftmost element.)

PISOLO This monadic operator converts an array to a sequence, beginning with the lowest numbered element. (Parallel in, serial out, lowest numbered element first.) This operator is equivalent to

IF LEB a < RIB a THEN PISOLE a ELSE PISORI REV a FI

PISOHI This monadic operator converts an array to a sequence, beginning with the highest numbered element. (Parallel in, serial out, highest numbered element first.) This operator is equivalent to

IF LEB a < RIB a

THEN PISORI REV a

ELSE PISOLE a

FI

SIPOLORI This monadic operator converts a sequence to an array. The first element of the sequence is the first in the sequence and becomes the rightmost array element. The right bound of the array is 1. (Serial in, parallel out, lowest index first becomes rightmost element.) This operator is equivalent to

#### **REV SIPOHILE a.**

SIPOHIRI This monadic operator converts a sequence to an array. The elements of the sequence are assumed to arrive in reverse order, that is, last element

(highest index) first. This last element of the sequence becomes the rightmost array element. The right bound of the array is 1. (Serial in, parallel out, highest index first becomes rightmost element.) This operator is equivalent to **REV SIPOLOLE a.**

Figure 2.2 shows the bit-by-bit application of the **OR** function on two arrays. The first line checks (at compile time) that the bounds of a and b are the same.

IF LWB a = LWB b AND UPB a = UPB b

THEN PAR i FROM LWB a TO UPB a

DO a[i] OR b[i] OD

FI

Figure 2.2: Parallel Application of OR to Two Bit Arrays

If there are n elements in each array, n **OR** operators will be instantiated for execution in parallel.

The parallel to serial and serial to parallel operators just introduced can be used to reduce the number of operator instantiations at the expense of longer execution time as is shown in Figure 2.3. The PISOLE operator converts a and

Figure 2.3: Serial Application of OR to Two Bit Arrays

b from parallel arrays to sequences. Each pair of elements in these sequences is input to the **OR** operator, and a new sequence is produced. This sequence is input to the **SIPOLOLE** operator which converts it to an array of the same size of a and b.

## 2.3.4 Structures

The second data structuring technique names and collects non-homogeneous types so that they can be manipulated as a single entity. Access to an individual field in a structure is through the name of the field. For example, a floating point number could be represented by the structure definition

# STRUCT (XS exponent; FRAC mantissa),

where XS is the type for the exponent and FRAC is the type for the mantissa (presumably, XS and FRAC are defined elsewhere). A structured value is denoted by the name of the structure type followed by a parenthesized list of comma separated fields. For example, the data type (mode) definition,

MODE FLOAT = STRUCT (XS exponent; FRAC mantissa)

treats the value FLOAT (ex1,frac) as a structure of type FLOAT. The OF operator takes a field name and a structure and yields the value of that field. So

# exponent OF FLOAT (ex1,frac)

yields the value of ex1.

#### 2.3.5 Unions

A union specifies that a formal parameter's value may be one of several data types. The declaration

FUNCTION foo = (UNION (FLOAT, INTEGER)parm)

states that the actual parameter to the function foo may be either FLOAT or INTEGER.

The type of a union is determined through the application of a conformity clause.

CASE parm IN

(FLOAT float\_parm): f1(float\_parm),

(INTEGER integer\_parm): f2(integer\_parm)

ESAC

This construction examines the data type of parm. If it is a FLOAT, then parm's value is associated with float\_parm and the function f1 is invoked with this value. If it is an INTEGER, then parm's value is associated with integer\_parm and the function f2 is invoked with this value.

## 2.3.6 Operators and Functions

There are three types of functions in ALICS—prefix monadic operators which take one argument, dyadic (properly called infix dyadic) operators which take two arguments, and functions which take zero or more arguments. The difference between operators and functions is entirely syntactic. Operators are used in infix formulae in which the relative priorities and associativities of the operators determine the structure of the computation. Operators are syntactically less powerful than functions, since operators can have only one or two operands. Operators are provided as a convenience to designers who prefer to read and write infix formulae. The parentheses in a functional expression determine the computational order. Thus an infix formula such as

#### a NAND NOT b NOR c,

is equivalent to the function description

## nor2(nand2(a,not(b)),c)

Functions and operators provide several capabilities in ALICS—most notably, modularity and replication of values. Modularity is important because it allows a reduction of the amount of code that needs to be written and the resulting programs are more easily understood. Commonly used code can be written once and then invoked as a function (module) in many places.

The second use for a function or operator is to replicate values. Functional languages do not allow simultaneous access to components of a composed value. For example, functional languages do not allow the value (a,c) to be created from a composed value such as (a,b,c) unless the composed value is passed to a function. Inside the function the value is referenced by its formal parameter name (number in FP) multiple times and the desired value computed and returned as the value of this function.

The syntax of a function is shown in Figure 2.4. In this figure name is the

FUNCTION name (parameter-list) function-type/mode: BEGIN function-body END

Figure 2.4: Syntax of a Function Definition

name of the function; parameter-list is the list of formal parameter declarations; function-type/mode is the mode, or type, of the value of the function; and function-body is the body of the function whose value is yielded as the value of the function.

A variation on this syntax allows BEGIN to be written as (and END as).

The syntax of an operator is shown in Figure 2.5. In this figure name is the

OP name = (parameter-list) operator-type/mode:

BEGIN operator-body

END

associativity name-list;

PRIO name-list = priority;

Figure 2.5: Syntax of a Operator Definition

name of the function—which is formed from uppercase alphabetic or a symbol formed from the characters +-\*/<>/ke!~?=:|. parameter-list is the list of one or two formal parameter declarations; operator-type/mode is the mode, or type, of the value of the operator; and operator-body is the body of the operator whose value is yielded as the value of the operator. A variation on this syntax allows BEGIN to be written as ( and END as ). The associativity of operators is declared as LEFTASSOC, RIGHTASSOC, or NONASSOC. The PRIO declaration is used for assignment of a priority (also known as precedence) of one to nine to a of list of operators. The higher the number, the higher the priority.

Operators have an additional property that functions do not have. An operator symbol can be overloaded, as in Algol 68 or Ada [Ada83], to provide multiple entendres for the symbol. This means that, for instance, the operator symbol plus-sign can be simultaneously associated with an operator that performs integer addition, and with one that performs floating-point addition, and with one that performs some other function on some other type of arguments. Which of these operators is actually invoked depends on the types of the arguments used in conjunction with the operator symbol.

#### 2.3.7 Flow of Control

Several types of flow of control (sequencing of operations) are available in AL-ICS: sequential, parallel, conditional, and limited forms of iteration and recursion.

Control flows sequentially through composed functions. In the expression f(g(x)), g(x) executes first. The value returned by g is then passed to the function f. In the expression a+b\*c, execution is sequential, beginning with the multiplication and concluding with the addition, according to the relative priorities of these two operators.

Parallel execution occurs in parallel clauses. Parallel clauses yield a vector of values, which may appear as an input to a function. For example, in the function call f(a+b, c+d), both additions are performed in parallel. The two resultant values are passed to the function f.

Functions are expanded at compile-time. A separate function is created on the chip for each instance in the functional specification. This is not always an optimum approach since some hardware might be idle part of the time.

There are two types of iteration—parallel and sequential. Parallel iteration occurs at compile time, replicating the iteration body. The bounds of a parallel iteration must be determined at compile time. Sequential iteration specifies repeated execution of the iteration body at run time. The sequential iteration construct specifies a state machine. User-defined variables comprise the state, which can be changed during initialization of the state and at the end of each iteration. The state changes and iteration output are computed from user-defined functions.

Only a limited form of recursion is handled by this method. Recursion is performed by interpreting functions at compile-time. Since chips have bounded area, recursions require fixed points that are calculable at compile time. This is not powerful enough for general recursive computations, but as is shown in Chapter 5, is useful in generic functions (functions that return varying-length results).

Storage is available only as part of the state in the ALICS sequential construct.

#### 2.3.7.1 Conditionals

There are two types of conditionals—one is based on a Boolean value, the other on an integer value. The first is the IF expression, whose syntax is shown in Figure 2.6, in which zero or more **ELIF-THEN** parts may be used. The semantics

IF a

THEN b

ELIF c

THEN d

ELSE e

FI

Figure 2.6: Syntax of an ELIF Clause in an IF-Expression