THE EVOLUTION OF FAULT TOLERANT COMPUTING AT THE JET PROPULSION LABORATORY & AT UCLA 1960-1986

Algirdas Avizienis David A. Rennels

June 1987 CSD-870022

#### **FOREWORD**

This report presents an overview of the origins and evolution of fault-tolerant computing during the years 1960-1986 at the Jet Propulsion Laboratory, Pasadena, California, and at the University of California, Los Angeles, California, U.S.A. A preliminary version of this report was presented at the Symposium on the Evolution of Fault-Tolerant Computing that was organized by IFIP Working Group 10.4 "Reliable Computing and Fault Tolerance" and took place on June 30, 1986 in Baden, Austria.

The entire text (except Appendix C) will appear as a chapter in the book "The Evolution of Fault-Tolerant Computing" that will be published by Springer-Verlag, Vienna, Austria in 1987. Appendix C consists of the paper "Design of Fault-Tolerant Computers" (reference [Aviz 67a]) that was presented at the 1967 Fall Joint Computer Conference in Anaheim, California. To the extent of our knowledge, this paper introduced the term "fault-tolerant computer" and the concept of fault tolerance into technical literature.

Algirdas Avižienis David A. Rennels June 5, 1987

# THE EVOLUTION OF FAULT TOLERANT COMPUTING AT THE JET PROPULSION LABORATORY

AND AT UCLA: 1960 - 1986

Algirdas Avižienis David A. Rennels

UCLA Dependable Computing and Fault-Tolerant Systems Laboratory University of California, Los Angeles, CA 90024, U.S.A.

# 1. Early Efforts at JPL

The Jet Propulsion Laboratory (JPL) is a research facility in Pasadena, California, that was founded by Professor Theodore von Karman of the California Institute of Technology as a test site in 1936 and was supported by the U.S. Army until October 1958, when it was transferred to the recently founded NASA, the U.S. National Aeronautics and Space Administration. The primary mission of JPL within the NASA structure is to develop unmanned interplanetary spacecraft and to conduct scientific investigations of the other planets of our solar system. Unmanned investigations of the Moon by Ranger spacecraft were the first step in the series of space exploration missions that have continued with the Mariner, Viking, and Voyager series of interplanetary spacecraft that thus far have reached Mercury, Venus, Mars, Jupiter, Saturn and Uranus.

Until 1958 the task of JPL was the development of guided rockets for the U.S. Army (the Corporal and Sergeant series) that offered interesting dependability problems of their own. Upon arriving at JPL in July, 1955 as a recent M.S. graduate from the University of Illinois, A. Avižienis was assigned to solve the problem of dependable guidance parameter insertion in the new Sergeant system. The previous Corporal system employed hand-set dials within the rocket's guidance compartment that did not provide any verification of settings. The design for the new Sergeant system employed a system that read a punched card in a remote command post, transmitted the readings to control a stepping motor in the guidance compartment, and then independently read back the settings to the command post, where they were matched against the card to verify that the proper setting had been accomplished. This custom-tailored error detection mechanism employed relay logic for its control and identified several dependability issues that reemerged a few years later in the context of spacecraft guidance and control computing.

Dependability issues for spacecraft computing emerged at JPL after its transfer to NASA in 1958. A. Avižienis encountered them soon after returning to JPL from a four-year educational leave with a Ph.D. earned in May, 1960 at the Digital Computer Laboratory of the University of Illinois, where he designed parts of the ILLIAC II arithmetic unit and did thesis research on high-speed signed-digit arithmetic that did not address dependability problems. The problem that was perceived at JPL was the need for longevity of the spacecraft computer: unmanned interplanetary missions of 1 to 10 years duration were being considered, while the mean-time-to-failure of contemporary guidance computers was measured in fractions of a year. The NASA-specified OAO satellite on-board processor employed component redundancy that was not suitable for integrated circuits, while the SATURN V guidance computer employed a TMR CPU and was designed for a mission length of 250 hours [Kueh 69]. Both designs from the IBM Federal Systems Division at Owego, N.Y., provided valuable insights, but did not offer a solution to the problem of unattended operation for several years, with the critical performance demands coming at the very end of a long mission that leads to the flyby or orbiting of a planet.

Late 1960 marked the beginning of a multi-year research effort at JPL. It was the search for an effective solution to the problem of building a long-life onboard information processing system for unmanned spacecraft. A. Avižienis was the only full-time researcher for the first three years, working with the support of research group supervisor John J. Wedel, Jr. and with expert advice on spacecraft design, guidance, control, and computing from members of JPL Section 341 ("Flight Computers and Sequencers") and other members of JPL technical staff.

Valuable information on the SATURN V computer was gained during visits to NASA Marshall Spaceflight Center in Huntsville, AL, and to IBM Federal Systems in Owego, N.Y. Supporting research on the application of error detecting and correcting codes in system design was done under a contract with the Stanford Research Institute, Menlo Park, CA., by Dr. William H. Kautz and others. Two meetings also provided new breadth of viewpoint: a small Conference on Diagnosis of Failures in Switching Circuits (17 talks, 54 participants) in May, 1961 at Michigan State University, and a well-attended (over 500 participants) Symposium on Redundancy Techniques in Computing Systems held in Washington, D.C., on February 6-7, 1962. The latter consisted of 23 presentations that ranged from solid results to sketchy suggestions and philosophical discourses [Wilc 1962].

### 2. The STAR Computer at JPL

Existing theoretical studies of the long-life problem indicated that large numbers of spares offered a promise of longevity, given that all spares could be successfully employed in sequence [Reed 62]. The JPL problem was to translate the idealized "spare replacement" system model into a flightworthy implementation of a spacecraft guidance and control computer. About one year after rejoining the JPL staff, A. Avižienis submitted on October 6, 1961 a tenpage JPL Interofffice Memo to Henry A. Curtis, the Manager of Section 341, outlining the design of "a Self-Testing-And-Repairing System for Spacecraft Guidance and Control", designated by the acronym "STAR". The proposal was fully supported by JPL and NASA research management, and the research effort continued for more than ten years, culminating with the construction and demonstration of the laboratory model of the JPL-STAR computer [Aviz 71a].

The above reference and many other publications have adequately documented the final design of the JPL-STAR computer, and it shall not be detailed here. However, an interesting view of the STAR system evolution may be gained from the October 6, 1961 JPL memo that is reproduced as Appendix A to this paper. The memo has been used as evidence for the patent application filed by JPL in 1967 that resulted in U.S. Patent No. 3, 517, 171, "Self Testing and Repairing Computer", granted on June 23, 1970 to A. Avižienis and assigned to NASA, but it has not been previously published.

The 1961-1965 interval of STAR research was dedicated to the evolution of system organization concepts and an in-depth study of error detection techniques that led to the evolution and adoption of low-cost arithmetic error codes in the STAR design. The AN, residue, and inverse residue arithmetic error codes were investigated and developed [Aviz 71b]. In 1963, Allen D. Weeks joined the STAR effort as a logic designer and John Buchok as a senior technician. In June of 1965 David A. Rennels, then a doctoral student at Caltech, accepted a summer position with the STAR project and worked on the design and construction of a byte-serial arithmetic unit for "AN"-coded 32-bit operands with the check constant A = 15 [Aviz 73]. D. A. Rennels rejoined the STAR project in 1966 to serve as the principal hardware designer, and later as the main evaluator of the STAR laboratory model, conducting numerous coverage evaluation experiments [Aviz 72], [Renn 73a].

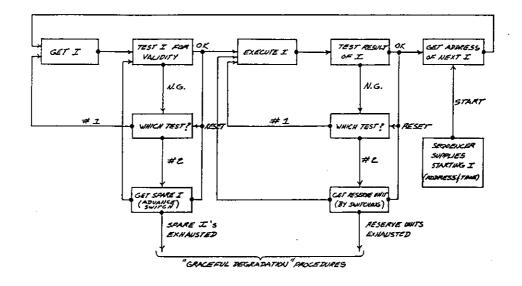

The initial goal of the STAR design was to place the test and repair features into hardware; however, as the design evolved, it became apparent that a hardware-software interface had to be devised to enable the implementation of program rollbacks. To develop the software, the STAR team recruited John A. Rohr, then a Ph.D. student and ILLIAC III software designer at the University of Illinois. He joined JPL in September, 1967 and served as the principal software designer to the end of the STAR project. His work produced a programming system (assembler, loader, simulator, executive), a programming manual, test and demonstration programs, and culminated with the development of STAR rollback techniques and a system executive program that interfaced with the hardware features [Rohr 73a], [Rohr 73b]. The first program was successfully executed on the STAR laboratory "breadboard" model in 1969.

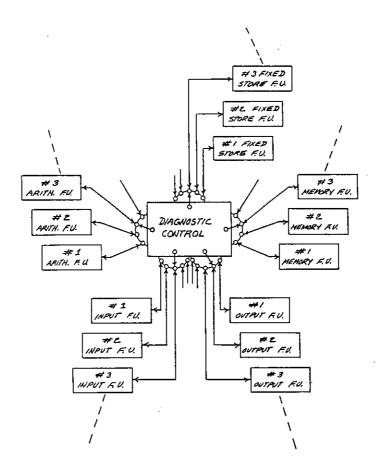

Publication of STAR papers was held back until the design was well defined; the first description was presented on request at a NASA-sponsored meeting in October, 1966 [Aviz 66]. The Central Control Unit described there and later renamed as the Test-And-Repair Processor TARP [Aviz 71a] was quite probably the first appearance of the Service Processor concept. The characterization of the computer as "self-repairing" appeared to be too specific and the term "fault-tolerant" was devised for all subsequent descriptions, beginning with a paper on "Design of Fault-Tolerant Computers" at the 1967 Fall Joint Computer Conference [Aviz 67]. This paper introduced the term "fault-tolerant" and the concept of fault tolerance into technical literature. Several technical papers dealing with various aspects of the STAR design followed during the next six years [Aviz 68], [Aviz 71a], [Gill 72], [Renn 73b], [Rohr 73b], [Aviz 73].

Additional research efforts were initiated in 1968, with Francis P. Mathur undertaking reliability modeling studies [Math 70a], [Math 70b], [Math 71] and George C. Gilley investigating the systematic extension of STAR techniques for the automatic maintenance of an entire autonomous interplanetary spacecraft [Gill 70], [Gill 72]. An adaptation of the STAR design to a specific application was carried out for the JPL Thermoelectric Outer Planet Spacecraft (TOPS) that was intended for the 15-year "Grand Tour" flyby of four outer planets of the solar system [A&A 70]. David K. Rubin led the effort, with support from the entire STAR team. Two elements of the STAR breadboard were designed outside of JPL. A highly reliable magnetic power switch was developed by the Stanford Research Institute, Menlo Park, Calif., and a fault-tolerant read-only memory was built by the M.I.T. Instrumentation Laboratory, Cambridge, Mass., under contracts from JPL.

Regrettably, deep cuts in NASA budgets for unmanned space exploration led to the termination of the TOPS project in 1972, and research on the STAR system breadboard itself was ended in 1973. The STAR system remained in the laboratory as a utility computer for subsequent research until July, 1977, when it was "mothballed" in a JPL storage facility. The California Museum of Science and Industry requested the STAR computer for an exhibit in 1983; however, it could not be located in storage, and its fate remains unknown.

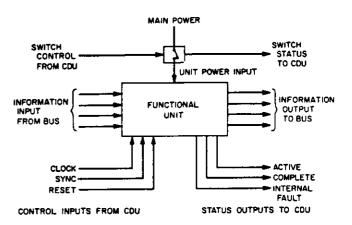

The only apparent direct descendant of the JPL-STAR fault-tolerant architecture was the Fault-Tolerant Spaceborne Computer (FTSC) [Burc 76]. The architecture of FTSC is the joint result of two architectural studies [Conn 72], [Stif 73]. The STAR contribution came through the study done at Ultrasystems, Inc., Irvine, CA. [Conn 72]. The effort was directed by R. B. Conn, while STAR designers A. Avižienis, D. A. Rennels, and J. A. Rohr served as principal consultants in this study, sponsored by the U.S. Air Force. This study updated the STAR architecture by taking into account the increasing levels of circuit integration and combined all processing into a single replaceable CPU. The TARP was significantly refined and designated as the CCU (Configuration Control Unit). A second iteration of the design led to a duplication of the CPU for improved error detection. The complexity of the CCU was reduced by using the CCUs to monitor the pair of CPUs, and relegating to the CPUs the monitoring and recovery management of the rest of the system.

The study done at Raytheon [Stif 73] contributed a single-error correcting and burst-error detecting code in the memory and for bus transfers, as well as single bit-plane replacement within a memory module by means of a "rippler" switch. The STAR approach to pooled memory sparing and assignment was retained. Two "brassboard" models of FTSC were built by Raytheon and were evaluated by extensive fault injection tests [Burc 76]. However, the design needed about 20 custom-designed and radiation-hardened LSI chips. The rapid development of microprocessors made the FTSC single-processor custom design excessively costly to implement for space applications, and the project was terminated before any flight-qualified machines could be built.

D. A. Rennels took over the lead role in fault tolerance research at JPL in 1972. At that time, A. Avižienis initiated a major research project in fault-tolerant computing at UCLA, which is described in the second half of this paper. He also remained in a supporting role as an Academic Member of Technical Staff at JPL until 1981, collaborating with D. A. Rennels and others on some of the subsequent projects that are described below. Contributions of the STAR project were noted by the awarding of the biannual Information Systems Award of the American Institute of Aeronautics and Astronautics in 1979 and of the NASA Exceptional Service Medal in 1980. While both awards were given to A. Avižienis, they actually recognized more than a decade of dedicated effort by a diversely talented group of contributors, who demonstrated the feasibility of building fault-tolerant long-life systems for autonomous operation.

# 3. After STAR: Fault-Tolerant Distributed Systems at JPL

In the STAR computer hundreds of SSI/MSI chips were needed to make a single processor. Therefore the processor was subdivided into three simpler functional units (each with several hundred SSI/MSI chips), and the memory was subdivided into 4096-word modules. By 1970, major improvements were anticipated in component technology, and it was clear that single-chip processors would soon be available for flight computers. JPL spacecraft were already being designed with several independent digital controllers for command, telemetry and attitude control processing. It could be expected that small general purpose computers would take over these functions and also be embedded in various payload subsystems. It was clear that the next step in computing technology would lead to distributed systems for spacecraft on-board computing.

# 3.1 The Unified Data System (UDS)

The Unified Data System (UDS) project was begun in the early 1970s as an attempt to define and breadboard a distributed computer architecture to be used on the next generation of spacecraft. At that time the STAR investigation had been concluded, and A. Avižienis was directing a research effort at UCLA. The principal architects of the UDS system were D. Rennels, V. Tyree and B. Riis-Vestergaard. The architecture consisted of a set of computer modules connected by a redundant set of serial busses. Computer modules were of two types, High Level Modules (HLM) and Terminal Modules (TM). This approach made an important distinction between those (HLM) computers which supplied shared global functions (e.g. system executive, telemetry formatting, data analysis) and those (TM) computers which would be embedded in spacecraft subsystems and used for local control and data handling. HLMs were connected only to the buses, were non-dedicated and could be backed up by a common pool of spares. TMs had specific I/O lines to the subsystems in which they were embedded and had to be backed up by dedicated spares which had the same custom I/O connections [Renn 76].

The spacecraft for which this system was designed operated with a synchronous executive. All activities were time-driven. Each computing function was carried out in periodic intervals and all functions were synchronized much like gears on a clock. For example, a television picture was taken every 48 seconds, another instrument would go through eight 6-seconds cycles every picture cycle, etc.

A number of novel features were included in the design of UDS to enhance its reliability [Renn 78a]. A key element was to make its operation simple, predictable, and verifiable. We observed that although the system was required to satisfy hard real-time timing constraints, the minimum resolution on timing of inputs and outputs of various subsystems was a multiple of a basic period of several milliseconds. A real-time interrupt was supplied to all computer modules to define the minimum RTI interval. Inputs were sampled and held over specified intervals (of one or more RTIs) and all outputs were changed only at the end of the intervals. As a result, collections of computations could be treated as atomic events in the specified time intervals. They could be executed in any order with exactly the same results, and unused time could be inserted in each interval to allow an error recovery to occur without changing the input-output characteristics of the computations. Previous spacecraft computers were interrupt driven, making simulation expensive and the system response much less predictable because it was more dependent on the ordering of closely timed events. This approach made the system more predictable and simplified verification of its programs.

Another basic approach was to view the purpose of subsystem-embedded computers as a mechanism to create virtual subsystems which simplified system interfaces and reduced timing constraints on the buses interconnecting the computers. To guard against error propagation due to software errors, the subsystem-embedded Terminal Modules (which were expected to be supplied by subcontractors) were not allowed to initiate bus transmissions. Instead, the High Level Modules moved data between designated memory areas in the TMs on a periodic basis and checked on its validity. A software executive was developed by H. F. Lesh which provided scheduling of tasks in the various computer modules. A PDL-like specification language was used, augmented by timing constructs such as WAIT, WHEN, BACKSTART to suspend and reactivate programs in appropriate synchronization [Lesh 76].

A distributed microcomputer breadboard was constructed and programmed to simulate a Mariner-class spacecraft. There were two HLMs: one dedicated to spacecraft system executive and command, and another to telemetry and control of data movement between computers. TMs were implemented to control a flight television camera, a tape recorder, and the uplink-downlink functions. The breadboard was demonstrated taking a picture of an image across the lab, shipping it out as a digital telemetry stream, and displaying it on a monitor. This research breadboard was a precursor to a distributed computer system which will soon fly on the Galileo mission to Jupiter.

This research resulted in a better understanding of the system-level issues in a distributed real-time system. The approaches used for a fault-tolerant bus system, the techniques for fault containment, the hierarchic control strategies developed to simplify and reduce time-criticality of intercommunications, and special features of the system executive all apply to contemporary spacecraft systems. They were used later in the JPL Fault-Tolerant Building Block Computer (FTBBC). Due to limited resources, the UDS design assumed concurrent fault detection in processors but did not attempt to implement it in the breadboard. The subsequent FTBBC program addressed this issue.

# 3.2 The Fault-Tolerant Building Block Computer

In the mid 1970s, Reeve Peterson of the Naval Ocean Systems Center (NOSC) was managing a program in VLSI development, and was interested in developing circuits for fault-tolerant systems. He was interested in the possibility of producing fault-tolerant VLSI-based computers which could last throughout the operational life of their host systems and provide "maintenance-free missions." A joint program sponsored by NOSC and NASA was initiated. An architecture was developed by D. Rennels which resulted in a breadboard of the FTBBC [Renn 78b].

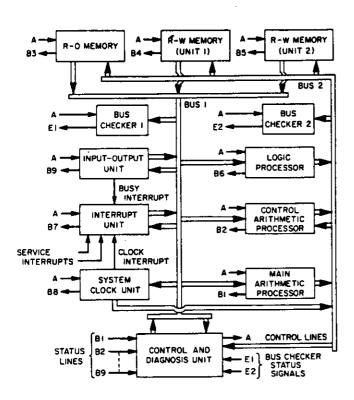

The JPL Fault-Tolerant Building-Block Computer (FTBBC) architecture was designed to use a small set of VLSI building-block circuits to interconnect existing microprocessor and memory chips to form Self-checking Computer Modules (SCCM). The SCCMs were designed to contain redundant communications interfaces which allowed them to be connected with other active and spare (SCCM) computers to form a fault-tolerant distributed system. Self-checking (morphic) logic design was used throughout the SCCM design to provide concurrent fault detection in each SCCM computer module. Four building-block circuits were designed: (1) a Memory Interface building block, (2) an I/O building block, (3) a Bus Interface building block which allowed the SCCMs to be connected with similar SCCMs into a network, and (4) a Core building block which compared the outputs of two (duplicate) processors, checked information on internal buses for proper coding, and collected fault messages from other building blocks. After detecting a fault the Core could initiate a program rollback to correct transient faults, and disable the SCCM if the fault persisted, indicating a permanent fault. A breadboard SCCM was constructed, and experimental fault insertion was carried out which verified the concurrent fault detection capabilities of the SCCM. Faults were inserted into both the operational logic and the check circuits by shorting randomly selected wires to ground [Renn 81].

The design used a redundant set of MIL-STD-1553A buses for fault-tolerant intercommunication, and a local executive similar to the UDS design was employed. I/O and software scheduling was synchronized by a real-time interrupt as in UDS. The majority of SCCMs were standby redundant, but the system executive function was duplicated in two SCCMs, so that if one failed, the dedicated backup could continue system control without excessive delays and loss of system state information. Only a single SCCM was constructed, therefore the distributed system has not been tested experimentally. An SCCM with a backup spare was used as a baseline fault-tolerant processor in an autonomous satellite study conducted by JPL for the US Air Force. Fault detection mechanisms and redundant elements were added to a USAF satellite design, and automatic recovery algorithms were written for the SCCM [Aren 83]. David Eisenman was responsible for much of the algorithm development and software architecture of this system.

#### 3.3 Current Research Issues

The FTBBC design is characterized by the use of redundancy at several levels. Spare (memory and processor) chips can be employed within SCCMs to enhance their reliability. Similarly, redundant I/O and memory modules can be employed within each SCCM. Fault tolerance is achieved by also employing spare SCCMs within the network. The use of redundancy at several levels has been found to be necessary in order to achieve long unattended life with a moderate amount of spare hardware. This presents difficult reliability modeling problems, since subsystems with internal redundancy no longer have constant failure rates, and Markov models become very large. Modeling multi-level redundant systems has been shown to be an important new research issue. Similarly, the implementation of concurrent fault detection using self-checking logic raises new VLSI design issues.

In the early 1980s, a program was initiated at JPL to develop methodologies to design self-checking VLSI circuits which also are self-exercising. The goal was to develop a computer which in addition to having concurrent fault detection, also exercises its internal circuits in such a way as to flush out latent faults within milliseconds (concurrently with normal operation). The approach was to modify generic VLSI circuits used in self-checking computer design and add internal self-exercising features to expose both transient errors and permanent faults quickly. Existing circuits for concurrent fault detection were used to detect the faults which are exposed. A self exercising memory design was presented at FTCS-16 [Renn 86a]. Preliminary results indicate that, given that concurrent fault detection is implemented, the additional use of self-exercising design is both effective and relatively inexpensive.

In 1986, NASA support was shifted from fault-tolerant computing to the development of a dataflow machine, so at the current time JPL is assisting other government agencies in the development of fault-tolerant computers. This program involves assisting in program planning and conducting small technology development activities at JPL. Current activities involve evaluating the fault tolerance potential of several existing high-performance architectures, as well as developing and evaluating design approaches for implementing fault tolerance in them. An evaluation of fault-tolerance issues in Hypercube architectures was completed and alternative design approaches have been proposed [Renn 86b].

# 4. Fault Tolerance and Dependable Computing at UCLA: 1962-1986

#### 4.1 The First Decade: 1962-1972

By 1960 Professor Gerald Estrin at the University of California, Los Angeles, (UCLA) had initiated research on the very stimulating and advanced concept of the "Fixed-plus-Variable" computer architecture. After a few exchanges of visits and presentations between JPL and UCLA, A. Avižienis joined the UCLA Department of Engineering faculty and Dr. Estrin's project in September of 1962 and started teaching undergraduate and graduate courses on computer system design and computer arithmetic, while also directing research at JPL. He presented the first formal course on fault-tolerant computer design at UCLA in 1966, and this

course has been offered annually since then. A second, advanced graduate seminar course was established in 1975, and a seminar on fault-tolerant software was started in 1983. About 500 graduate students have taken at least one of these courses, and over 800 practicing designers and other computer professionals have taken a "short course" version offered annually through UCLA Extension, and also presented in other U.S. cities, in London, in Paris, and in Tokyo.

Research activities in fault tolerance began at UCLA in late 1962, with the first Master's thesis "A Study of Redundant Switching Circuits" by K.B. de Graaf being completed in June, 1964. This thesis was followed by 14 more M.S. and 18 Ph.D. theses on various aspects of fault tolerance, supervised by A. Avižienis, who also authored or co-authored over 100 publications in this area. Several more M.S. and Ph.D. theses were supervised and papers published by other UCLA faculty, as discussed later.

Fault tolerance research at UCLA during the 1963-72 decade was characterized by a very effective collaboration with the STAR project at JPL. The excellent laboratory facilities and expert technicians at JPL enabled the design, construction, and evaluation of the experimental STAR computer, while the academic environment at UCLA provided the opportunity to the researchers to present their results and insights through the rigorous form of Ph.D. dissertations. The STAR computer research led to the UCLA Ph.D. theses by F. P. Mathur [Math 70b], G. C. Gilley [Gill 70], and D. A. Rennels [Renn 73a], all directed by A. Avižienis, and the University of Illinois Ph.D. thesis by J. A. Rohr [Rohr 73a]. The immediate supervision of this research was delegated to A. Avižienis by the thesis committee chairman, Prof. J. A. Robertson of the University of Illinois.

## 4.2 Two Early Formative Meetings

The first organizational manifestation of UCLA activities in the fault tolerance field was initiated by A. Avižienis in 1965. It was the Workshop on the Organization of Reliable Automata, held in Pacific Palisades, California on February 2-4, 1966 and co-sponsored by the UCLA Department of Engineering and the Technical Committee on Switching Circuit Theory and Logic Design of the IEEE Computer Group. The organizing committee consisted of Dr. Raymond E. Miller (IBM Research, Yorktown Heights, N.Y.), Dr. Robert A. Short (Stanford Research Institute, Menlo Park, CA), and was chaired by Professor Algirdas Avižienis, UCLA. The event attracted 43 participants, many of whom later formed the nucleus of the IEEE CG Technical Committee on Fault-Tolerant Computing that was founded in 1969. Presentations were given by 30 speakers. Texts of the talks were not published as a volume, but the workshop speakers provided three sessions (12 papers) at the First Annual IEEE Computer Conference held on September 6-8, 1967 in Chicago [IEEE 67]. Since a published reference to this 1966 Workshop does not exist, the program is reproduced as Appendix B to this paper.

The success of the Workshop and the continued support and interest of several participants led A. Avižienis to propose to the IEEE Computer Group (IEEE-CG) in early 1969 that a Technical Committee on Fault-Tolerant Computing (TC-FTC) should be formed to promote further activities in this field. The approval of the IEEE-CG Administrative Committee was

granted on November 18, 1969. A letter from Computer Group Chairman E. J. McCluskey, dated November 20, 1969, appointed A. Avižienis to serve as the first Chairman of the new TC-FTC and requested him to invite the founding members. The 18 initial members were: A. Avižienis, W. G. Bouricius, W. C. Carter, H. Y. Chang, J. Goldberg, A. L. Hopkins, E. C. Joseph, E. J. McCluskey, E. G. Manning, F. P. Mathur (TC Secretary), G. Metze, C. V. Ramamoorthy, J. P. Roth, R. A. Short, C. V. Srinivasan, S. A. Szygenda, C. Tung, and S. S. Yau. The new TC met for the first time on May 5, 1970 during the Spring Joint Computer Conference in Atlantic City, New Jersey.

The first objective of the new TC-FTC was the establishment of a technical conference, since an open conference dedicated to the theory and design of fault-tolerant computers had not been held since the 1962 Symposium on Redundancy Techniques for Computing Systems in Washington, D. C. [Wilc 62]. Co-sponsorship of the new meeting and strong organizational support was provided by JPL, and the initial International Symposium on Fault-Tolerant Computing took place on March 1-3, 1971 at the Huntington-Sheraton Hotel in Pasadena, California, with A. Avižienis serving as Symposium Chairman, and W. C. Carter as Program Chairman. A total of 251 participants registered for the meeting, representing the following countries: USA 230, Canada 9, France 4, Japan 3, England 3, Federal Republic of Germany and Italy, 1 each.

The program consisted of 33 papers (including three from France, one from England, and one from Japan) arranged in six sessions, and a panel discussion on diagnosis and testing [Gill 71]. The session titles were: test generation and diagnosis, fault location and testing, reliability modeling and analysis, architecture and design, error protection and recovery, and software reliability. At the conference banquet, the distinguished space scientist and Director of JPL, Dr. William C. Pickering, addressed the participants, outlining plans for future exploration of the planets and noting the key role of fault-tolerant computing in this endeavour. Many participants of the Symposium subsequently visited JPL for a tour and a demonstration of the STAR computer that included fault injection tests during program execution.

The annual series of comprehensive symposia on fault-tolerant computing took off with an auspicious start, and the TC-FTC began building an international membership of fault tolerance experts. The Call for Papers of the second annual Symposium, to be held in the Boston, Massachusetts area on June 19-21, 1972 was distributed at the Pasadena meeting.

# 4.3 The Second Phase at UCLA: Scope of Activities, 1972-1986

A major new research effort in fault-tolerant computing began at UCLA in July of 1972, when A. Avižienis became the Principal Investigator for a five-year, \$887,900 research grant "Fault-Tolerant Computing" from the U.S. National Science Foundation (NSF) and established the Reliable Computing and Fault Tolerance research group that has recently evolved into the Dependable Computing and Fault-Tolerant Systems (DC & FTS) Laboratory. Further research grants and contracts from NSF, the Office of Naval Research, the Federal Aviation Administration, NASA, the State of California, and industry have raised the total funding received for research support since 1972 to over \$3.5 million.

Faculty participation in research related to fault tolerance also grew steadily: beginning with two co-investigators (Professors W. W. Chu and D. F. Martin) on the initial NSF grant in 1972, ten more regular faculty members and several visiting professors and research scientists have taken part in research projects during the 1972-1986 period. Graduate student participation has also been very strong. It is estimated that about 200 publications, 30 Ph.D. dissertations, and 20 M.S. theses have resulted from the research on dependable computing and fault-tolerant systems that has been carried out by faculty and students associated with the projects of the Reliable Computing and Fault-Tolerance research group and its successor, the DC & FTS Laboratory, established in July, 1985.

A broad range of research problems have been addressed, including fault-tolerant architectures for distributed systems, supercomputers, and real-time applications, modeling and evaluation of fault-tolerant systems, fault tolerance in associative processors and database machines, fault-tolerant VLSI design, arithmetic error detecting and correcting codes, design of self-checking PLA's, fault-tolerant computer communications, software reliability, and design methodologies for fault-tolerant systems. Research on the tolerance of design faults by design diversity was initiated in 1975, and has resulted in a series of N-version programming experiments, as well as the implementation of the DEDIX distributed supervisory system for N-version software, and the development of a design paradigm for diverse multichannel systems.

# 4.4 Methodology Research and a Design Paradigm

The specification and design of the STAR computer at JPL involved much improvisation and experimentation with design alternatives. It became apparent that the lessons learned during this process could serve as the foundation for a more orderly approach that would utilize a set of guidelines for the choice of fault masking, error detection, diagnosis, and system recovery techniques.

The first effort to present such guidelines appeared in the 1967 Fall Joint Computer Conference paper "Design of Fault-Tolerant Computers" [Aviz 67]. This paper introduced the concept of a "fault-tolerant system", presented a classification of faults, and outlined the alternate forms of masking, detection, diagnosis, and recovery techniques along with some criteria for choices between "massive" (i.e., masking) and "selective" application of redundancy. The design of the JPL STAR computer was used to illustrate the application of these criteria in choosing the fault tolerance techniques for a spacecraft computer that had long life and autonomy requirements with strict weight and power constraints. The 47 references covered the most relevant published work to mid-1967.

The earlier book by W. H. Pierce "Failure-Tolerant Computer Design" [Pier 65] served as an important reference; however, it must be noted that Pierce's definition of "failure tolerance" corresponded exactly to fault masking in logic circuits, including voting, adaptive, and interwoven logic, redundant relay contact networks, and application of error correcting codes as a masking technique. It is a definitive work on masking forms of redundancy that were known at that time. However, neither error detection, nor fault diagnosis, nor recovery techniques were included as elements of Pierce's "failure-tolerant" computers.

The 1967 paper was the first of a sequence of publications intended to formulate an evolving view of dependable computing as the consequence of a judicious introduction of fault tolerance and fault avoidance during system design. Two different classes of faults - those due to physical causes, and those due to human mistakes and oversights are considered. This evolving view has been presented in a series of papers on the techniques, scope, and aims of fault tolerance. The key contributions to this series are: [Aviz 71c], [Aviz 72b], [Aviz 75a], [Aviz 75b], [Aviz 77c], [Aviz 78a], [Aviz 79], [Aviz 82a], [Aviz 82b], [Aviz 84b], [Aviz 86a].

The unifying theme of these papers has been the evolution of a design paradigm for fault-tolerant systems that guides the designer to consider fault tolerance as a fundamental issue throughout the design process. The series shows a progressive refinement of concepts and an expansion of the scope to include the tolerance of "human-made" design and interaction faults. Other recent themes are the balancing of performance and fault tolerance objectives during system partitioning and the integration of subsystem recovery procedures into a multi-level recovery hierarchy. Strong emphasis is also placed on the application of design diversity in all parts of a multichannel system in order to attain tolerance of design faults. Very valuable support for this research effort has come from the author's participation in the activities of IFIP Working Group 10.4, and quite especially from the discussions of fundamental concepts of fault tolerance that have been taking place since the very first meeting of the WG 10.4 in 1981. Most specifically, the work of Dr. J.-C. Laprie has been of great value, especially through collaboration during his stay as a Visiting Professor at UCLA in 1985 [Aviz 86a].

A closely related current effort is the development of a paradigm for the qualitative evaluation of the fault tolerance attributes of complex system designs. This "inverse" of the design paradigm is being developed as part of the research related to the Advanced Automation System for air traffic control in the U. S. [Aviz 87].

# 4.5 Fault-Tolerant System Design and Analysis

A major research effort in the design of fault-tolerant systems has been a natural consequence of the design methodology research described above. Results in several areas that have been addressed at UCLA since 1972 are summarized below.

Fault-Tolerant High Speed Systems. The emphasis in this area has been on the introduction of low-cost error detection, fault diagnosis, reconfiguration, and recovery techniques into large multiprocessor and "supercomputer" architectures. The results consist of three Ph.D. dissertations [Vine 71], [Thom 77], [Bond 81], as well as several publications [Vine 73], [Sylv 74], [Aviz 74a], [Sylv 75], [Thom 75], [Baqa 76a], [Baqa 76b], [Thom 76], [Aviz 77a], [Aviz 77b], [Aviz 78b], [Aviz 83a], [Ragh 84]. Faculty collaborators in this effort were Profs. M. D. Ercegovac and T. Lang. Under direction of Prof. W. W. Chu, performance and fault tolerance of multiport memories was studied in the Ph.D. thesis of P. Korff [Korf 76]. More recently, D. Rennels and A. Avižienis have initiated a study of the issues involved in implementing fault-tolerance in highly parallel multicomputers. Recommendations for implementing fault-tolerance in hypercube connected systems (e.g., the JPL Hypercube) have been presented [Renn 86b].

Associative Processors and Database Machines. Here the emphasis has been on introducing fault tolerance in a systematic manner and assessing the cost and the effectiveness. The associative processor work includes the Ph.D. thesis by B. Parhami [Parh 73c] and related papers that considered fault tolerance issues in this class of machines [Parh 73b], [Parh 74]. The later database machine work, done in collaboration with Prof. A. F. Cardenas, consisted of one Ph.D. thesis [Alav 81] and two papers [Card 83], [Aviz 84a].

Error Detection Methods. Majority of the research in error detection has dealt with continuing investigation of arithmetic error detecting codes. Previous arithmetic code work had introduced the concepts of "low-cost" arithmetic codes [Aviz 64], inverse residue codes, and multiple residue and AN codes with "low-cost" and "hybrid-cost" variations [Aviz 65], [Aviz 67b], [Aviz 69], [Aviz 71b]. Later results were: algorithms for coded operands [Aviz 73], applications to storage errors [Parh 73a], [Parh 78], coding and algorithms for signed-digit representations [Aviz 81a], and two-dimensional residue codes [Aviz 83a], [Aviz 85a], [Aviz 86b]. Other studies considered external monitoring [Aviz 81b] and diagnosis [Ng 77c]. Further work on arithmetic error codes was contributed by Prof. A. Svoboda [Svob 78], and a Ph. D. dissertation on error-coded algorithms for on-line arithmetic was done by A. Gorji-Sinaki [Gorj 81] under direction of Prof. M. Ercegovac.

Design of Distributed Systems. The "building block" approach to fault-tolerant distributed system design was pioneered by D. A. Rennels [Renn 78a], [Renn 78b], [Grey 84], [Renn 86a], [Renn 86b]. Much of the work in this area has focused on fault-tolerant real-time space systems. D. Rennels has supervised several research studies on the architectures required for the next generation of on-board computer systems [Renn 81a], [Renn 81c], [Depa 82], [Renn 84]. In the area of ground-based distributed systems a study was completed by C. Covey under the direction of D. Rennels which examined hardware augmentations to speed up functions for maintaining consistency and synchronization when data is replicated at several sites [Cove 82]. The Ph.D. thesis of B. Grey examined the potential use of highly fault-tolerant shared storage servers for large distributed systems. A preliminary architecture was completed, and highly secure capabilities-based storage management techniques were explored [Grey 85].

Under direction of A. Avižienis, Ph.D. dissertations were done on interconnection networks [CheH 81], on distributed architectures for N-version software execution [Maka 82a], [Maka 84], and on communication architectures [Ragh 82a], [Ragh 82b], [Ragh 85]. Professor D. S. Parker directed an investigation of distributed operating system and application algorithms, with emphasis on distributed concurrency control [Park 81]. The problem also was investigated in the Ph.D. thesis by R. A. Ramos [Ramo 82], [Park 82a]. A new type of network, called the Gamma network, which is a multi-processor interconnection network with redundant paths was introduced and analysed using redundant number systems [Park 82b], and regular networks were investigated [Malo 82]. Distributed communication systems were investigated under the direction of Prof. M. Gerla. A new fault-tolerant ring architecture was developed which consists of two interleaved rings [Grna 80a]. Computationally efficient techniques for reliability evaluation of a network in which both nodes and links can fail with given probabilities were devised [Grna 79], [Grna 81b]. An extended model of distributed systems, Stochastic Petri Nets, was developed and its properties in both discrete and continuous time as well as some

practical applications were studied in the Ph.D. dissertation of M. Molloy, which demonstrated the capabilities of the Stochastic Petri Net models to analyze systems for both correctness and performance [Moll 81]. Approximations and bounds on the performance of multibus interconnection schemes were derived [Mars 82]. Collaborating faculty included Profs. M. D. Ercegovac, M. Gerla, D. S. Parker, and B. Bussell.

Fault Tolerance Aspects of VLSI Design. This research included studies of selfchecking design [OryC 73], [Sum 75], [Sum 76] and the Ph.D. dissertation by S. L. Wang on totally self-checking PLAs [Wang 79], [Wang 81]. The Ph.D. thesis of M. W. Sievers explored computer-aided design of totally self-checking logic [Siev 80], [Siev 81]. Yield-improving designs were investigated in Ph.D. research by T. E. Mangir [Mang 81], [Mang 82]. An investigation into the feasibility of a circuit-oriented approach in enhancing testability of VLSI chips by dynamically controlled partitioning was performed as a Ph.D. thesis by V. G. Oklobdzija, directed by Prof. M. Ercegovac [Oklo 82a], [Oklo 82b]. In 1984, D. A. Rennels initiated studies to develop VLSI circuits which are both self-checking and provide concurrent self-testing during normal operation. This work is being conducted with S. Chau who is nearing completion of a Ph.D. dissertation [Renn 86a]. Dr. Yuval Tamir joined the UCLA faculty in 1985 after receiving his Ph.D. at UC Berkeley [Tami 85]. His Ph.D. thesis addressed a number of problems in the implementation of fault-tolerant VLSI circuits and their application in fault-tolerant multicomputer architecture [Tami 83, 84a, 84b, 84c]. Recently, he has addressed recovery issues in large multicomputer systems [Tami 87]. A study led by Y. Tamir and D. Rennels is also under way to reduce error checking delays in high speed VLSI processors by pipelining the error checks and providing several cycle rollback capability to compensate for delayed error signals.

Modeling and Evaluation of Fault-Tolerant Systems. Directed by A. Avižienis, early work in this area was done by F. P. Mathur [Math 70a], [Math 70b], including the CARE reliability modeling program [Aviz 71a]. Further work, including experimental evaluation of the JPL-STAR computer and the RMS modeling system, was done by D. A. Rennels [Aviz 72a], [Renn 73a], [Renn 73b]. A major advance in Markov modeling was contributed through the Ph.D. dissertation of Y. W. Ng [Ng 76a], who devised an unified model [Ng 73], [Ng 75], [Ng 80], that introduced transient faults [Ng 76b], degradability, and repair [Ng 77a]. The ARIES 76 reliability modeling system (written in APL) contained all these features [Ng 77b], [Ng 78], [Ng 80], and found wide acceptance for education, research, and in industry. The sucessors to ARIES 76 were the ARIES 81 [Maka 82b] and ARIES 82 [Maka 82c] systems that were written in the language C and introduced the model of a "periodically renewed" fault-tolerant system [Maka 81]. ARIES 82 is still widely used in research and industry. Under the direction of D. Rennels, several reliability models were developed by A. DePaula to deal with the use of multilevel redundancy and systems with time-varying failure rates. These were based on recursive integral formulations, with closed form solutions in some cases and numerical integrations in more complex cases to evaluate systems in which Markov matrices become unwieldy [Depa 82]. A separate effort addressed the modeling of transient faults in TMR systems [Merr 75].

# 4.6 Tolerance of Design Faults by Design Diversity and N-Version Software

By early 1970s significant progress had been made in the tolerance of physical faults, and it became clear that design faults, especially as represented by software "bugs", presented the next challenge to the researchers in fault tolerance. A research effort to attain tolerance of design faults by means of multi-version software was started by A. Avižienis at UCLA in early 1975. The method was first described as "redundant programming" at the April 1975 International Conference on Reliable Software in Los Angeles [Aviz 75a], and was renamed as "N-version programming" in the course of the next two years [Aviz 77d]. The entire UCLA design diversity research effort through mid-1985 has been summarized in [Aviz 85b]. The name "Multi-Version Software" (MVS) is also used.

The N-version programming approach to fault tolerant software systems employs functionally equivalent, yet independently developed software components. These components are executed concurrently under a supervisory system that uses a decision algorithm based on consensus to determine final output values. From its beginning in 1975, the fundamental conjecture of the MVS approach at UCLA has been that errors due to residual software faults are very likely to be masked by the correct results produced by the other versions in the system. This conjecture does not assume independence of errors, but rather a low probability of their concurrence and similarity. MVS systems achieve reliability improvements through the use of redundancy and diversity. A "dimension of diversity" is one of the independent variables in the development process of an MVS system. Diversity may be achieved along various dimensions, e.g., specification languages, specification writers, programming languages, programmers, algorithms, data structures, development environments, and testing methods.

The scarcity of previous results and an absence of formal theories on N-version programming in 1975 led to the choice of an experimental approach: to choose some conveniently accessible programming problems, to assess the applicability of N-version programming, and then to proceed to generate a set of programs. Once generated, the programs were executed as N-version software units in a simulated multiple-hardware system, and the resulting observations were applied to refine the methodology and to build up the concepts on N-version programming. The first detailed assessment of the research approach and a discussion of two sets of experimental results, using 27 and 16 independently written programs, obtained from Prof. D. Berry's software engineering class, was published in 1978 [CheL 78b]. The detailed results appear in the Ph.D. thesis by Liming Chen [CheL 78a].

The preceding exploratory research demonstrated the practicality of experimental investigation and confirmed the need for high quality software specifications. As a consequence, the first aim of the next phase of UCLA research (1979-82) was the investigation of the relative applicability of various software specification techniques. Other aims were to investigate the types and causes of software design faults, to propose improvements to software specification techniques and their use, and to propose future experiments for the investigation of design fault tolerance in software and in hardware.

To examine the effect of specification techniques on multi-version software, an experiment was designed in which three different specifications were used. The first was written in the formal specification language OBJ [Gogu 79b]. The second specification language chosen was the non-formal PDL that was characteristic of current industry practice. English was employed as the third, or "control" specification language, since English had been used in the previous studies [CheL 78b]. The detailed description of the experiment has been reported in the Ph.D. dissertation by J. P. J. Kelly [Kell 82], and the main results have been presented in [Aviz 82c], [Kell 83] and [Aviz 84b].

In parallel with the experiment, a general model for unified interpretation of N-Version Programming and Recovery Block methods was developed. The same model allows modeling of sequential and parallel N-Version Programming (NVP) as well as of the Recovery Block scheme. Following this model, queueing models have been developed to analyze the performance of the fault tolerance techniques. The average segment processing time (average throughput) and reliability were the performance measures. The same queueing models were used for examination of both performance measures as functions of system parameters which include: average segment processing time, recovery rate, repair rate and segment failure probability. The obtained results and a comparison of the two fault tolerance techniques were published in [Grna 80b], [Grna 80c].

The NASA Langley Research Center is sponsoring the NASA Four-University experiment in fault tolerant software which has been underway since 1984. During the summer of 1985, the NASA experiment employed 40 graduate students at four universities to design, code and document 20 diverse software versions of a program to manage redundancy and to compute accelerations for a redundant inertial measurement unit. The analysis of this software currently engages researchers at six sites: UCLA, the University of Illinois at Urbana-Champaign, North Carolina State University, and the University of Virginia, as well as the Research Triangle Institute (RTI), and Charles River Analytics (CRA). Empirical results from this experiment will be jointly published by the cooperating institutions after the verification, certification, and final analysis phases are complete. While the joint results still await publication, some independent results from the UCLA effort led by John P. J. Kelly have been reported in [Kell 86].

In the course of the experiments at UCLA it became evident that the usual general-purpose campus computing services were poorly suited to support the systematic execution, instrumentation, and observation of N-version fault-tolerant software. In order to provide a long-term research facility for experimental investigations of design diversity as a means of achieving fault-tolerant systems, the UCLA Reliable Computing and Fault Tolerance research group designed and implemented the prototype DEDIX (DEsign DIversity eXperiment) system [Aviz 85c], a distributed supervisor and testbed for multiple-version software, at the UCLA Center for Experimental Computer Science. DEDIX is supported by the Center's Olympus Net local network, which utilizes the UNIX-based LOCUS distributed operating system to operate a set of VAX 11/750 computers. The purpose of DEDIX is to supervise and to observe the execution of N diverse versions of an application program functioning as as fault-tolerant N-version software unit. DEDIX also provides a transparent interface to the users, versions, and the input/output system, so that they need not be aware of the existence of multiple versions and recovery algo-

rithms. The prototype DEDIX system has been operational since early 1985. Several modifications have been introduced since then, most of them intended to improve the speed of the execution of N-version software. The first major test of DEDIX that is currently taking place is the experimentation with the set of 20 programs produced by the NASA-sponsored four-university project discussed earlier. At the same time, a formal specification effort for the DEDIX is being initiated.

The past experience at UCLA has pinpointed an effective specification as the keystone of success for N-version software implementation [Aviz 84b]. Significant progress has occurred in the development of formal specification languages since our previous experiments. Our current goal is to compare and assess the ease of use by application programmers of several formal program specification methods. Presently the first choice is the Larch specification language family [Gutt 85]. The NASA Four-University experiment software that was originally specified in English has been specified in Larch [Tai 86], and work has been initiated on specifying parts of DEDIX in Larch as well. Valuable advice and support in the efforts have been received from the originators of Larch, Prof. J. V. Guttag of M.I.T., Dr. J. J. Horning of the DEC Systems Research Center, and Prof. J. M. Wing of Carnegie-Mellon University.

In an MVS system, several versions of a program are executed, usually in parallel, and their intermediate results are compared. In this way, faults in the individual versions are masked by a consensus. Without recovery the accumulation of failures is eventually large enough to saturate the fault-masking ability, and the entire system fails. It is therefore essential to recover these versions as they fail, and to transform the erroneous state of the failed versions to an error-free state from which normal execution can continue. The method of Community Error Recovery (CER) developed at UCLA in the Ph.D. dissertation of K. S. Tso [Tso 87a] makes use of the assumption that at any given time during execution a majority of good versions exists which can supply information to recover the failed versions. Experimental evaluation of the CER method has been performed, using the DEDIX supervisory system and the five diverse programs written at UCLA for the NASA experiment described previously [Kell 86]. A summary of the implementation and modeling of the CER method has been presented in [Tso 86], and a discussion of the evaluation appears in [Tso 87b].

Related research on the NASA experiment programs (in two completed M.S. theses) has considered statistical data on coincident and similar errors [Dora 86], and the branch coverage test has been applied to study various aspects of the programs [Swai 86]. In late 1986 a new experiment was initiated with support from the Sperry Commercial Flight Systems Division of Honeywell, Inc., Phoenix, AZ., in which six teams of two programmers each will use six different programming languages (Pascal, C, Modula-2, Ada, Lisp, and Prolog) to write a flight control program. The goal is to study the diversity that can be attained by the use of very different languages.

# 4.7 Reliable Software, Formal Specification, and Program Correctness

With the start of the 1972-78 NSF grant, Professor David F. Martin took charge of a study on various aspects of attaining reliable software. This research focused on semantic and pragmatic issues of the correct implementation of programming languages. The investigations carried out comprised a balanced combination of foundational theoretical studies and practical implementations. During the 1972-78 period, Ph.D. dissertations were completed and contributions were made in the areas of acyclic parallel program schemata [Hadj 75], compiler correctness [Chir 76], portable translator writing systems [Heis 76], high-level microprogramming languages and the synthesis of correct microprograms [Patt 77], and the design and proof of correct implementation of an expression-oriented, microcomputer-based high-level programming language [Clea 78].

Beginning in 1973, Professor Joseph A. Goguen conducted algebraic research on program semantics, specification and synthesis [Gogu 79a]. Results included the development of the basic mathematical definitions and results which underlie the algebraic approach to abstract data types [Gogu 78a], a method to introduce abstract error messages into abstract data types and programs [Gogu 77], and the new programming specification language OBJ [Gogu 78b]. An interactive implementation called OBJ-T was done on UCLA's PDP-10 [Gogu 79b]. Professor R. Burstall from the University of Edinburgh and J. Goguen developed an algebraic specification language named CLEAR [Burs 77].

In 1979, a three-year NSF grant "Improvement of the Reliability of Computing," was received that supported the N-Version fault-tolerant software research as well as the continuation of above discussed research concerned with the development of techniques for formal algebraic specification of semantics, and studies of techniques and tools to assure the correct implementation of programming languages. Two Ph.D. dissertations were completed under the guidance of Prof. D. F. Martin. The thesis research conducted by M. Zamfir, developed a mathematical model of concurrent computing agents, the *flow net*. Parallel programming languages can also be defined in this model in the usual syntax-directed fashion [Zamf 82]. The principal accomplishment toward correct implementation of programming languages was the Ph.D. dissertation by R. Bigonha which produced the design of a language and system for the modular specification of the denotational semantics of programming languages [Bigo 82].

Directed by Prof. J. Goguen, Ph.D. thesis research by K. Parsaye-Ghomi produced a theory of higher order data types, i.e., abstract data types with higher order operations and equations [Pars 82].

# 5. Acknowledgments

The evolution of fault-tolerant computing at JPL and at UCLA began late in 1960. During the past twentysix years, numerous individuals have made significant contributions to these efforts. Many of them are recognized by citations of publications; we also wish to thank those contributors whose names appear in the acknowledgments of the referenced papers, and also to those colleagues whose valuable contributions have remained less evident.

An especially important and pleasant aspect of our research has been the opportunity to welcome at UCLA and to work with visiting colleagues from abroad. We sincerely thank them all and look forward to many return visits: T. Anderson (U.K.), J. Arlat, J.-P. Blanquart, M. Buchwalter, J. P. Chinal, A. Costes, J.-C. Laprie, P. Traverse (France), W. Giloi, W. Goerke, U. Voges (Fed. Rep. Germany), H. Kopetz (Austria), M. Ajmone Marsan, L. Strigini (Italy), P. Gunningberg (Sweden), Y. Hatakeyama, H. Ihara, H. Mori, T. Sasada (Japan), R. Huslende (Norway), A. Grnarov (Yugoslavia), R. Jasinevičius, J. Mockus, V. Statulevičius (Lithuania), C.-L. Chen (P. R. China).

It has been a special pleasure to put together this overview of past efforts as part of the IFIP WG 10.4 Baden Symposium honoring our dear friend and colleague, Dr. William C. Carter. Ever since our first meeting in 1965, Bill has been a constant source of advice, support, and inspiration. Thank you, Bill, for your personal standard of integrity and excellence that set an admirable example for us to follow.

#### 6. References

Note: The single asterisks at the references, e.g. [Alav 81]\*, designate Ph.D. dissertations, and the double asterisks (\*\*) designate M.S. theses completed at UCLA.

- [A&A 70] "TOPS Outer Planet Spacecraft," Astronautics and Aeronautics (Special Issue), Vol. 8, No. 9, September 1970.

- [Alav 81]\* Alavian, F., "Database Recovery and Fault-Tolerance Analyses in Parallel Associative Database Processors," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, December 1981; also *Technical Report No. CSD-820318*, March 1982.

- [Aren 83] Arens, W., Rennels, D. A., "A Fault-Tolerant Computer for Autonomous Spacecraft,"

Digest of FTCS-13, the 13th International Symposium on Fault-Tolerant Computing,

Milano, Italy, June 1983, pp. 467-470.

- [Aviz 64] Avižienis, A., "A Set of Algorithms for a Diagnosable Arithmetic Unit," Jet Propulsion Laboratory, Pasadena, California, *Technical Report 32-546*, March 1, 1964.

- [Aviz 65] Avižienis, A., "A Study of the Effectiveness of Fault-Detecting Codes for Binary Arithmetic," Jet Propulsion Laboratory, Pasadena, California, *Technical Report 32-711*, September 1, 1965.

- [Aviz 66] Avižienis, A., "System Organization of the JPL Self-Testing and Repairing Computer and Its Extension to a Multiprocessor Configuration," Proceedings of the NASA Seminar on Spaceborne Multiprocessing, October 1966, Boston, pp. 61-66.

- [Aviz 67a] Avižienis, A., "Design of Fault-Tolerant Computers," AFIPS Conference Proceedings, 1967 Fall Joint Computer Conference, Vol. 31, Washington, D. C.: Thompson, 1967, pp. 733-743.

- [Aviz 67b] Avižienis, A., "Concurrent Diagnosis of Arithmetic Processors," Digest of the 1st Annual IEEE Computer Conference, Chicago, IL, September 1967, pp. 34-37.

- [Aviz 68] Avižienis, A., "An Experimental Self-Repairing Computer," in *Information Processing* '68, Proceedings of the IFIP Congress 1968, Vol. 2, pp. 872-877.

- [Aviz 69] Avižienis, A., "Digital Fault Diagnosis by Low-Cost Arithmetical Coding Techniques," Proceedings of the Purdue University Centennial Year Symposium on Information Processing, April 1969, pp. 81-92.

- [Aviz 71a] Avižienis, A., Gilley, G. C., Mathur, F. P., Rennels, D. A., Rohr, J. A, Rubin, D. K., "The STAR (Self-Testing-and-Repairing) Computer: An Investigation of the Theory and Practice of Fault-Tolerant Computer Design," *IEEE Trans. on Computers*, Vol. C-20, No. 11, November 1971, pp. 1312-1321; also in *Digest of the 1971 International Symposium on Fault-Tolerant Computing*, Pasadena, CA, March 1971, pp. 92-96.

- [Aviz 71b] Avižienis, A., "Arithmetic Error Codes: Cost and Effectiveness Studies for Application in Digital System Design," *IEEE Trans. on Computers*, Vol. C-20, No. 11, November 1971, pp. 1322-1330; also in *Digest of the 1971 International Symposium on Fault-Tolerant Computing*, Pasadena, CA, March 1971, pp. 118-121.

- [Aviz 71c] Avižienis, A., "Fault-Tolerant Computing, An Overview," *IEEE Computer*, Vol. 4, No. 1, February 1971, pp. 5-8.

- [Aviz 72a] Avižienis, A., Rennels, D. A., "Fault-Tolerance Experiments With The JPL STAR Computer", in *Digest of COMPCON '72 (Sixth Annual IEEE Computer Society Int. Conf.)*, San Francisco, California, 1972, pp. 321-324.

- [Aviz 72b] Avižienis, A., "The Methodology of Fault-Tolerant Computing," *Proceedings of the 1st USA-Japan Computer Conference*, Tokyo, October 1972, pp. 405-413.

- [Aviz 73] Avižienis, A., "Arithmetic Algorithms for Error-Coded Operands", IEEE Trans. on Computers, Vol. C-22, No. 6, June 1973, pp. 567-572; also in Digest of FTCS-2, the 2nd International Symposium on Fault-Tolerant Computing, Newton, MA, June 1972, pp. 25-29.

- [Aviz 74a] Avižienis, A., Parhami, B., "A Fault-Tolerant Parallel Computer System for Signal Processing," Digest of FTCS-4, the 4th International Symposium on Fault-Tolerant Computing, Champaign, IL., June 1974, pp. 2-8 2-13.

- [Aviz 75a] Avižienis, A., "Fault-Tolerance and Fault-Intolerance: Complementary Approaches to Reliable Computing," *Proceedings of the 1975 International Conference on Reliable Software*, Los Angeles, April 1975, pp. 458-464.

- [Aviz 75b] Avižienis, A., "Architecture of Fault-Tolerant Computing Systems," Digest of FTCS-5, the 5th International Symposium on Fault-Tolerant Computing, Paris, June 1975, pp. 3-16.

- [Aviz 76] Avižienis, A., "Fault-Tolerant Systems," *IEEE Trans. on Computers*, Vol. C-25, No. 12, December 1976, pp. 1304-1312.

- [Aviz 77a] Avižienis, A., "Fault-Tolerance and Longevity: Goals for High-Speed Computers on the Future," *Proceedings of the Symposium on High-Speed Computer & Algorithm Organization*, University of Illinois at Urbana-Champaign, April 1977, Academic Press, pp. 173-178.

- [Aviz 77b] Avižienis, A., Ercegovac, M., Lang, T., Sylvain, P., Thomasian, A., "An Investigation of Fault-Tolerant Architectures for Large-Scale Numerical Computing," *Proceedings of the Symposium on High-Speed Computer & Algorithm Organization*, University of Illinois at Urbana-Champaign, April 1977, Academic Press, pp. 173-178.

- [Aviz 77c] Avižienis, A., "Fault-Tolerant Computing: Progress, Problems, and Prospects," Information Processing 77, Proceedings of the IFIP Congress 1977, Toronto, August 1977, pp. 405-420.

- [Aviz 77d] Avižienis, A., Chen, L., "On the Implementation of N-version Programming for Software Fault Tolerance During Execution," *Proceedings COMPSAC 77*, (First IEEE-CS International Computer Software and Applications Conference), Chicago, November 1977, pp. 149-155.

- [Aviz 78a] Avižienis, A., "Fault-Tolerance: The Survival Attribute of Digital Systems," *Proceedings of the IEEE*, October 1978, 66-10, pp. 1109-1125.

- [Aviz 78b] Avižienis, A., Bond, J. W. III, "Fault Tolerance in Large Computing Systems," Proceedings of the 3rd Jerusalem Conference on Information Technology, Jerusalem, August 1978, pp. 9-16.

- [Aviz 79] Avižienis, A., "Toward a Discipline of Reliable Computing," *Proceedings of the EU-ROIFIP 79*, (European Conference on Applied Information Technology), London, September 1979, pp. 701-706.

- [Aviz 81a] Avižienis, A., "Low Cost Residue and Inverse Residue Error-Detecting Codes for Signed-Digit Arithmetic," *Proceedings of the 5th IEEE Symposium on Computer Arithmetic*, Ann Arbor, MI, May 1981, pp. 165-168.

- [Aviz 81b] Avižienis, A., "Fault Tolerance by Means of External Monitoring of Computer Systems," AFIPS Conference Proceedings, Vol. 50, May 1981, pp. 27-40.

- [Aviz 82a] Avižienis, A., "The Four-Universe Information System Model for Fault-Tolerance," Digest of FTCS-12, the 12th International Symposium on Fault-Tolerant Computing, Santa Monica, California, June 1982, pp. 6-13.

- [Aviz 82b] Avižienis, A., "Design Diversity the Challenge of the Eighties," Digest of FTCS-12, the 12th International Symposium on Fault-Tolerant Computing, Santa Monica, California, June 1982, pp. 44-45.

- [Aviz 82c] Avižienis, A., Kelly, J. P. J. "Fault-Tolerant Multi-Version Software: Experimental Studies of a Design Diversity Approach," *Proceedings of 6th International Conference on Software Engineering (Poster Sessions)*, Tokyo, Japan, September 1982, pp. 101-102.

- [Aviz 83a] Avižienis, A., Raghavendra, C. S., "Applications for Arithmetic Error Codes in Large, High-Performance Computers," *Proceedings of the 6th IEEE Symposium on Computer Arithmetic*, Aarhus, Denmark, June 1983, pp. 169-173.

- [Aviz 84a] Avižienis, A., Cardenas, A. F., Alavian, F., "On the Effectiveness of Fault Tolerance Techniques in Parallel Associative Database Processors," *Proceedings of the IEEE 1984 International Conference on Data Engineering*, April 1984, pp. 50-59.

- [Aviz 84b] Avižienis, A., Kelly, J. P. J., "Fault Tolerance by Design Diversity: Concepts and Experiments," *Computer*, Vol. 17, No. 8, August 1984, pp. 67-80.

- [Aviz 85a] Avižienis, A., "Arithmetic Algorithms for Operands Encoded in Two-Dimensional Low-Cost Arithmetic Error Codes," *Proceedings of the 7th IEEE Symposium on Computer Arithmetic*, Urbana, Illinois, May 1985, pp. 285-292.

- [Aviz 85b] Avižienis, A., "The N-Version Approach to Fault-Tolerant Software", *IEEE Transactions on Software Engineering*, Vol. SE-11, No. 12, December 1985, pp. 1491-1501.

- [Aviz 85c] Avižienis, A., Gunningberg, P., Kelly, J. P. J., Strigini, L., Traverse, P. J., Tso, K. S., Voges, U., "The UCLA DEDIX system: a Distributed Testbed for Multiple-Version Software," Digest of FTCS-15, the 15th International Symposium on Fault-Tolerant Computing, Ann Arbor, Michigan, June 1985, pp. 126-134.

- [Aviz 86a] Avižienis, A. Laprie, J. C., "Dependable Computing: From Concepts to Design Diversity," *Proceedings of the IEEE*, Vol. 74, No. 5, May 1986, pp. 629-638.

- [Aviz 86b] Avižienis, A., "Two-Dimensional Low-Cost Arithmetic Residue Codes: Effectiveness and Arithmetic Algorithms," Digest of FTCS-16, the 16th International Symposium on Fault-Tolerant Computing, Vienna, Austria, July 1986, pp. 330-336.

- [Aviz 87] Avižienis, A., Ball, D. E., "On the Achievement of a Highly Dependable and Fault-Tolerant Air Traffic Control System," *Computer*, Vol. 20, No. 2, February 1987, pp. 84-90.

- [Baqa 76a]\*\* Baqai, R. M., "The Reliability Aspects and Interconnection Network Strategies for IL-LIAC IV type Like Array Processors," M.S. thesis, UCLA Computer Science Department, University of California, Los Angeles, March 1976.

- [Baqa 76b] Baqai, I., Lang, T., "Reliability Aspects of the ILLIAC IV Computer," Proceedings of the 1976 International Conference on Parallel Processing, August 1976, pp. 123-131.

- [Bigo 82]\* Bigonha, R. S., "A Denotational Semantics Implementation System," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, March 1982; also *Technical Report No. CSD-820317*, March 1982.

- [Bond 81]\* Bond, J. W., III, "A Comparison of Fault-Tolerance in Large Scale Scientific Computer Systems," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, September 1981; also *Technical Report No. CSD-810601*, June 1981.

- [Burc 76] D. D. Burchby et al., "Specification of the Fault-Tolerant Space-Borne Computer (FTSC)," Digest of FTCS-6, the 6th International Symposium on Fault-Tolerant Computing, Pittsburgh, PA, June 1976, pp. 129-133.

- [Burs 77] Burstall, R. M., Goguen, J. A., "Putting Theories Together to Make Specifications," Proceedings of the 5th International Joint Conference on Artificial Intelligence, (MIT, Cambridge, Mass.) 1977, pp. 1045-1058.

- [Card 83] Cardenas, A. F., Alavian, F., Avižienis, A., "Performance of Recovery Architectures in Parallel Associative Database Processors," ACM Transactions on Database Systems, Vol. 8, No. 3, September 1983, pp. 291-323.

- [CheH 81]\* Chen, H. P. D., "The Analysis and Synthesis of Interconnection Networks for Distributed Computer Systems," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, June 1981; also *Technical Report No. CSD-820203*, February 1982.

- [CheL 78a]\* Chen, L., "Improving Software Reliability by N-version Programming," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, June 1978; also *Technical Report No. UCLA-ENG-7843*, June 1978.

- [CheL 78b] Chen, L., Avižienis, A., "N-version Programming: A Fault Tolerance Approach to Reliability of Software Operation," Digest of FTCS-8, the 8th International Symposium on Fault-Tolerant Computing, Toulouse, France, June 1978, pp. 3-9.

- [Chir 76]\* Chirica, L. M., "Contributions to Compiler Correctness," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, September 1976; also *Technical Report No. UCLA-ENG-7697*, October 1976.

- [Clea 78] Cleaveland, J. C., "Design, Implementation and Correctness of an Expression-Oriented Language for Microcomputers," UCLA Computer Science Department, *Technical Report No. UCLA-ENG-7837*, July 1978.

- [Conn 72] Conn, R. B., Alexandridis, N. A., Avižienis, A., "Design of a Fault-Tolerant Modular Computer with Dynamic Redundancy," *AFIPS Conference Proceedings*, Vol. 41, Fall JCC 1972, pp. 1057-1067.

- [Cove 82] Covey, C., Rennels, D. A., "Hardware Support Mechanisms for Concurrency Control in Local Computer Networks," Digest of International Workshop on High Level Language Architecture, Fort Lauderdale, Florida, December 1982.

- [Depa 82]\* DePaula, A., "Evaluation and Reliability Estimation of Distributed Architectures for On-Board Computers," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, September 1982; also *Technical Report No. CSD-821205*, December 1982.

- [Dora 86]\*\* Dorato, K., "Coincident Errors in N-Version Programming," M.S. thesis, UCLA Computer Science Department, University of California, Los Angeles, June 1986.

- [Gill 70]\* Gilley, G. C., "Automatic Maintenance of Spacecraft Systems for Long-Life, Deep-Space Missions", *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, September 1970.

- [Gill 71] Gilley, G. C., Editor, Digest of the 1971 International Symposium on Fault-Tolerant Computing, Pasadena, California, March 1971.

- [Gill 72] Gilley, G. C., "A Fault-Tolerant Spacecraft", in Digest of FTCS-2, the 2nd International Symposium on Fault-Tolerant Computing, Newton, MA, June 1972, pp. 105-109.

- [Gogu 77] Goguen, J. A., "Abstract Errors for Abstract Data Types," Proceedings IFIP Working Conference on Formal Description of Programming Concepts, (ed. J. Dennis), MIT, 1977, pp. 21.1-21.32; also in Formal Description of Programming Concepts, (ed. E. Neuhold), North Holland, 1978.

- [Gogu 78a] Goguen, J. A., Thatcher, J. W., Wagner, E. G., "An Initial Algebra Approach to the Specification, Correctness, and Implementation of Abstract Data Types," *Current Trends in Programming Methodology*, Vol. 4, *Data Structuring* (ed. R. Yeh), Prentice Hall, 1978, pp. 80-149.

- [Gogu 78b] Goguen, J., "Some Design Principles and Theory for OBJ-0, A Language for Expressing and Executing Algebraic Specifications of Programs," *Proceedings, International Conference on Mathematical Studies of Information Processing*, Kyoto, Japan, 1978, pp. 429-475.

- [Gogu 79a] Goguen, J. A., "Algebraic Specification," Research Directions in Software Technology (ed. P. Wegner), MIT Press, 1979, pp. 370-376.

- [Gogu 79b] Goguen, J. A., Tardo, J. J., "An Introduction to OBJ: A Language for Writing and Testing Formal Algebraic Program Specifications," *Proceedings of the Conference on the Specification of Reliable Software*, Cambridge, MA, April 1979, pp. 170-189.

- [Gorj 81]\* Gorji-Sinaki, A., "Error-coded Algorithms for On-line Arithmetic," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, February 1981; also *Technical Report No. CSD-810303*, March 1981.

- [Grey 84] Grey, B. O., Avižienis, A., Rennels, D. A., "A Fault-Tolerant Architecture for Network Storage Systems," Digest of FTCS-14, the 14th International Symposium on Fault-Tolerant Computing, Kissimmee, Florida, June 1984, pp. 232-239.

- [Grey 85]\* Grey, B. O., "FTSS: A Fault-Tolerant Storage System Supporting High Availability and Security in a Distributed Processing Environment," *Ph.D. dissertation*, UCLA Computer Science Department, University of California, Los Angeles, March 1985.

- [Grna 79] Grnarov, A., Kleinrock, L., Gerla, M., "A New Algorithm for Network Reliability Computation," *Proceedings Computer Networking Symposium*, Gaithersburg, Maryland, December 1979.

- [Grna 80a] Grnarov, A., Kleinrock, L., Gerla, M., "A Highly Reliable Distributed Loop Architecture," Digest of FTCS-10, the 10th International Symposium on Fault-Tolerant Computing, Kyoto, Japan, October 1980, pp. 319-324.

- [Grna 80b] Gmarov, A., Arlat, J., Avižienis, A., "Modeling of Software Fault-Tolerance Strategies," *Proceedings of the 11th Annual Pittsburgh Modeling & Simulation Conference*, University of Pittsburgh, Pennsylvania, Vol. 11, Part 2, May 1980, pp. 571-578.

- [Grna 80c] Grnarov, A., Arlat, J., Avižienis, A., "On the Performance of Software Fault-Tolerance Strategies," Digest of FTCS-10, the 10th International Symposium on Fault-Tolerant Computing, Kyoto, Japan, October 1980, pp. 251-253.

- [Gma 81b] Gmarov, A., Gerla, M., "Multiterminal Analysis of Distributed Processing Systems," Proceedings of the International Conference on Parallel Processing, August 1981.