TASK RESPONSE TIME AND MODULE ASSIGNMENT FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS

Kin Kwong Leung

December 1985 CSD-850041

| • . |  |   |  |  |

|-----|--|---|--|--|

|     |  | • |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

|     |  |   |  |  |

# UNIVERSITY OF CALIFORNIA

# Los Angeles

Task Response Time and Module Assignment for Real-Time Distributed Processing Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Kin Kwong Leung

The dissertation of Kin Kwong Leung is approved.

James MacQueen

Harold Borko

D. Stott Parker

Milos D. Ercegovac

Wesley W. Chu, Committee Chair

University of California, Los Angeles

1985

To

Miranda (Mei-Ling) and our Moms and Dads

# TABLE OF CONTENTS

|                                                                                  | page   |

|----------------------------------------------------------------------------------|--------|

|                                                                                  |        |

| LIST OF NOTATION                                                                 | ix     |

| 1 INTRODUCTION                                                                   | 1      |

| 1 INTRODUCTION                                                                   | ī      |

| 1.2 SOME RELATED DESIGN ISSUES OF RTDPS                                          |        |

| 1.2.1 Task Partitioning                                                          | 5<br>5 |

| 1.2.2 Module Assignment                                                          | 7      |

| 1.2.3 Module Replication                                                         | 9      |

| 1.2.4 File Allocation                                                            | 11     |

| 1.3 CONTRIBUTIONS OF THIS RESEARCH                                               | 13     |

| 2 TASK RESPONSE TIME MODEL FOR RTDPS                                             | 16     |

| 2.1 INTRODUCTION                                                                 | 16     |

| 2.1 INTRODUCTION                                                                 | 20     |

| 2.2.1 Module Response Time Model                                                 | 21     |

| 2.2.2 Weighted Control-Flow Graph Model                                          | 25     |

| 2.2.2.1 Sequential Thread Subgraph                                               | 27     |

| 2.2.2.2 And-Fork to And-Join Subgraph                                            | 27     |

| 2.2.2.3 Or-Fork to Or-Join Subgraph                                              | 29     |

| 2.2.2.4 Loop Subgraph                                                            | 29     |

| 2.2.3 Module Response Times With Dependent Module Invocations                    | 31     |

| 2.2.3.1 Partitioning the Control-Flow Subgraphs                                  | 31     |

| 2.2.3.2 Mean Module Response Times for Partitioned                               | -      |

| Subgraphs                                                                        | 32     |

| 2.3 MODEL VALIDATION                                                             | 36     |

| 2.4 MODEL APPLICATIONS                                                           | 46     |

| 2.5 SUMMARY                                                                      | 51     |

| 3 PRECEDENCE RELATIONSHIP EFFECTS ON RESPONSE TIMES                              | 53     |

| 3.1 INTRODUCTION                                                                 | 53     |

| 3.1 INTRODUCTION                                                                 | 54     |

| 3.2.1 The Waiting Time Ratio: W2/W1                                              | 60     |

| 3.2.2 The Waiting Time Ratio: W3/W1                                              | 62     |

| 3.2.3 Cutting Points for the PR Effect                                           | 64     |

| 3.3 INTUITIVE REASONING FOR THE PR EFFECT                                        | 68     |

| 3.3 PR EFFECT FOR SEVERAL CONSECUTIVE MODULES                                    | 73     |

| 3.4 HEURISTIC RULES TO CONSIDER PR IN MODULE                                     |        |

| ASSIGNMENT                                                                       | 74     |

| 3.5 SUMMARY                                                                      | 76     |

| 4 MODULE ASSIGNMENT WITHOUT MODULE REPLICATIONS                                  | 78     |

| 4.1 INTRODUCTION                                                                 | 78     |

| 4.2 ASSUMPTIONS AND PROBLEM FORMULATION                                          | 79     |

| 4.3 PROBLEM COMPLEXITY OF MAP                                                    | 82     |

| 4.4 A NEW APPROACH TO MODULE ASSIGNMENT PROBLEM                                  | 86     |

| 4.4.1 Algorithm for MAP  4.4.2 The Required Number of Random Initial Assignments | 87     |

| 4.4.2 The Required Number of Random Initial Assignments                          | 90     |

|             | 4.4.3 Weighted Task Response Time                     | 94    |

|-------------|-------------------------------------------------------|-------|

|             | 4.4.4 Application of the Algorithm to DPAD System     | 95    |

| 4.5         | SUMMARY                                               | 107   |

| 5 MODU      | JLE ASSIGNMENT WITH MODULE REPLICATIONS               | 108   |

| 5.1         | INTRODUCTION                                          | 108   |

| 5.2         | INTRODUCTIONTHE OBJECTIVE FUNCTION FOR RMAP           | 110   |

| • • •       | 5.2.1 A New Objective Function                        | 111   |

|             | 5.2.2 Properties of the Penalty Delay Function        | 112   |

| 5.3         | A NEW SEARCH ALGORITHM FOR RMAP                       | 115   |

| ر.ر         | 5.3.1 Problem Formulation                             | 116   |

|             | 5.2.2 Atamiahan fan DMAD                              | 116   |

|             | 5.3.2 Algorithm for RMAP                              | 120   |

|             | 5.3.3 Initial Module Multiplicities                   | 120   |

| 5.4         | APPLICATION OF RMAP ALGORITHM TO THE SENTRY           |       |

|             | SYSTEM 5.4.1 The Characteristics of the Sentry System | 122   |

|             | 5.4.1 The Characteristics of the Sentry System        | 122   |

|             | 5.4.2 Performance of the RMAP Algorithm               | 126   |

| 5.5         | SUMMARY                                               | 139   |

|             |                                                       |       |

| 6 CONC      | LUSIONS & FUTURE RESEARCH WORK                        | 141   |

| 6.1         | CONCLUSIONS                                           | 141   |

| 6.2         | FUTURE RESEARCH WORK                                  | 143   |

| 0.2         | 6.2.1 Database Management Strategies                  | 143   |

|             | 6.2.2 Module and File Allocations                     | 144   |

|             | 6.2.3 Tightly Coupled Distributed Systems             | 144   |

|             | 0.2.3 Figury Coupled Distributed Systems              | 7-4-4 |

| REFERI      | ENCES                                                 | 146   |

|             |                                                       |       |

| Appendi     | x A RESPONSE TIME FOR AND-FORK TO AND-JOIN            |       |

| STIRGE      | APH                                                   | 150   |

| A.1         | RESPONSE TIME FOR A TWO-THREAD AND-TO-AND             |       |

|             | CLID CD + DU                                          | 151   |

| Δ 2         | RESPONSE TIME FOR A N-THREAD AND-TO-AND               |       |

| A.4         | SUBGRAPH                                              | 154   |

|             | 30BQIA11                                              | 15    |

| Adi         | X B MEAN MODULE RESPONSE TIMES WITH DEPENDENT         |       |

| White im    | ATIONS                                                | 157   |

| TA A CAC'   | MEAN WAITING TIME FOR ENTRY MODULES                   | 158   |

| B.1         | MEAN WAITING TIME FOR ENTRY MODULES                   | 159   |

| <b>B</b> .2 | MEAN WAITING TIME FOR NON-ENTRI MODULES               | 133   |

|             | CALORIE E RECRONCE ER CEC CON PRIORIES MORIE E        |       |

|             | X C MODULE RESPONSE TIMES FOR PRIORITY MODULE         | 163   |

| SCHED       | ULING                                                 | 103   |

|             |                                                       |       |

# LIST OF FIGURES

|                                                                                                                       | page |

|-----------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1a: A Sample Task Control-Flow Graph                                                                         | 17   |

| •                                                                                                                     |      |

| Figure 2.1b: Assignments of Modules to Computers                                                                      | 18   |

| Figure 2.2: Weighted Control-Flow Graph for Response Time Estimations                                                 | 26   |

| Figure 2.3: Sequential Thread                                                                                         | 28   |

| Figure 2.4: And-Fork to And-Join Subgraph                                                                             | 28   |

| Figure 2.5: Or-Fork to Or-Join Subgraph                                                                               | 30   |

| Figure 2.6: Loop Subgraph                                                                                             | 30   |

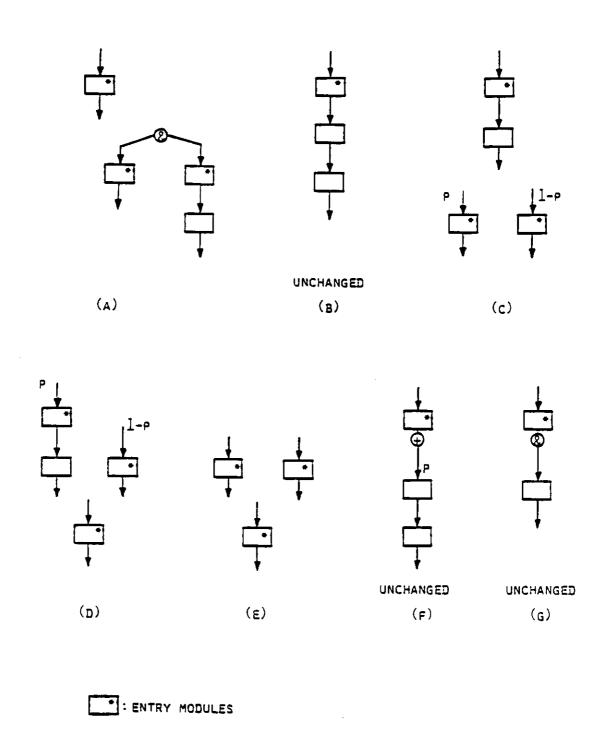

| Figure 2.7: Examples of Control-Flow Subgraphs that Allocated on a Computer                                           | 33   |

| Figure 2.8: Partitioned Control-Flow Subgraphs of Figure 2.7                                                          | 34   |

| Table 2.1: Module Execution Times for the Sample Control-Flow Graph (Figure 2.1a)                                     | 38   |

| Table 2.2: Module Assignments & Computer Processing Load for the Sample Control-Flow Graph                            | 39   |

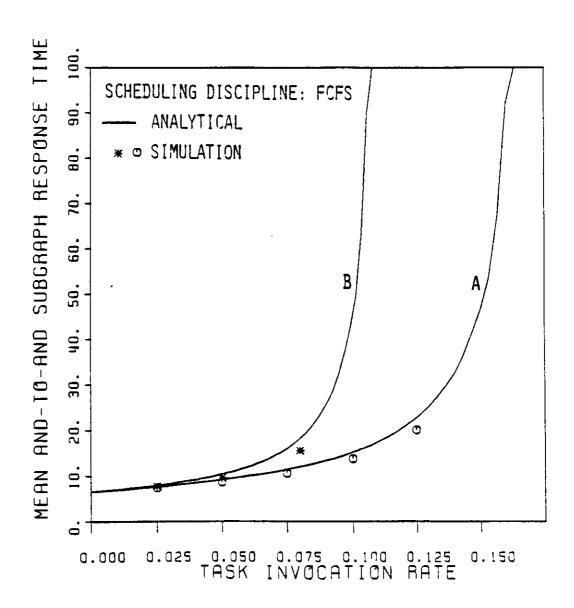

| Figure 2.9: Mean Response Time for the And-Fork to And-Join Subgraph of the Sample Control-Flow Graph                 | 40   |

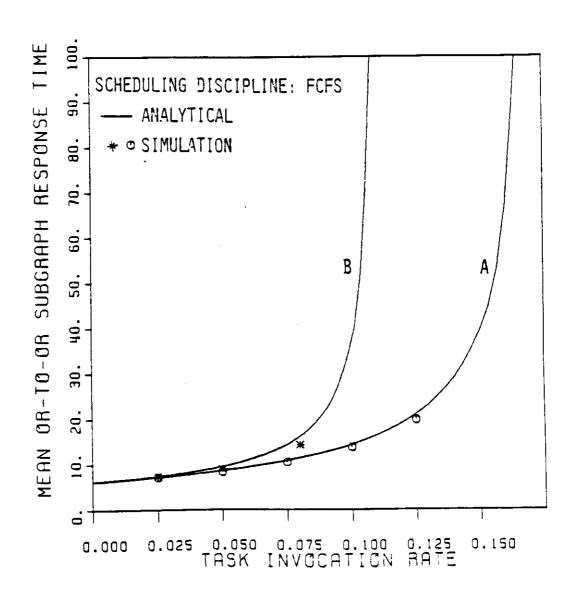

| Figure 2.10: Mean Response Time for the Or-Fork to Or-Join Subgraph of the Sample Control-Flow Graph                  | 41   |

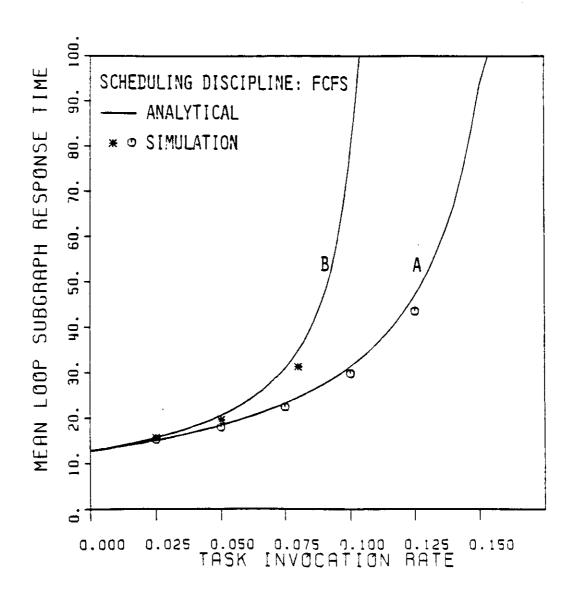

| Figure 2.11: Mean Response Time for the Loop Subgraph of the Sample Control-Flow Graph                                | 42   |

| Figure 2.12: Mean Task Response Time for the Sample Control-Flow Graph                                                | 43   |

| Table 2.3: Comparisons of Simulation Results with Analytical Predictions                                              | 45   |

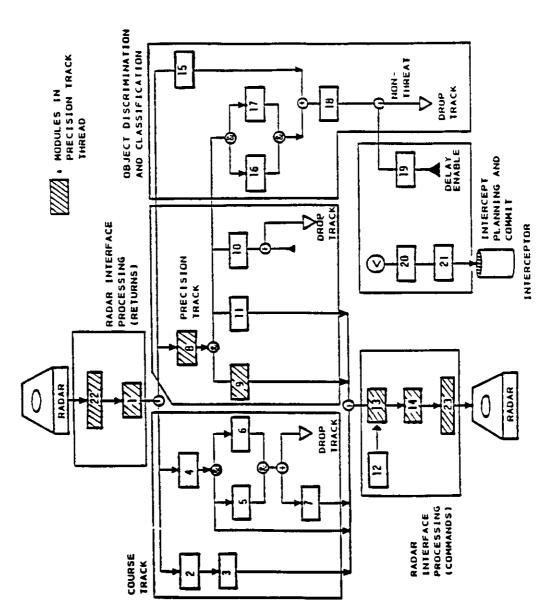

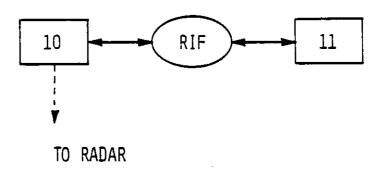

| Figure 2.13: The Task Control-Flow Graph for the DPAD System                                                          | 47   |

| Table 2.4: A Module Assignment for the DPAD System                                                                    | 48   |

| Table 2.5: Module Execution Times (Including Output IPC) for the DPAD System Averaged over 35 100-msec Time Intervals | 49   |

| Figure 2.14: Comparing Analytical Predictions with the DPAD Simulation                                                |      |

|                                                                                                                                                                      | 50         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.1: Two Processors: To Contrast the PR Effect                                                                                                                | 55         |

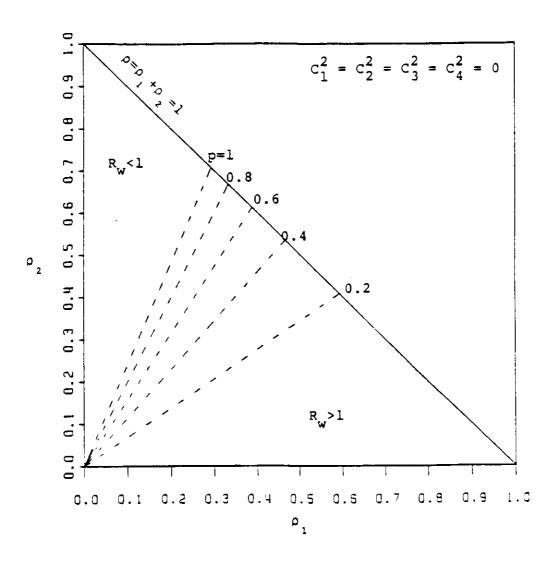

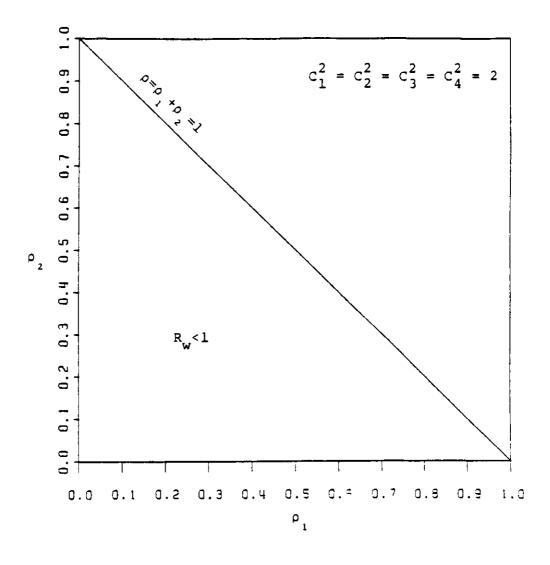

| Figure 3.2: Conditions for the PR Effect for Deterministic Module Execution Times                                                                                    | 65         |

| Figure 3.3: Conditions for the PR Effect for Exponential Module Execution Times                                                                                      | 6 <b>6</b> |

| Figure 3.4: Conditions for the PR Effect for Hyper-Exponential Module Execution Times with Squared Coefficients of Variations Equal to 2                             | 67         |

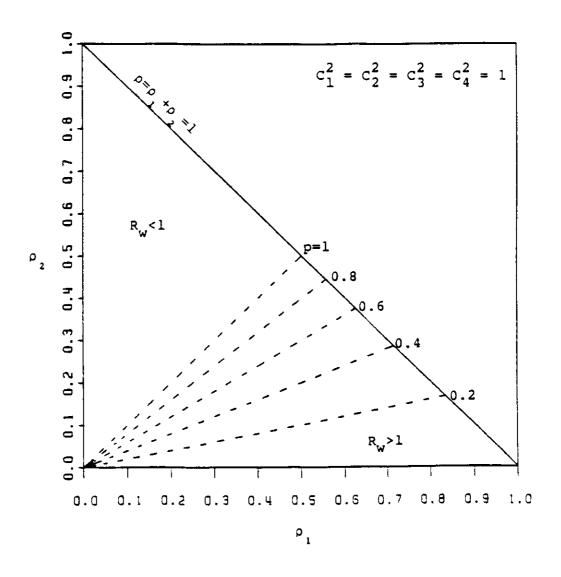

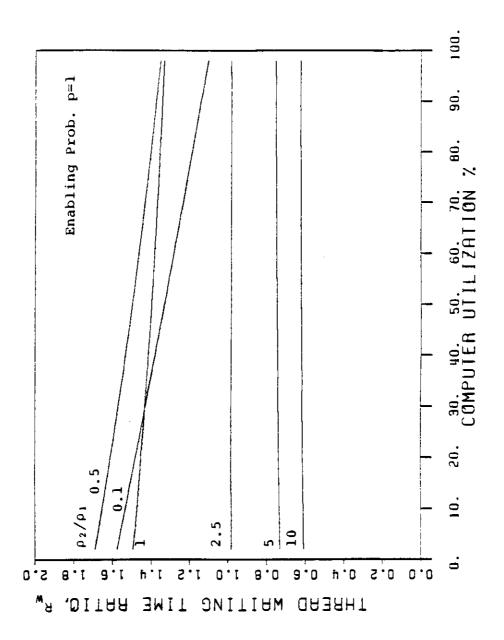

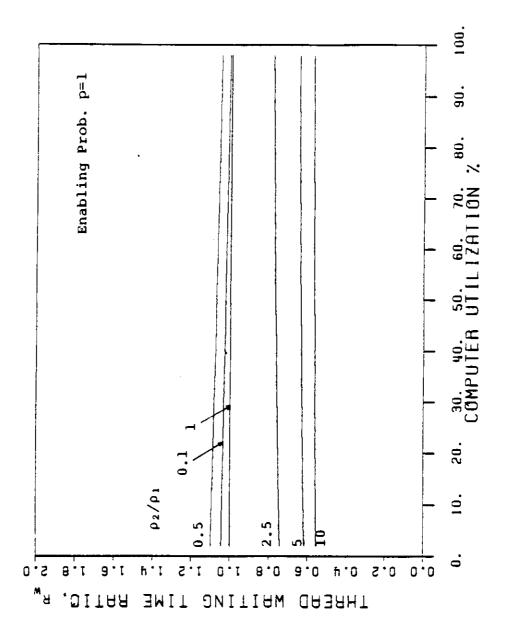

| Figure 3.5: Thread Waiting Time Ratio as a Function of Computer Utilization for Deterministic Execution Times                                                        | 69         |

| Figure 3.6: Thread Waiting Time Ratio as a Function of Computer Utilization for Exponential Execution Times                                                          | 70         |

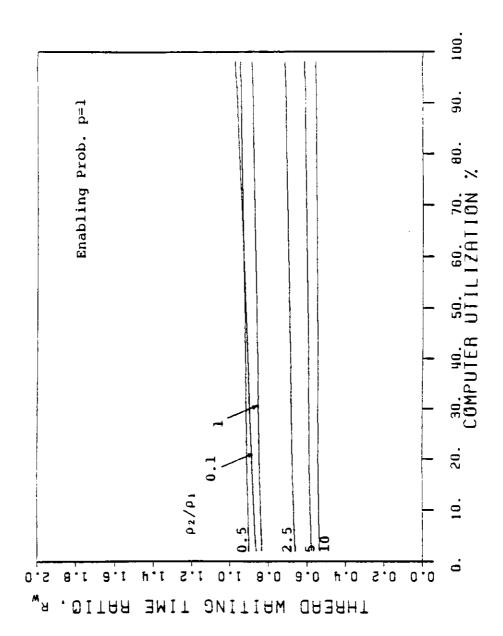

| Figure 3.7: Thread Waiting Time Ratio as a Function of Computer Utilization for Hyper-Exponential Execution Times with Squared Coefficients of Variations Equal to 2 | 71         |

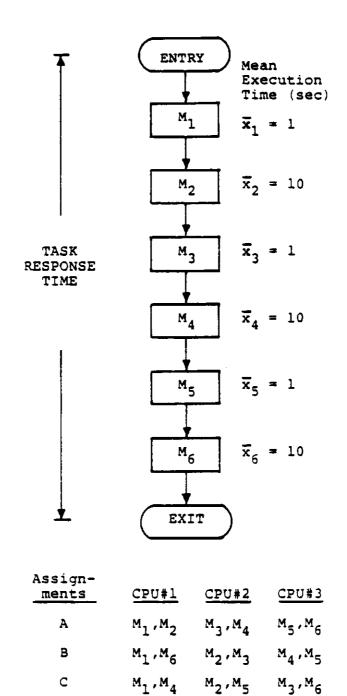

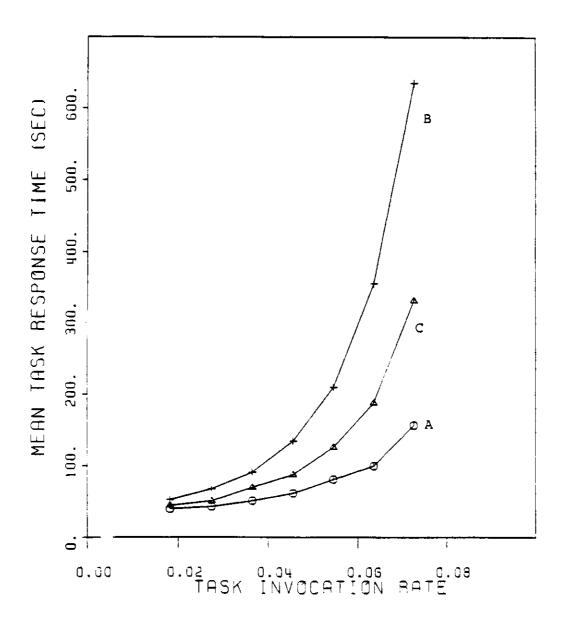

| Figure 3.8: Task Control-Flow Graph & Module Assignments for Illustrating PR Effects                                                                                 | 75         |

| Figure 3.9: Task Response Times for the Assignments                                                                                                                  | 77         |

| Figure 4.1: The Corresponding Task Control-Flow Graph for the RTDPS                                                                                                  | 85         |

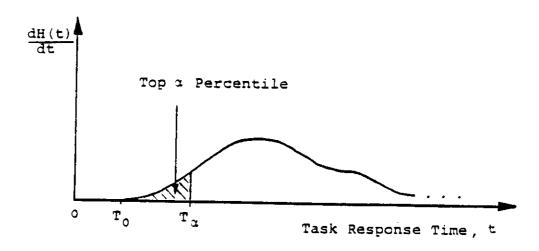

| Figure 4.2: A Sample Distribution of Task Response Times for Module Assignments                                                                                      | 91         |

| Table 4.1: Module Invocation Rates (No. of Enablements/msec) for the DPAD System                                                                                     | 97         |

| Table 4.2: Module Execution Times During Peak-Load Period for the DPAD System                                                                                        | 98         |

| Table 4.3: IMC's for the DPAD System                                                                                                                                 | 9          |

| Table 4.4: Suboptimal Module Assignments for Cases with 100 and 500 Random Initial Assignments                                                                       | 10         |

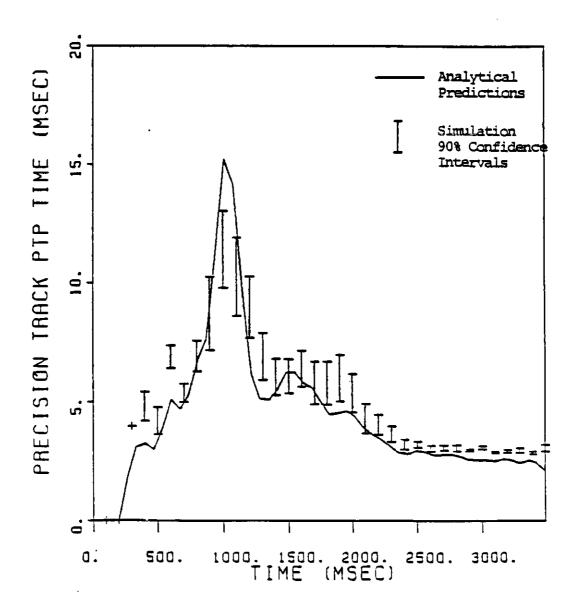

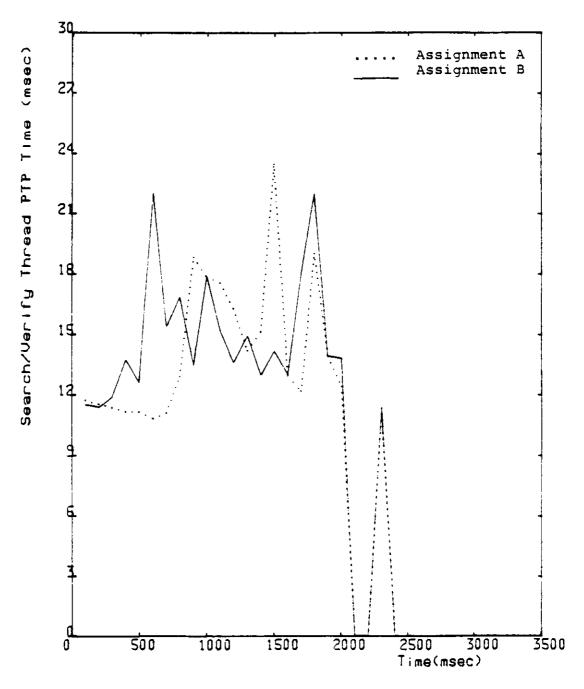

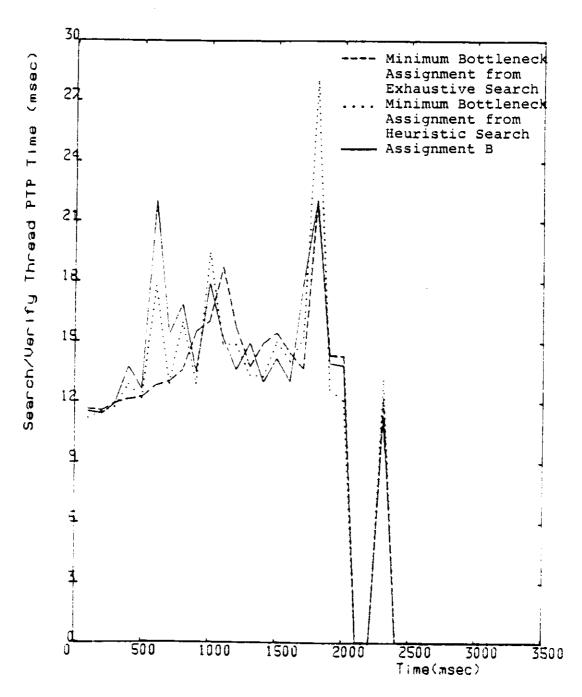

| Figure 4.3: Comparison of Search/Verify Thread PTP Time for Assignments A and B                                                                                      | 10         |

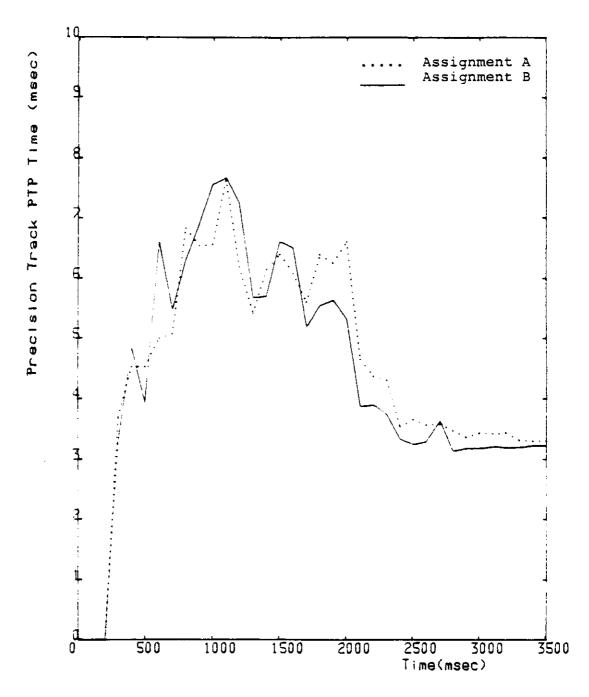

| Figure 4.4: Comparison of Precision Thread PTP Time for Assignments A and B                                                                                          | 10         |

| Figure 4.5: Comparison of Search/Verify Thread PTP Time for Minimum                                                                                                  |            |

| Bottleneck Assignments and Assignment B                                                                                                       | 105 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

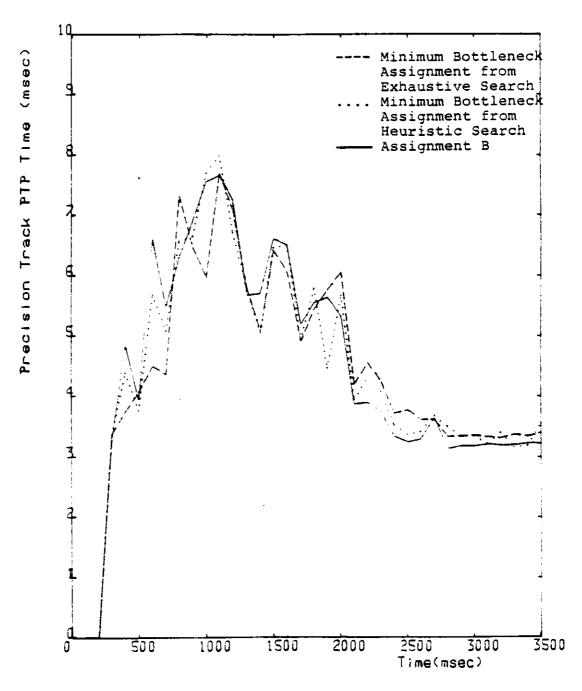

| Figure 4.5: Comparison of Precision Thread PTP Time for Minimum  Bottleneck Assignments and Assignment B                                      | 106 |

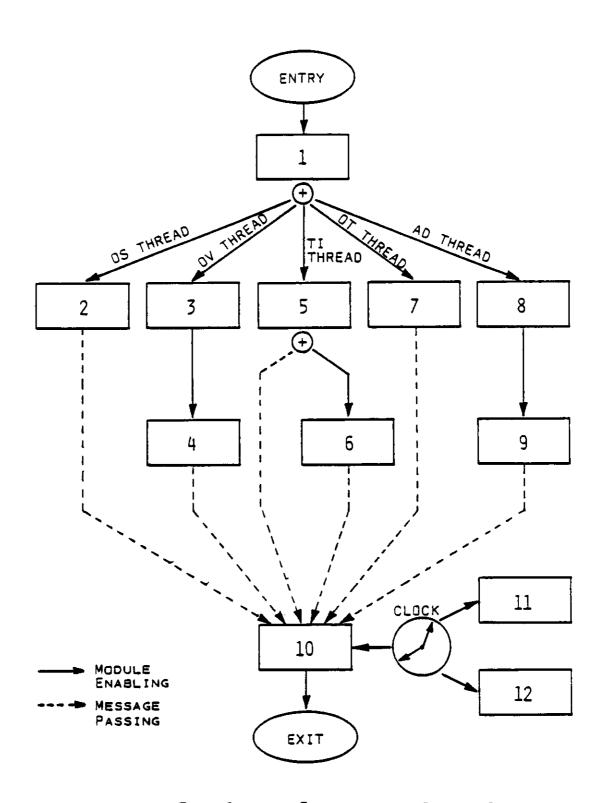

| Figure 5.1: Task Control-Flow Graph for Sentry System                                                                                         | 123 |

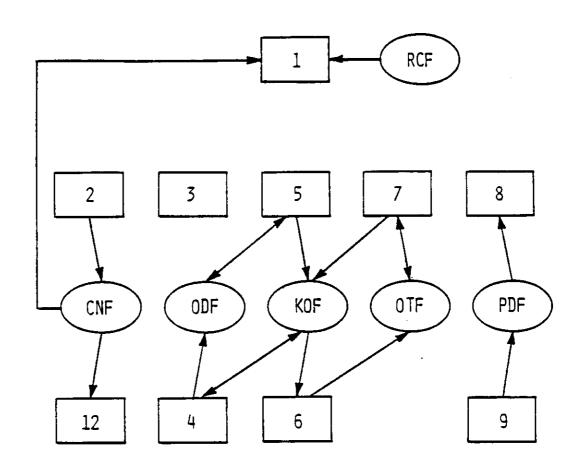

| Figure 5.2: Shared Data Files in the Sentry System                                                                                            | 125 |

| Table 5.1: Module Execution & File Access Times for the Sentry System                                                                         | 127 |

| Table 5.2: IMC Times for Various Module Pairs                                                                                                 | 128 |

| Table 5.3: Module Invocation Rates (No. of Enablements/msec) for the Sentry System                                                            | 129 |

| Table 5.4: Selected Sets of Thread Response Time Requirements                                                                                 | 131 |

| Table 5.5: Two Sets of Initial Module Multiplicities                                                                                          | 132 |

| Table 5.6: 11 Experiments with Selected Requirements, Module Multiplicities and the Penalty Scaling Constants                                 | 133 |

| Table 5.7: The Performance of the Sub-Optimal Module Assignment & the RMAP Algorithm After Iterating with 500/1000 Random Initial Assignments | 134 |

| Table 5.8: The Sub-Optimal Module Assignments for these 11 Experiments                                                                        | 136 |

| Figure A.1: Aggregating a N-Thread And-Fork to And-Join Subgraph                                                                              | 155 |

| Figure C.1: Arrival Processes and Service Times of the HOL Queueing                                                                           | 165 |

# LIST OF NOTATION

# Roman Capitals

- A Module assignment matrix with elements  $A_{ij}$

- D<sub>net</sub> Average interconnection network delay

- $D_{\textit{net}}(i,j)$  Average interconnection network delay incurred by messages from module i to module j

- D(A) Vector of thread response time discrepancies for module assignment A with elements  $d_i(A)$

- ${\it F}\,$  The objective function which represents the task response time model

- G Task control-flow graph

- LWP(A) The Processor with the longest average waiting time for module assignment A

- $R_w$  Thread waiting time ratio

- $\ensuremath{\mathcal{S}}$  The set of all modules of the application task

- $S_i$  The set of modules of thread i

- $S_L$  The set of modules residing on LWP

- $S_R$  The set of candidate modules for further replication on SWP

- SWP(A) The Processor with the shortest average waiting time for module assignment A

- $T_c$  Matrix of average IMC times with elements  $\overline{t_c}(i,j)$

- $T_{obj}$  Objective criterion for replicated module assignment problem

- $T_{pn}$  Penalty delay function for replicated module assignment problem

- Tptp Mean task response time

- T(i) Average response time for module i

- $U_i^*(s)$  Laplace Transform of execution time of  $i^{th}$  module bulk invocation

- W(R) Vector of required mean module waiting times with elements  $\overline{w_i}(R)$

- X Vector of module execution times with elements  $\overline{x}(i)$

## Small Roman

- a Scaling constant for the penalty delay of the objective function in replicated module assignment problem

- $c_i^2$  Squared coefficient of variation of execution time for module i

- $d_i(A)$  Response time discrepancy for thread i for module assignment A

- p Enabling probability of a consecutive module pair

- $p_{ij}$  Probability that module i enables module j upon completion of execution

- r Mean execution time ratio for a consecutive module pair

- t(i) response time (a random variable) for module i

- $\overline{t_i}(A)$  Average response time for thread i for module assignment A

- $\overline{\iota_i}(R)$  Average response time requirement for thread i

- $\overline{t}_c(i,j)$  Average IMC time from module i to j

- $\overline{u_i^n}$   $n^{th}$  moment of execution time (service time) for  $i^{th}$  module bulk invocation

- w Average module bulk waiting time

- $\overline{w}_i(R)$  Required mean module waiting time for thread i

- $\overline{x}(i)$  Average execution time for module i

## Greek

- $\alpha_i$  Initial Multiplicity of Module i

- λ Task invocation rate

- $\lambda_i$  Invocation rate for the  $i^{th}$  module bulk or module i

- $\sigma_{\text{net}}^2$  Variance of interconnection network delay

- $\sigma_w^2$  Variance of module bulk waiting time

- $\sigma_c^2(i,j)$  Variance of IMC time from module i to j

- $\sigma^2(c)$  matrix of variances of IMC times with elements  $\sigma^2_c(i,j)$

- $\sigma_i^2(i)$  Variance of response time for module i

- $\sigma_x^2(i)$  Variance of execution time for module i

- $\sigma^2(x)$  Vector of variances of module execution times with elements  $\sigma_x^2(i)$

- p total processor utilization (loading)

- $\rho_i$  Processor utilization due to module i

- $\rho_{M}$  Average processor utilization due to a module of the task

## **ACKNOWLEDGEMENTS**

I would like to express my most sincere thanks to my committee chairman, Professor Wesley W. Chu, for his guidance, friendship, encouragement, and insightful comments during the course of this research. Thanks are also due to Lance M. Lan formerly of UCLA for sharing with me his DPAD Simulation results, James Huang and Dennis Townsend of Titan Systems, Inc. for their technical information on the Sentry System. I also thank my committee members: Professors Milos Ercegovac, D. Stott Parker, Harold Borko and James MacQueen for their encouragement and serving in the committee. I also want to thank Jung Min An, Joseph Bannister and Joseph Hellerstein for their stimulating discussions during this research, as well as Laurel Hendrix for her secretarial and administrative assistance. I am grateful to members of Chinese Bible Church at West Los Angeles for their concern and spiritual support.

Additionally, I would like to thank my parents, Kwok and Shun-Yeung, and other family members for their love and emotional support. Finally, I owe a great debt of thanks to Miranda (Mei-Ling) whose love, patience, sensitivity, and devotion kept my spirit and motivation from waning and, having completed my Ph.D., she made it all worthwhile.

This work was supported in part by U.S. Army Contracts No. DASG60-79-C-0087 and subsequent renewals of the same contract, and Univ. of California MICRO Contract No. 4-482516-19900.

#### VITA

| January 6, 1958 | Born, Hong Kong                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------|

| 1976-1980       | B.S. in Electronics, The Chinese University of Hong Kong, Hong Kong                              |

| 1979            | Project Assistant, Royal Observatory of Hong Kong                                                |

| 1980-1982       | M.S. in Computer Science,<br>University of California, Los Angeles                               |

| 1981-1983       | Teaching Assistant/Associate, Computer Science Dept.,<br>University of California, Los Angeles   |

| 1983-1985       | Postgraduate Research Engineer, Computer Science Dept.,<br>University of California, Los Angeles |

#### **PUBLICATIONS**

"Task Response Time Model & Its Applications for Real-Time Distributed Processing Systems," coauthored with W.W. Chu, *Proceedings of 5th Real-System Symposium*, Texas, Dec.4-6, 1984, pp.225-236.

"Reservation Channel Access Protocol for High Speed Local Networks with Star Configurations," coauthored with W.W. Chu and W. Haller, *IEEE Trans. on Computer*, Vol.C-32, No.8, Aug. 1983, pp.763-766.

"A Contention Based Channel Reservation Protocol for High Speed Local Networks," coauthored with W.W. Chu and W. Haller, *Proceedings of 7th Conf. on Local Computer Networks*, Minneapolis, MN, Oct. 1982, pp.110-117.

"On the Effects of Non-Uniform Propagation Delays on the Performance of Multi-Access Protocols," Working Paper No.82008, Advanced Teleprocessing Systems Group, Computer Science Dept., UCLA, Spring 1982.

"A New Look at Partial Fraction Expansion from a High-Level Language Viewpoint," coauthored with C.F. Chen, Computer & Maths. with Appls. (Great Britain), Vol.7, No.5, 1981, pp.361-367.

# ABSTRACT OF THE DISSERTATION

Task Response Time and Module Assignment for Real-Time Distributed Processing Systems

by

Kin Kwong Leung

Doctor of Philosophy in Computer Science University of California, Los Angeles, 1985

Professor Wesley W. Chu, Chair

Task response time is an important system performance measure for real-time systems. An analytic model is introduced to estimate task response time for loosely coupled distributed processing systems with real-time applications. The model considers such factors as assignment of modules to computers, module precedence relationships, interprocessor communications, interconnection network delay and module scheduling policy. Simulation experiments are used to validate the model assumptions and to show the accuracy of the model.

The analytic model is first employed to investigate the effects of module precedence relationships on response times. Our study reveals that the distributions of module execution times and the mean execution time ratio for a pair of consecutive modules are major factors for the effects.

The task response time model is then used to study module assignment for distributed systems. Based on the model, a new local search algorithm for module assignment is developed. Firstly, each module is assumed to be allocated to a single computer. Task response time is the optimality criterion, and the analytic model becomes the objective function. Search strategies are established to search for better module assignments. Further, the algorithm is extended to handle module replications; that is, modules may be replicated on several computers. The design objective for replicated module assignment is to minimize task response time with the thread response time constraints. A new objective criterion which is the sum of task response time and possible penalty delay to account for the violations of thread response time constraints is introduced. With this objective function, not only module copies are optimally assigned to computers, the proper module multiplicities are also iteratively determined by the algorithm so as to achieve the objective.

The algorithm is validated by applying to two distinct distributed systems for space defense applications. One system does not require module replications while the other does. The sub-optimal module assignments generated by the algorithm provide excellent response time performance on both systems since the analytic model has considered all major factors that affect task response time. Therefore, the algorithm can serve as a valuable tool for distributed systems design.

#### CHAPTER 1

#### INTRODUCTION

# 1.1 REAL-TIME DISTRIBUTED PROCESSING SYSTEMS

In real-time systems, a task is a sequence of system functions which must finish within a specified time period if the systems are to perform properly (e.g., process control and space defense applications). To meet the real-time requirements, it is desirable to share the processing workload among several computers (processors 1). This technique is referred to as distributed processing. In addition to execution speedup, distributed processing can also provide cost-effective system designs, incremental system growth, better system reliability, and grace performance degradation in case of failures, etc.

The spectrum of distributed processing systems ranges from multiprocessor systems in which processors share common memory to sets of processors which are geographically dispersed and communicate via message exchanges. Herein, we consider real-time distributed processing system (RTDPS) (e.g., the Distributed Processing Architecture Design (DPAD) System [GREE80]) which is commonly known as loosely coupled distributed processing system. This system is solely dedicated for a

<sup>&</sup>lt;sup>1</sup> "Computers" and "processors" are used interchangeably in this dissertation.

given real-time application task. The RTDPS consists of a set of processors connected together by an interconnection network which may be a fully connected network, a store-and-forward network or a local area network (e.g., a multi-access communication channel). Communications among processors are provided in the form of message exchanges.

Each processor has its own memory and self-autonomy thus all processors are equally important and no master-slave relationship among processors exists. A distributed operating system (DOS) is residing on each computer. Besides performing the functions such as memory allocation, scheduling and file management, the DOS also participates in the concurrency control, interfaces with communication subsystems, and exchanges information with other computers to guard against overloading and system failures. A typical execution cycle on each computer runs in the following sequence: processing messages from remote computers, dispatching a job for execution, sending output messages to remote computers, and other miscellaneous system management work. For real-time applications, the DOS usually does not provide interrupt facility as: (1) to eliminate interrupt overheads; (2) to avoid complicated data inconsistency problems which may occur during interruptions; and (3) to keep the variance of response time small, otherwise may be largely increased due to program interruptions.

In a RTDPS, the application task is partitioned into a set of software modules (or simply, modules). The task is repeatedly invoked to meet the processing require-

ments (e.g., processing radar return signals). Task response time or port-to-port (PTP) time is defined as the time from the task is invoked to the completion of the task execution. In some cases, the response time for the executions of a sequence of modules, which is referred to as a thread, is of interest. The thread response time (or PTP Time of the thread 1) is the time from the request for the first module to the completion of the last module execution in the thread.

During the task execution, modules need to communicate with other modules via message exchanges. These messages are called intermodule communication (IMC). For a specific application task, the volume of IMC messages among modules is determined by the process of task partitioning. Therefore, it is desirable to partition the task to minimize the IMC among modules. In distributed systems, IMC is usually facilitated by sharing common data files and/or direct message exchange. The overhead for message exchanges on a local computer is usually small and can be assumed to be negligible in most systems. However, if IMC messages are sent to a remote computer via the interconnection network, the messages become interprocessor communication (IPC). Clearly, the IPC load in a distributed system depend on the IMC and the assignment of modules to computers. These IPC messages requires such extra processing as communication protocol and management of the distributed data files. IPC presents extra processing load on both the transmitting and the receiving computers. Therefore, IPC has significant impact on the system performance and response time. The importance of these impacts have been recognized by many

<sup>&</sup>lt;sup>1</sup>Unless specified for a thread, PTP time is referred to the response time of the entire application task.

researchers [JENN77, CHU78, MA82, CHU84].

If data are shared among modules residing on different computers, to provide fast local accessing and to enhance file availability, some of the shared data files are replicated on several computers. However, maintaining the data consistency of the replicated copies requires the use of a concurrency control mechanism. A number of consistency control techniques such locking, timestamp and exclusive-writer protocol [BERN81,CHU85a] have been proposed. Besides the extra processing overhead due to the concurrency control protocol, file replications also increase the total IPC on the system because more than one file copy need to be updated. In the contrary, if a file is not replicated on a local computer, accesses to the file during module executions become read/write requests on remote computers where the file is located. These remote file accesses as a form of IPC of course incur the interconnection network delay and wait for response on the remote computers, thus degrading the task response time.

Therefore, planning a distributed system is complicated by many such complex and interdependent design issues as task partitioning, module and file assignment, data base management algorithm, etc. Presently, there is no systematic methodology for designing distributed systems. Existing system designs use ad hoc methods which result in a trial-and-error approach. Since response time is an important performance measure in real-time systems, we conduct this research to develop an analytic model for estimating response time for distributed systems. The model can then be used as a unified approach for studying various distributed design issues and explor-

ing the tradeoffs among different choices.

# 1.2 SOME RELATED DESIGN ISSUES OF RTDPS

The merits of distributed processing: response time, throughput, system availability and incremental system growth, have made this system architecture appealing to many applications. However, the expected system performance and merits may not be accomplished unless the distributed system is properly designed. Here we discuss some important design issues of RTDPS which are related to the main theme of this research. The design issues discussed in the following include: (1) task partitioning, (2) module assignment (or task allocation 1), (3) module replication and (4) file allocation.

# 1.2.1 Task Partitioning

The main purpose of distributed processing is to fully utilize the available computing resources by distributing the processing workload on several computers. Thus, the first step to RTDPS design is to partition the application task into a set of smaller and well-defined subtasks which are implemented in programming languages. These software modules are ready for allocation to computers. In general, task partitioning is strongly dependent upon the nature and inherited parallelism of the application task under consideration. Although few results on this issue were published in the literature, system designers usually find the following guidelines useful for task parti-

In this dissertation, "task allocation" is to assign modules to computers. Thus we refer this process as to module assignment. Nevertheless, "task allocation" is a popular term.

tioning.

- (a) It is desirable to exploit the inherited parallelism of the application task. That is to partition the task such that synchronizations among modules are eliminated as much as possible. Therefore, modules can be executed concurrently on several computers.

- (b) Modules' execution times should not differ so much from each other because similar module sizes often facilitate even load balancing among computers. In addition, too large a module execution time may delay the response to the requests of some urgent module executions if module execution is non-interruptable. Too small a module usually wastes the computing capacity as much operating system overhead is incurred in scheduling when comparing with the amount of useful computation performed by the module.

- (c) The data input and output characteristics of each module are determined by task partitioning. It is advantageous to partition the task such that amount of IMC's among modules is small. As a result, the total IPC on the system can be kept small and most of the computing power is used for actual application processing.

Clearly these design factors are interrelated with each other. For example, in order to reduce IMC, in one extreme, one might keep the entire application task unpartitioned as no IPC will be generated on the computers. However, it totally neglects the possibility of concurrent module processing. In some situations, a large module

should not be further partitioned due to the nature of its processing requirements and/or avoidance of generating a large volume of IMC. Although we know little about the general approach to efficient task partitioning, a good task partitioning ought to be a proper balance and tradeoff among these factors.

In this context, we shall assume that the task of the RTDPS under consideration is well partitioned into modules and the precedence relationships among them can be represented by a task control-flow graph.

# 1.2.2 Module Assignment

The assignment of modules to processors affect the response time, throughput and system reliability. Several approaches to module assignment in distributed processing systems have been proposed [STON77, RAO79, PRIC79, MA82, CHOU82, EFE82, SHEN85, CHU85b, etc.]. These techniques include graph-theoretic, mathematical programming, and heuristic approaches. Instead of doing a survey on various module assignment strategies, here we discuss: (1) the key factors considered in these methods, and (2) their shortcomings when applying to the RTDPS. These drawbacks have motivated us to investigate some better approach to module assignment for RTDPS.

The key parameters considered in these approaches mainly are (a) module execution times (costs) and (b) interprocessor communication times (costs). Their basic notion in performing module assignment is to balance the computational load, including (a) and (b), among the processors such that either the total system time (cost) is

minimized or computer loads are well balanced. Besides balancing the processing load, logical and precedence relationships among modules, queueing effect and interconnection network delay also have significant influence on the performance of module assignments. Especially for RTDPS where the response time is an important performance measure, these effects should be considered in module assignment.

[STON77] and [RAO79] use graph-theoretic algorithms which are tractable only for systems with two computers. Algorithms proposed in [MA82], [EFE82], [CHOU82] and [SHEN85] balance the workload on computers but neglect the impacts of module precedence relationships. Further, the approaches proposed in the literature usually assume that the application task is invoked only once. As a result, the queueing effect is ignored which affects the response time. This assumption used in the algorithms do not represent the actual operating environment in a RTDPS. Therefore, their "optimal" module assignment does not necessarily provide good response time. Moreover, the interconnection network delay is disregarded in the module assignment methods, but the network delay may have tremendous effect on system response time, especially if the network bandwidth in the RTDPS is not sufficiently large. In one extreme, modules may prefer to be allocated to a single processor instead of several processors to avoid the prohibitively high network delay. In summary, all these aforementioned factors substantiate that mere balancing the workload among processors is inadequate in module assignment to achieve a low system response time.

### 1.2.3 Module Replication

More importantly, all module assignment algorithms proposed so far do not consider module replications. This is, modules may be allocated to several processors instead of a single processor for executions. Sometimes, certain modules need to be replicated in RTDPS due to the considerations of response time requirements, system reliability, and/or some other constraints. In general, module replications may improve the system performance under one or more of the following circumstances:

## (a) To meet strict response time specifications

In general, some modules of a given real-time application task are more urgent (or crucial) than others. And, these modules require rapid response from the processors. For example, the process of discrimination of offensive missiles is far more critical in terms of response time than search operations for new incoming objects in a space defense application. Therefore, it is desirable to satisfy these urgent modules with a much stringent response time requirement. Apparently, one way to meet the requirements is merely to assign a high execution priority to these modules thus receiving quicker response at the expense of other modules. However, if the requests for the urgent module executions come in a bursty manner, this approach may violate their real-time constraints. On the other hand, these modules may be replicated on several processors in addition to being assigned with a high priority. Thus, bursty execution requests can be routed to and executed on several processors to share the processing load for achieving the desired response times. Hence, besides load balancing,

module replication is also a good alternative to meet strict response time specifications.

## (b) To enhance system reliability

Module replication is similar to file replication in RTDPS in terms of enhancing system reliability. By replicating the important modules on several processors, requests for these modules can be processed on more than a single site. Therefore, module replications improve the system availability for the essential module executions in the presence of system failures.

## (c) To achieve load balancing

The loading on each computer depends on the execution times and invocation rates for the residing modules. Clearly, the module execution times are predetermined by the task partitioning process in the early stage of system design. Of course, these execution times cannot be changed at the phase of module assignment. However, if modules are replicated, requests for these modules can be routed to the several computers for executions. Thus replicating modules in effect reduces the invocation rate for each replicated module copy on a computer. By adjusting the multiplicity of a replicated module, one can reduce the invocation rates for the replicated modules on each computer to a desirable level. As a result, the processing load due to the replicated modules can be evenly balanced on several computers. More importantly, module replications therefore do provide a new degree of flexibility for

efficient system design in the hope that the computing resources are better utilized and the response time requirements can be satisfied.

The current module assignment algorithms neglect: repeated task invocations, IPC, module precedence relationships, queueing effects, interconnection network delays, and module replications. The new approach should remedy these drawbacks.

## 1.2.4 File Allocation

The other related design consideration for RTDPS is to replicate and distribute data files so that they can be efficiently accessed and generate less amount of IPC.

This is commonly referred to as file allocation (or file assignment).

The optimal file allocation problem for multiprocessor systems with multiple files was firstly studied by Chu [CHU69]. Chu considered storage and transmission costs, file lengths, and read and update rates. The optimal allocation yields minimum overall operating costs. Subsequently, a lot of research effort [CASE72, MORG77, CHEN80, COFF81, RAMA83, etc.] has been dedicated to the problem. Most of them partitioned the multiple file allocation problem to multiple single file allocation subproblems. Minimizing the communication and storage costs is commonly used as an optimality criterion. The allocation models are usually formulated in the form of a 0-1 integer programming problem. In particular, both [CASE72] and [COFF81] attempted to determine the optimal number of copies of a data file. [MORG77] considered the placement of files and programs which use these files. [RAMA83] showed the isomorphism between the simple file allocation problem (without

response time consideration) and the single commodity warehouse location problem in operations research, therefore some results by operations researchers can be adopted for solving the file allocation problems.

In RTDPS design, module and file assignment problems are coupled together:

(1) since file accesses are generated by module executions, file access rates on each computer are dependent upon how modules are assigned to computers; and (2) module waiting times and processing loading on computers also depend on the volume of IPC's generated due to file accesses. Morgan and Levin [MORG77] considered the assignment of program and data files to computers in which file accesses are generated from program executions. However, the followings are their drawbacks when applying to RTDPS environments:

- (a) The model only considers the communication and storage costs for file accesses and programs, but neglects IPC, processor loadings and queueing times.

- (b) "Programs" in [MORG77] are equivalent to modules in our RTDPS. However, [MORG77] does not take the logical and precedence relationships among modules into consideration.

- (c) Communication and storage costs are assumed to be known in the allocation model. Since response time is an important performance measure in RTDPS, it is desirable to approximate the response times by proper selections of communication and processing costs. However, these costs are usually difficult to estimate in a loaded environment like RTDPS.

Of course, it will be advantageous to perform module and file assignments at the same time. As a result, the interactions among modules and data files can be considered and the task response time for the RTDPS can then be truly minimized. However, simultaneous assigning modules and files to computers in order to minimize the task response time is very complicated because actually four design sub-issues are involved in the problem: (1) to determine the optimal number of copies for each module; (2) to allocate the module copies to computers; (3) to determine the optimal number of copies of each data file; and (4) to allocate file copies to computers. Even a simple module assignment problem in a multiprocessor system has been proved to be a NP-complete problem [GARE77] for which a polynomial time bound algorithm is very unlikely to exist. Thus all four sub-issues together further increase the problem complexity and make it more difficult to formulate. As a first step to this complex problem, we concentrate ourselves on module assignment aspect. In this research, we treat the file allocation aspect by assuming each data file which is shared by several modules is stored (or replicated) on each computer which needs access (read and/or write) to the file.

# 1.3 CONTRIBUTIONS OF THIS RESEARCH

The major contributions of this research lie in three areas: (1) a new analytic model to estimate task response time for RTDPS is introduced; (2) the model is employed to study the impacts of module precedence relationships on response times; and (3) based on this model, a new module assignment algorithm for the distributed systems is developed.

Response time is an important design criterion for real-time systems. Therefore, it is desirable to design a RTDPS such that its response times are minimized. In general, either analytical or simulation techniques can be used to study response times for RTDPS. However, simulation methods usually tend to be more expensive and time-consuming. These shortcomings have led us to pursuing analytical approaches. To overcome the inadequacies of current analytical approaches, a new analytic model is introduced to estimate the task response time for the distributed systems. The model considers such factors as module precedence relationships, IPC, interconnection network delay, module scheduling policy, and assignment of modules and files to computers. Simulation experiments are used to validate the model assumptions and show the accuracy of the model.

The analytic model can be used in various design study for distributed systems. Firstly, the model is employed to study the importance and the effects of module precedence relationships on response times. Secondly, since the analytic model accurately estimates task response times for various module assignments, the model can be used to perform module assignment. Based on the model, a new local search algorithm for module assignment in RTDPS is developed. In this algorithm, the task response time becomes the objective criterion which is optimized over the solution space — module assignments, and the model is used as the objective function for the problem. Search strategies are established in the algorithm to look for better module assignments. We first consider the cases where each module is allocated to a single computer. Then, we extend the algorithm to handle cases where each module

may be replicated on several computers. For the distributed systems where module replications are required, not only the module copies are optimally allocated to computers, but the appropriate module multiplicities are also iteratively determined by the algorithm.

The module assignment algorithm is applied to two distinct distributed systems. One of them requires module replications while the other does not. The solutions from the algorithm provide excellent response time performance because the task response time model has considered all major factors that affect the task response time in the distributed systems. Therefore, the module assignment algorithm can serve as a valuable tool for distributed systems design.

#### CHAPTER 2

### TASK RESPONSE TIME MODEL FOR RTDPS

## 2.1 INTRODUCTION

With the advent of low-cost VLSI and communication technologies, distributed processing has become an economically and technologically attractive computer architecture. The distributed system considered here consists of multiple computers, each with its own memory and peripherals, connected by an interconnection network. This type of systems is commonly referred to as loosely coupled distributed processing systems.

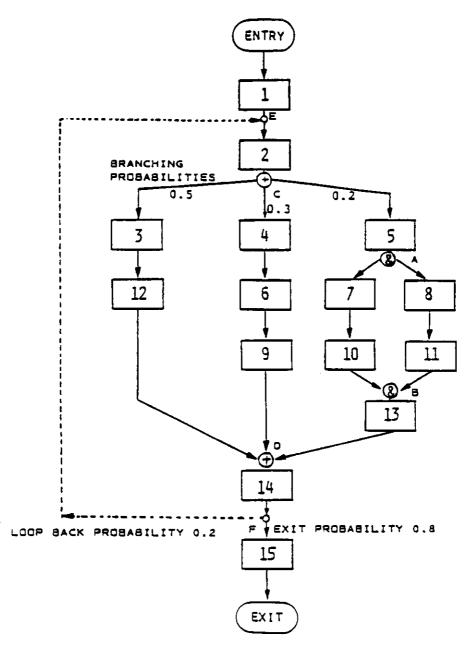

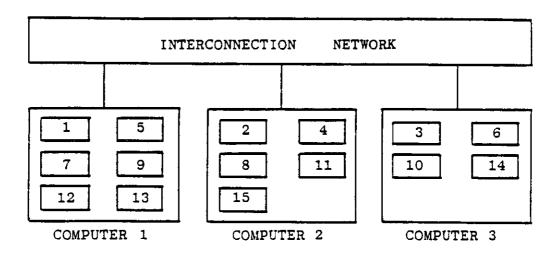

Recall that an application task in a RTDPS is often partitioned into several sub-tasks (i.e., software modules) which are assigned to a set of computers for processing. An example of a task consisting of fifteen modules assigned to a system with three computers is shown in Figure 2.1. The logical structure and precedence relationships among the software modules may be represented by a task control-flow graph. The task is repeatedly invoked to meet the processing requirements (e.g., processing return signals from a radar). After a module completes its execution, it sends messages to enable (invoke) its succeeding module(s) as indicated in the task

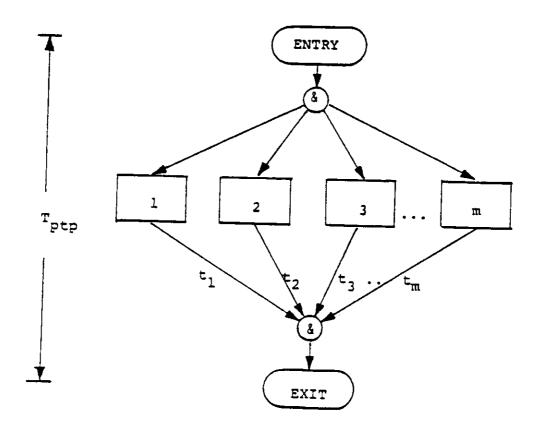

AND-FORK TO ANO-JOIN SUBGRAPH: A TO B

OR-FORK TO OR-JOIN SUBGRAPH: C TO O

LOOP SUBGRAPH: E TO F

TASK: ENTRY TO EXIT

Figure 2.1a A Sample Task Control-Flow Graph

Figure 2.1b Assignment of Modules to Computers (A Loosely Coupled Distributed System)

control-flow graph. In addition, when a module finishes its execution, it may also send messages to update the shared data files on other computers. Such message exchanges among modules are referred to as intermodule communication (IMC) [CHU84]. The overhead for communications among modules that reside on the same computer is usually small and can be assumed to be negligible. If messages are sent between modules that reside on different computers, the messages are called interprocessor communication (IPC). IPC requires such extra processing as communication protocol and management of the distributed data files, and incurs interconnection network delay. Therefore IPC has significant impact on the system performance and response time.

If data are shared among modules residing on different computers, some of the shared data files are replicated on several computers. However, maintaining the data consistency of the replicated copies requires the use of a concurrency control mechanism (e.g., locking, timestamp, exclusive-writer protocol). Therefore, planning a distributed system is complicated by many such complex and interdependent design issues as module and file assignment [CHU80], module scheduling policy, database management algorithm, etc. Presently, there is no systematic methodology for designing distributed systems. Existing system designs use ad hoc methods which result in a trial-and-error approach. Further, since RTDPS often are required to perform time critical functions, response time is an important performance measure. Simulation techniques are used to estimate the response time, but such approaches are time-consuming and expensive. This motivates us to develop an analytic model for

estimating the response time for these systems. The model can be used as a unified approach for studying various RTDPS design issues and exploring the tradeoffs among different design choices.

We shall first present our task response time model based on module response times and the weighted task control-flow graph. Next, we present a set of simulation experiments to validate the assumptions used in the model for various types of logical structures and precedence relationships among modules. Finally, we discuss the use of the model to study the interrelationships among task response time, module assignment, precedence relationships, scheduling policy for module executions, and database management algorithms.

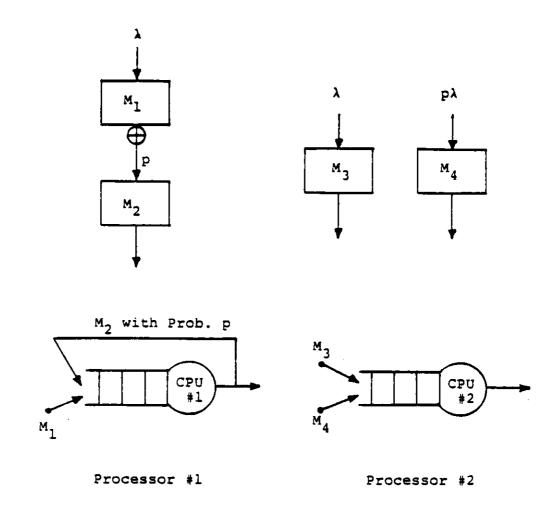

#### 2.2 A TASK RESPONSE TIME MODEL

Queueing networks [BASK75, HEID82, LAZO84] are commonly used to model distributed processing systems. In such models, computers are represented as servers, modules as customers, and task invocations correspond to external arrivals. Customers are routed for service in accordance with the task control-flow graph and the module assignment. In distributed systems, a module may enable more than one modules. This is referred to as a FORK in the graph. Alternatively, a module may have several immediate predecessor modules which must complete their executions before the succeeding module can be executed. This is referred to as a JOIN. When a control-flow graph consists of FORKs and JOINs, the routing scheme in the queueing network model is inadequate to represent the logical relationships among modules.

Thus the system cannot be represented by a tractable queueing network model.

Therefore, we introduce a new model to estimate the task response time.

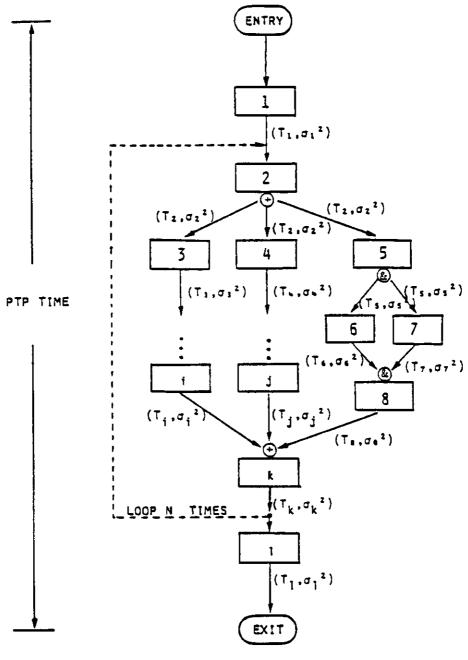

Task response time, or port-to-port (PTP) time, is the time from the request of a task invocation to the completion of its execution. Since a task may be repeatedly invoked and the modules are enabled according to the sequence as indicated in the control-flow graph, task response time consists of module waiting times, module execution times and precedence waiting times. Module waiting time is the time from a module invocation arrival until it starts its execution on a computer. This waiting time is the time spent waiting for module executions and input IPC processings. Module execution time is the sum of a module's execution time and its output IPC time. Let the sum of a module's waiting time and execution time be denoted as module response time. The precedence waiting time is the intermodule synchronization delay due to the precedence relationships among modules. Our task response time model consists of two sub-models: module response time model and weighted control-flow graph model. The first sub-model computes the module response times, while the latter considers the precedence waiting times.

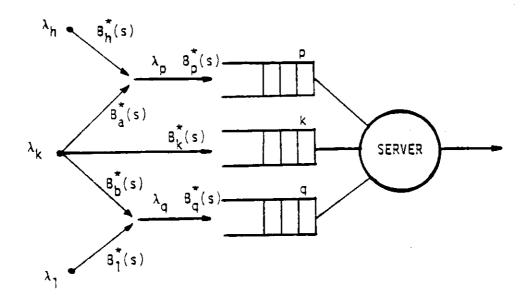

# 2.2.1 Module Response Time Model

For a given module assignment, each computer will execute a fixed set of modules. The response time of a module is the time from its invocation to the completion of its execution. Thus module response time includes waiting (queueing) time and module execution time. If a module needs to send messages to other computers,

the output IPC time is included as a part of the module execution time. Further, these IPC's are transmitted over the interconnection network, and eventually arrive at their destinations. These input IPC's on the destination computers can be viewed as a special module which also contends for processing. Based on the module assignment and IMC's among modules, IPC processing times can be obtained. Let the module execution times be characterized by probability distribution functions (PDF's). Then each computer can be modeled as a queueing system with several modules (customers of different types) with specified service distributions. Based on the logical structures among modules and task invocation rate, the invocation rate of each module on the computer can be determined. In queueing terminology, module invocations are customer arrivals. If several modules on the same computer are invoked simultaneously, this results in a bulk module invocation.

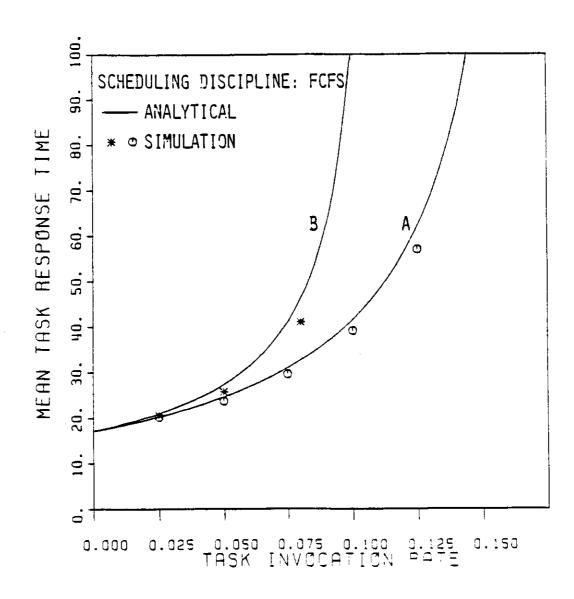

In our model, we assume that (1) the module invocation arrival (single or bulk) processes are independent of each other, and (2) module invocation interarrival times are Poisson distributed. To illustrate the concept, let us determine the modules' response times on a computer that uses *first-come-first-serve* (FCFS) scheduling policy of for module executions.

Consider a computer that has m distinct module invocations (single or bulk invocations), and the arrival rate for the  $i^{th}$  module invocation be  $\lambda_i$  and the Laplace Transform (L.T.) of the service requirement be  $U_i^*(s)$  for i=1,2,...m. One of these m

<sup>&</sup>lt;sup>1</sup> The model can be applied to other module scheduling policies with the use of appropriate queueing delay equations.

module invocations (say the  $c^{th}$ ) represents the input IPC on the computer. Thus  $\lambda_c$  and  $U_c^*(s)$  are the arrival rate and L.T. of processing time for the input IPC. For the  $i^{th}$  bulk invocation that invokes a set  $S_i$  of distinct modules (referred to as module bulk), the corresponding service requirement is  $U_i^*(s) = \prod_{j \in S_i} X_j^*(s)$ , where  $X_j^*(s)$  is the L.T. of the service time of module j.

Based on the assumptions 1 and 2, this queueing system is an extension of the regular FCFS M/G/1 queue with total arrival rate  $\lambda = \sum_{i=1}^{m} \lambda_i$ , and the L.T. of service time for each invocation arrival is  $U^*(s) = \sum_{i=1}^{m} \frac{\lambda_i}{\lambda} U_i^*(s)$ . For the M/G/1 queue, the first two moments of the module bulk waiting time from the bulk invocation arrival until its first module starts to execute are

$$\overline{w} = \frac{\sum_{i=1}^{m} \lambda_i \overline{u_i^2}}{2(1-\rho)} \tag{2.1}$$

and

$$\overline{w^2} = 2(\overline{w})^2 + \frac{\sum_{i=1}^{m} \lambda_i \overline{u_i^3}}{3(1-\rho)}$$

(2.2)

where:

$u_i^n = n^{th}$  moment of service time for  $i^{th}$  module invocation,

$$\rho = \text{server utilization } = \sum_{i=1}^{m} \lambda_i \overline{u_i^{\perp 1}},$$

$\overline{w}$  = average module bulk waiting time.

From Eqs.(2.1) and (2.2), we obtained the variance of module bulk waiting time as

$$\sigma_{w}^{2} = \overline{w^{2}} - (\overline{w})^{2} = 2(\overline{w})^{2} + \frac{\sum_{i=1}^{m} \lambda_{i} \overline{u_{i}^{3}}}{3(1-\rho)} - \left\{ \frac{\sum_{i=1}^{m} \lambda_{i} \overline{u_{i}^{2}}}{2(1-\rho)} \right\}^{2}$$

(2.3)

In a bulk invocation, a set of modules are invoked at the same time. Based on the resource requirements, the operating system schedules the execution sequence for these modules. Let the sequence be  $j_1, j_2, ..., j_{k-1}, j_k, j_{k+1}, ...$  The response time (a random variable) for module  $j_k$  is

$$t(j_k) = w + \sum_{i=1}^{k} x(j_i)$$

(2.4)

where:

w =module bulk waiting time,

$x(j_i) =$  execution time for module  $j_i$ .

The average response time  $T(j_k)$  for module  $j_k$  can be obtained by taking the expected values of Eq.(2.4). We have

$$T(j_k) = \overline{w} + \sum_{i=1}^k \overline{x}(j_i)$$

(2.5)

Since w,  $x(j_i)$  and  $x(j_k)$  are independent random variables, the variance  $\sigma_t^2(j_k)$  of the response time for module  $j_k$  is the sum of variances of each component in Eq.(2.4). Hence

$$\sigma_t^2(j_k) = \sigma_w^2 + \sum_{i=1}^k \sigma_x^2(j_i)$$

(2.6)

where  $\sigma_x^2(j_k)$  is the variance of execution time for module  $j_k$  and  $\sigma_w^2$  is given in Eq.(2.3). For the case of a single module invocation, there will be only a single module in the execution sequence.

# 2.2.2 Weighted Control-Flow Graph Model

To take into consideration the precedence waiting times due to the intermodule relationships as indicated in the task control-flow graph, we map the mean and variance of the module response times (computed by the module response time model) onto the control-flow graph as arc weights (Figure 2.2). The response time for module i is assigned as the weights for all arcs emerging from module i in the control-flow graph. After the execution of module i, if it enables module j which is residing on a different computer, the module enablement message is transmitted via the interconnection network. Since the network delay is independent of module response times, the mean and variance of network delay 1 can be added to the weight of the arc from module i to j. Then the task response time can be estimated from this weighted control-flow graph model.

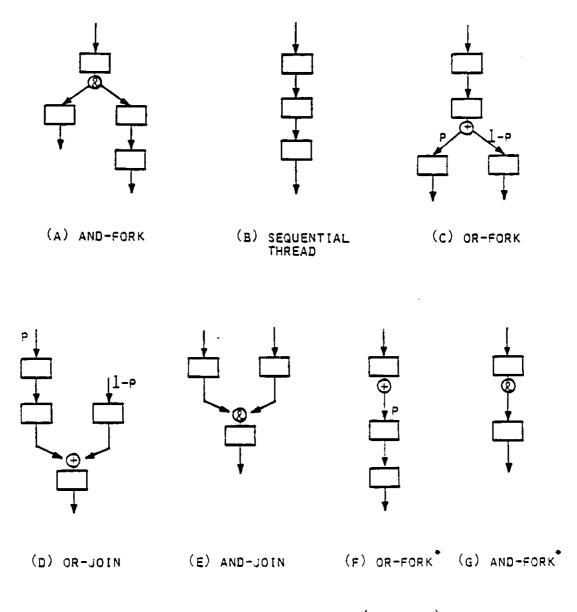

According to the logical structures and precedence relationships among software modules, there are four common types of control-flow subgraphs: sequential thread, And-Fork to And-Join, Or-Fork to Or-Join, and loop (Figures 2.3 to 2.6). A task control-flow graph may contain a combination of these basic logical relationships

<sup>&</sup>lt;sup>1</sup> Network delays among any pair of computers may be different depending upon the characteristics of the interconnection network.

$\tau_{i}$  - mean module i response time  ${\sigma_{i}}^{2}\text{-}$  variance of module i response time

Figure 2.2 Weighted Control-Flow Graph for Response Time Estimations

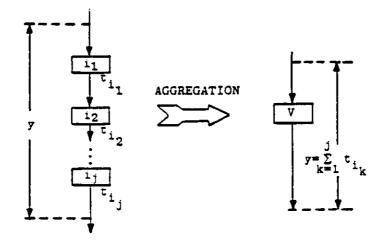

among modules. Each of these graphs can be reduced to a single node graph. Such successive graph reductions yield the estimation of the task response time.

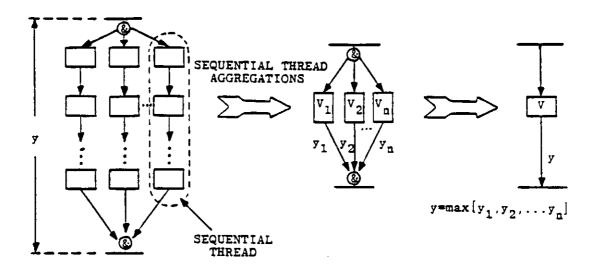

### 2.2.2.1 Sequential Thread Subgraph

Sequential thread subgraph (Figure 2.3) is a sequence of modules connected in series in which each module (except the last) has a single successor. Modules execute in the sequence indicated by the thread. Assuming that module response times represented by arc weights are random variables, then the total response time of the thread is the sum of all arc weights of each module.

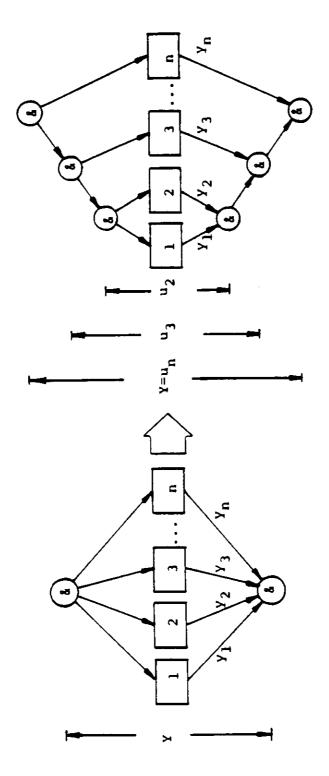

# 2.2.2.2 And-Fork to And-Join Subgraph

This subgraph begins from a module which simultaneously enables several succeeding modules (an and-fork) and ends at a module which is enabled only when all of its preceding modules have completed their executions (an and-join) as shown in Figure 2.4. This subgraph may correspond to the case in which the modules assigned to different computers require concurrent processing. Since sequential threads can be reduced to a single node as mentioned above, the and-fork to and-join subgraph can be aggregated into several nodes  $V_i$  with response time  $y_i$  for i=1,2,...n (Figure 2.4). Because of the and-join function, the response time of the subgraph is the maximum of  $y_i$ 's.

Computing the response time for this subgraph requires the knowledge of the PDF's for  $y_i$ 's, which is rather complicated. In this study, we shall emphasize mainly

t : RESPONSE TIME OF MODULE i j (RANDOM VARIABLE)

y : RESPONSE TIME FOR THE SEQUENTIAL THREAD (RANDOM VARIABLE)

Figure 2.3 Sequential Thread

Figure 2.4 And-Fork to And-Join Subgraph

the average task response time, which usually can be determined by the first two moments of module response times. Therefore, these moments are derived from the module response time model. According to the coefficients of variation of  $y_i$ 's, they can be approximated by either Erlangian or hyper-exponential distribution functions [SAUE81]. Assuming that  $y_i$ 's are independent, the joint PDF for  $y_i$ 's can be computed. Thus the mean and variance of the response time for the subgraph can be obtained (See Appendix A).

## 2.2.2.3 Or-Fork to Or-Join Subgraph

This type of the subgraph consists of an or-fork and an or-join as depicted in Figure 2.5. At the or-fork, the module enables one of its succeeding modules. This type of subgraph facilitates the system to process one out of several threads based on certain selection criteria. The branching probability to execute each thread can be measured or estimated from the IMC data. The response time for the subgraph is the sum of all these threads' response times weighted by their branching probabilities.

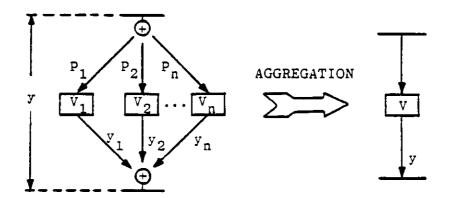

# 2.2.2.4 Loop Subgraph

Loops are often contained in a task control-flow graph for repeatedly processing a set of modules for a task invocation. A loop may contain any of the aforementioned subgraphs. After aggregating these subgraphs, a loop may be represented by a single cyclic node graph as shown in Figure 2.6. The arc weight is the response time of executing a single loop. The response time of the loop subgraph can be computed from the average number of times that the loop is executed multiplied by the time re-

$P_i$ : BRANCHING PROBABILITY (TO ENABLE MODULE  $V_i$ )

$$\sum_{i=1}^{n} P_{i} = 1$$

Figure 2.5 Or-Fork to Or-Join Subgraph

y<sub>1</sub> : RESPONSE TIME FOR A SINGLE LOOP

y: RESPONSE TIME FOR THE LOOP SUBGRAPH

Figure 2.6 Loop Subgraph

quired to execute a single loop.

# 2.2.3 Module Response Times With Dependent Module Invocations

In Section 2.2.1, module invocations are assumed to be independent and their interarrival times are Poisson distributed (assumptions 1 and 2). Thus, the logical dependency and the precedence relationships among modules are neglected when computing the module response times. The independence assumption is based on the following observations. Each computer is allocated with several modules which are enabled by modules residing on other computers. Since the operation of each computer is independent of each other, the module invocation arrival processes at each computer are random and thus can be approximated by independent Poisson processes. However, if a module is invoked by another module residing on the same computer (e.g., assigning a sequential thread to the computer), then the module invocations are dependent and non-Poisson arrivals. The error introduced in computing the mean module response times in such cases may be unacceptable. Therefore we introduce the following generalized model to compute the mean module response times for dependent module invocations.

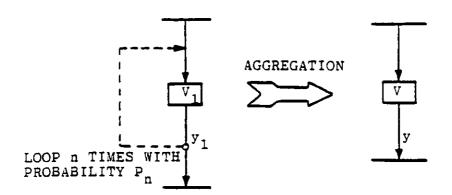

### 2.2.3.1 Partitioning the Control-Flow Subgraphs

Based on a module assignment, we partition the control-flow graph into a set of subgraphs such that the modules of each subgraph are allocated to the same computer. Each control-flow subgraph on a computer is invoked by other computers via the interconnection network. Examples of such subgraphs are shown in Figure 2.7.

Due to the relationships among modules as indicated in the subgraphs, the invocations of these modules are dependent upon each other. In addition, the dependency among the modules at the *forks* and *joins* increases the computation complexity for module response times. For tractability while considering the precedence relationships among modules, we further partition the subgraphs into several smaller ones at the forks or joins. As a result, the partitioned subgraphs become sequential threads (Figure 2.8). Figure 2.8a is a special case where two sequential threads are invoked simultaneously via bulk module invocations as they succeed an and-fork in the original control-flow subgraph. Further, if a sequential thread has an or-fork (Figure 2.8f) and the control branches to a module residing on another computer, then the execution terminates at the or-fork.

# 2.2.3.2 Mean Module Response Times for Partitioned Subgraphs

Since computing the mean module response time is simpler than computing its variance, we are able to relax assumptions 1 and 2. Let us refer to the first module of each sequential thread in a subgraph as the *entry module*, and other modules as *non-entry modules*. We assume: (1a) the invocations for the entry module(s) of each subgraph are independent of each other, (2a) the interarrival times of these invocations are exponentially distributed (i.e., Poisson arrival processes). In this case, only the invocations for the entry modules are independent and Poisson arrivals, and the invocations for non-entry modules may be dependent and non-Poisson arrivals. Thus the

\* MODULES SUCCEEDING THE OR-FORK (AND-FORK)

ARE RESIDING ON DIFFERENT COMPUTERS

Figure 2.7 Examples of Control-Flow Subgraphs that Allocated on a Computer

Figure 2.8 Partitioned Control-Flow Subgraphs of Figure 2.7

mean module response times <sup>1</sup> computed under these relaxed assumptions include such module precedence relationships as sequential threads, bulk module invocations at and-forks, and branching at or-forks.

Let us consider the response times for entry modules. Due to Poisson arrivals, the average waiting time for a given entry module is the processing time required to execute all the module invocations existing (waiting or being executed) on the computer upon the arrival of the entry module invocation. When several entry modules are invoked simultaneously, these modules are executed in a predefined sequence. Except the first module in the sequence, the mean module waiting time for a given entry module is the sum of the module bulk waiting time and the execution times of those modules processed prior to the module (Same as Eq.(2.4)).

Let us now consider the waiting times for non-entry modules. After an entry module finishes its execution, it enables its succeeding module as indicated in the subgraph. Since the invocation arrivals for the non-entry modules no longer form a Poisson arrival process, we need to keep track of the 'history' of the module executions since the arrival of that entry module invocation. During the waiting time of the entry module, new module invocations may arrive from other computers, and some of modules waiting in front of the entry module may invoke their succeeding modules. These module executions will become the waiting time for the non-entry module, which can be divided into three components, and computed as shown in the Appendix

<sup>&</sup>lt;sup>1</sup> For mathematical tractability, the variances of module response times are computed under the independent Poisson assumptions.

B. The module response times can be obtained by summing the respective waiting and execution times.

Our study reveals that for most subgraphs, the module response times based on independent and Poisson module invocation assumptions are very close to those of the dependent module invocations. The dependent module invocation approach provides more accurate module response times only when the modules assigned on a computer form a long sequential thread. This reveals that assumptions 1 and 2 are reasonable, and provide good approximations for most cases.

#### 2.3 MODEL VALIDATION

To validate the proposed task response time model, simulation experiments were performed via two simulation packages: a queueing network based simulation package PAWS [BERR82], and a simulator of the Distributed Processing Architecture Design (DPAD) System [GREE80] for real-time space defense applications. In the PAWS simulation, computers are modeled as servers, and module invocations are represented as customers which request services from the servers. The service times correspond to the module execution times. After receiving service, a customer is transferred to another server queue according to the task control-flow graph and the module assignment. A customer goes through the interconnection network if it is transferred from one server to another. The network is represented by a server which always delays each customer according to the network delay distribution function before passing the customer to its destination server. As a result, the module invoca-

tions are dependent upon each other, and their arrivals are non-Poisson distributed. Further, the queueing discipline on a computer is also used for the corresponding server queue. For an AND-FORK operation, the module invocation is split into several modules and routed to their appropriate servers. For an AND-JOIN operation, the module following the join waits until all precedent modules complete their executions. The precedence and logical relationships among modules are preserved in the simulation. Therefore, PAWS provides a flexibility for testing different types of task control-flow graphs. However, it uses idealized external inputs (e.g., Poisson task invocation arrivals) and does not include the detailed operating system overhead.

We have performed the simulation to obtain the mean PTP times for selected types of task control-flow graphs. To reach the steady state of the queueing systems, the task is invoked ten thousand times for each simulation run. In order to aviod the instability of computers due to overloading in the simulations, the maximum task invocation rate is thus chosen that utilization of each computer is less than 80%. Further, each simulation experiment is repeated five times with different initial random numbers to reduce the statistical fluctuation. Here let us consider the sample task control-flow graph in Figure 2.1a with its parameters given in Table 2.1. It consists of sequential threads, an And-Fork to And-Join, an Or-Fork to Or-Join, and a loop. These modules are assigned to three identical computers for processing, and the system has a constant network delay of 0.2 second for message exchanges among computers. Figures 2.9 to 2.12 present the mean response times for these subgraphs and the whole task for the module assignments (Table 2.2). We aggregate the response

| • . |  |  |  |

|-----|--|--|--|

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

|     |  |  |  |

| MODULES        | MEAN EXECUTION TIME (in sec) | DISTRIBUTION |

|----------------|------------------------------|--------------|

| 1, 2, 3, 4, 5  | 1                            | EXPONENTIAL  |

| 6, 7, 8, 9, 10 | 2                            | EXPONENTIAL  |

| 11,12,13,14,15 | 3                            | EXPONENTIAL  |

Table 2.1 Module Execution Times for the Sample Control-Flow (Figure 2.1a)

|           |                                                 |                       |                           |                       |                        | <del></del>                |

|-----------|-------------------------------------------------|-----------------------|---------------------------|-----------------------|------------------------|----------------------------|

| 3         | PROCESSING<br>LOAD (SEC) PER<br>TASK INVOCATION | 5.625                 | 4.625                     | 4.625                 | 5.626                  | 5.626                      |

| e ndo     | MODULES<br>ASSIGNED                             | 3, 6, 10, 14          | 4, 10, 14                 | 4, 10, 14             | 2, 7, 9,<br>10, 12, 13 | 3, 4, 5, 6<br>7, 8, 11, 12 |

| 2         | PROCESSING<br>LOAD (SEC) PER<br>TASK INVOCATION | 5.875                 | 8.875                     | 6.875                 | 5.5                    | 5.75                       |

| CPU 2     | MODULES<br>ASSIGNED                             | 2, 4, 8,<br>11, 15    | 2, 6, 8, 9,<br>11, 12, 15 | 2, 3, 8,<br>9, 11, 15 | 1, 5, 6,<br>8, 15      | 1, 2,<br>10, 15            |

| 1         | PROCESSING<br>LOAD (SEC) PER<br>TASK INVOCATION | 5.125                 | 3,125                     | 5.125                 | 5.5                    | 5.25                       |

| CPU 1     | HODULES<br>ASSIGNED                             | 1, 5, 7,<br>9, 12, 13 | 1, 3, 5,<br>7, 13         | 1, 5, 6,<br>7, 12, 13 | 3, 4,<br>11, 14        | 9, 13, 14                  |

| COMPUTERS | ASSIGNMENTS                                     | ٧                     | <b>6</b>                  | Ü                     | Q                      | ы                          |

Table 2.2 Module Assignments & Computer Processing Load for the Sample Control-Flow Graph