DATABASE MANAGEMENT ALGORITHMS FOR ADVANCED BMD APPLICATIONS

Principal Investigator: Wesley W. Chu Researchers: M. T. Lan, K. K. Leung, J. M. An

April 1985 CSD-850018

|  |  | , |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

| REPORT DOCUMENTATION                                                            | PAGE                          | READ INSTRUCTIONS BEFORE COMPLETING FORM                       |

|---------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------|

| I. REPORT NUMBER                                                                | Z. GOVT ACCESSION HO          | J. RECIPIENT'S CATALOG HUMBER                                  |

|                                                                                 |                               |                                                                |

| i. TITLE (and Subtitle)                                                         | 1                             | S. TYPE OF REPORT & PERIOD COVERED                             |

| Patabasa Magagamant Alicovithes S                                               |                               | Final Report for the period:                                   |

| Database Management Algorithms for<br>EMD Applications                          | r Advanced                    | Feb. 1, 1984 - Jan. 31, 1985                                   |

| END APPTICACIONS                                                                |                               | 6. PERFORMING ORG. REPORT NUMBER                               |

| · AUTHOR(a)                                                                     | <del></del>                   |                                                                |

| - · · ·                                                                         |                               | 8. CONTRACT OR GRANT NUMBER(4)                                 |

| W. W. Chu, M. T. Lan, K. K. Leung, J                                            | . M. An                       | DASG 60-83-C-0019                                              |

|                                                                                 |                               |                                                                |

| 3. PERFORMING ORGANIZATION NAME AND ACCRESS                                     |                               | IQ. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| University of California, Los                                                   | Angeles                       | AREA & TORK UNIT NUMBERS                                       |

| Computer Science Department                                                     |                               |                                                                |

| 405 Hilzard Ave., Los Angeles                                                   | , CA. 90024                   |                                                                |

| 1. CONTROLLING OFFICE NAME AND ADDRESS                                          |                               | 12. REPORT DATE                                                |

| Ballistic Missile Defense Advanced Center (BMDATC)                              | l Technology                  |                                                                |

| P. O. Box 1500, Huntsville, AL 35                                               | 307                           | IJ. NUMBER OF PAGES                                            |

| 14. HONITCHING AGENCY HAME & ADDRESS(If differen                                | (CU)                          | 114                                                            |

|                                                                                 | -                             |                                                                |

|                                                                                 |                               | Unclassified                                                   |

|                                                                                 |                               | 154 DECLASSIFICATION/ DOWNGRADING                              |

| 6. DISTRIBUTION STATEMENT (of this Report)                                      |                               | <u> </u>                                                       |

|                                                                                 |                               | Marie I m. d                                                   |

| Distribution limited to U. S. Government of the requests for this document must | ment Agencies oni             | y, Test and Evaluation.                                        |

| ATTN: BMDSC-AU, P. O. Box 1500, Hui                                             | ntsville, AL 358              | <del>-</del>                                                   |

| ,                                                                               | , . <u></u>                   | -·                                                             |

|                                                                                 |                               |                                                                |

| 7. CISTRIBUTION STATEMENT (of the abstract entered                              | in Block 20, if different tre | a Report)                                                      |

|                                                                                 |                               |                                                                |

|                                                                                 |                               |                                                                |

|                                                                                 |                               |                                                                |

| E. SUPPLEMENTARY NOTES                                                          |                               |                                                                |

|                                                                                 |                               |                                                                |

|                                                                                 |                               |                                                                |

|                                                                                 |                               | •                                                              |

|                                                                                 |                               |                                                                |

| 5. KEY WORDS (Continue on reverse side if necessary an                          |                               |                                                                |

| Concurrency, Database Management Algo                                           | orithm, Distribut             | ed Systems, Intermodule                                        |

| Communication (IMC), Locking, Task As<br>Fault Tolerant Locking, Resilient Com  | ssignment, Interp             | rocessor Communication (IPC),                                  |

| Control-Flow Graph, Precedence Relati                                           | ion. Module Sched             | sk kesponse model, lask                                        |

|                                                                                 | ton, module bened             | ualug,                                                         |

| 3. ASSTRACT (Continue on reverse side if necessary and                          | d leantity by block member)   |                                                                |

|                                                                                 |                               |                                                                |

|                                                                                 |                               |                                                                |

|                                                                                 |                               |                                                                |

# DATABASE MANAGEMENT ALGORITHMS FOR ADVANCED BMD APPLICATIONS

### FINAL REPORT FOR THE PERIOD

FROM: February 1, 1984

TO: January 31, 1985

Contract No. DASG 60-83-C-0019

Prepared For:

Ballistic Missile Defense Advanced Technology Center

Huntsville, Alabama 35807

April 30, 1985

University of California, Los Angeles Wesley W. Chu, Principal Investigator

Researchers: M. T. Lan, K. K. Leung, and J. M. An

The views, opinions, and/or findings contained in this report are those of the author(s) and should not be construed as an official Department of the Army position, policy or desision, unless so designated by other official documentation.

### **CONTENTS**

|      |                                                                                          | Page  |

|------|------------------------------------------------------------------------------------------|-------|

| Ī.   | INTRODUCTION AND SUMMARY                                                                 | I-1   |

| II.  | TASK RESPONSE TIME MODEL & ITS APPLICATIONS FOR REAL TIME DISTRIBUTED PROCESSING SYSTEMS | II-1  |

| III. | PRECEDENCE RELATIONS & TASK ALLOCATION FOR DISTRIBUTED REAL-TIME SYSTEMS                 | III-1 |

| IV.  | FAULT TOLERANT LOCKING FOR TIGHTLY COUPLED SYSTEMS                                       |       |

|      | ACKNOWLEDGEMENTS                                                                         |       |

|      | DISTRIBUTION LIST                                                                        |       |

### CHAPTER I

### INTRODUCTION AND SUMMARY

### I. INTRODUCTION AND SUMMARY

During the past year, we have been emphasizing our studies on distributed processing systems for the following three areas: task response time model, algorithm for task assignments for distributed real-time systems, and Fault Tolerant Locking protocol. We shall briefly summarize our findings in the following.

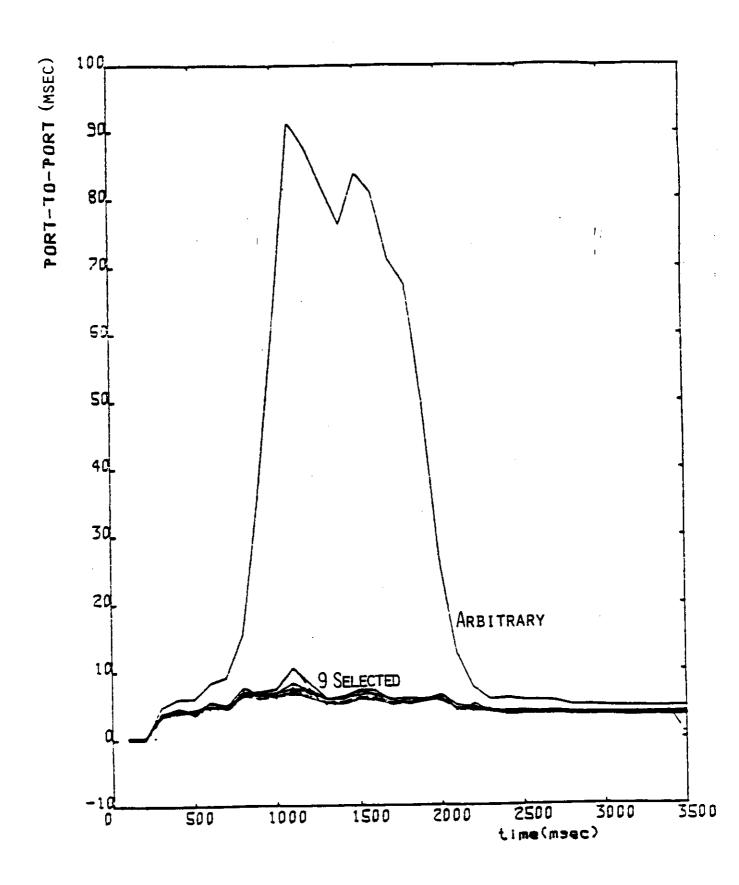

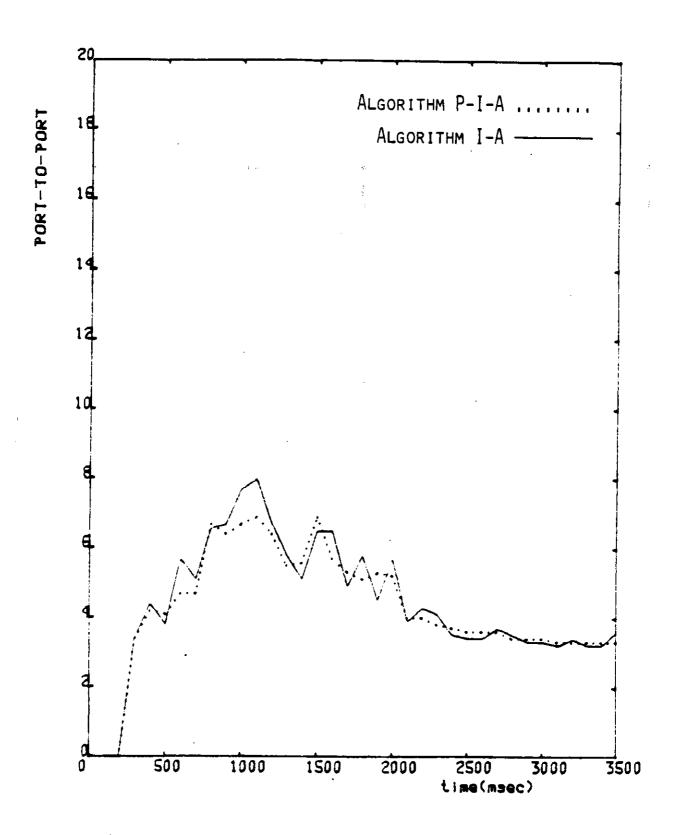

We have developed an analytical model for estimating the average response time for loosely coupled distributed systems. The model provides a good estimate of task response time as compared with simulations. For example, we are able to estimate the port-to-port time for the DPAD system and obtain results comparable to that generated by the DPAD simulator. Our analytical model not only provides us more insight, but also is far less time-consuming. The model allows us to study the performance of various scheduling algorithms, data base management algorithms, and module and file assignment. Currently, we are extending our model for the tightly coupled distributed systems.

Task assignment is one of the important problems in distributed systems. The three key parameters are: accumulative execution time (AET), interprocessor communication (IMC), and module precedence relation. During the past year, we have emphasized our investigation on the module precedence relationship area. We have performed simulation experiments as well as analytical studies and discovered that the module execution time is a key parameter in determining whether a module pair should be allocated on the same processor. In general, if a module with small execution time

precedes a module with large execution time, then they should be allocated on the same processor. Otherwise, they should be allocated on different processors. We have incorporated these rules in our allocation algorithm developed in the previous year that considers AET and IMC. We noticed that precedence relationship consideration could provide substantial response time improvements for some application tasks.

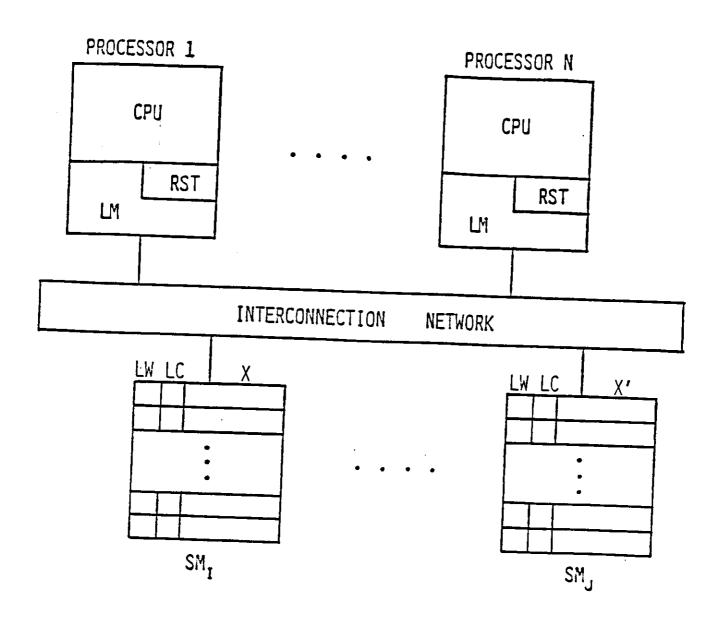

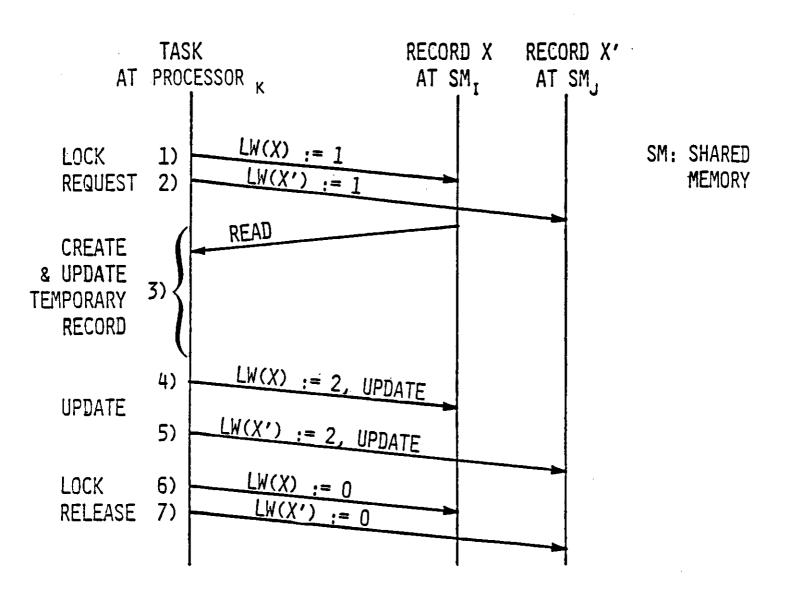

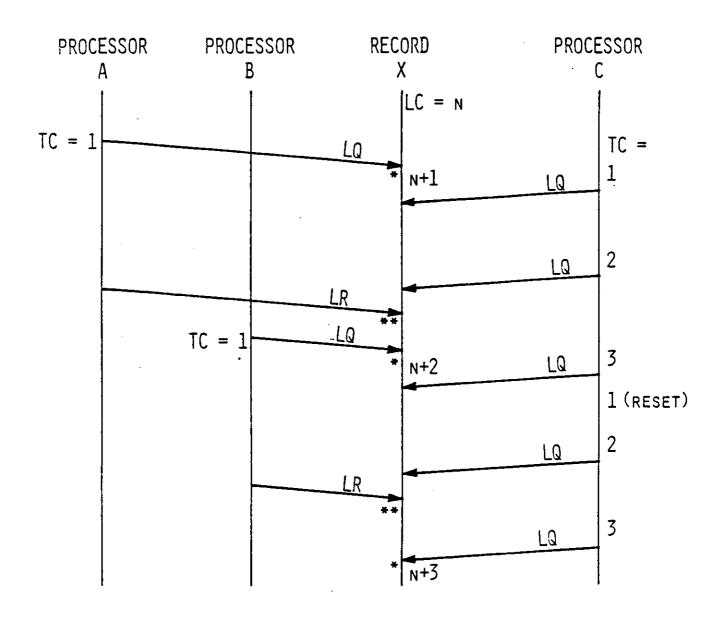

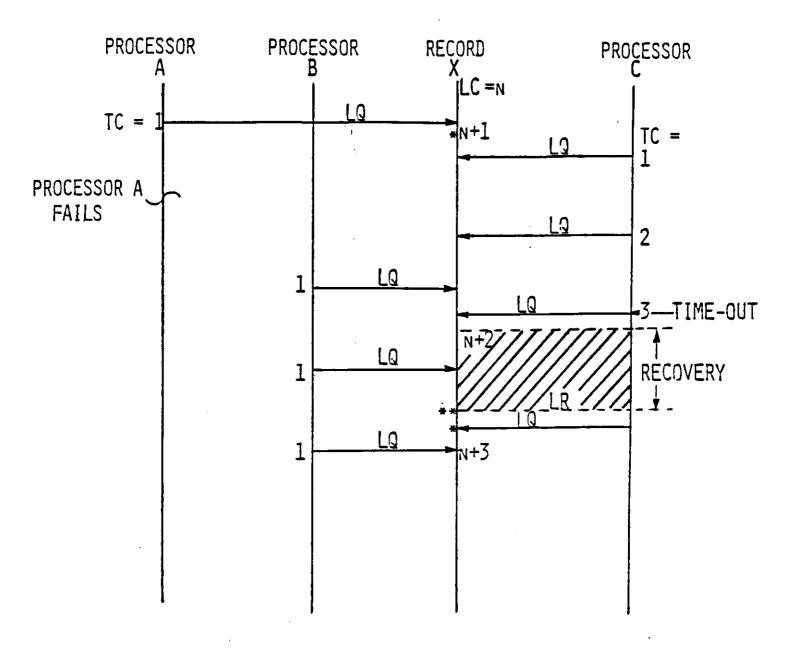

Fault tolerance is an important design issue for distributed systems. Fault Tolerant Locking (FTL) provides a resilient locking protocol for performing updates in primary and shadow file copies in a tightly coupled distributed systems. Techniques are developed to assure data consistency and recovery in cast of processor, memory, or communication path failures. FTL has been implemented on the SDC BMD testbed at Huntsville. Experimental results characterize the FTL behavior, operating overhead, and performance. The testbed results conclude that FTL is feasible (in terms of response time) for BMD applications. Currently, we are developing an analytical model for FTL to study the interrelationship of such parameters as the memory access conflict, number of lock retries (time-out), and response time. Such study should provide us with insight about selecting the parameter values for achieving optimal performance.

### CHAPTER II

TASK RESPONSE TIME MODEL & ITS APPLICATIONS

FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS

# TASK RESPONSE TIME MODEL & ITS APPLICATIONS FOR REAL-TIME DISTRIBUTED PROCESSING SYSTEMS\*

### Wesley W. Chu and Kin K. Leung

Computer Science Department University of California, Los Angeles California 90024

#### Abstract

Response time is an important system performance measure for real-time distributed processing systems. This paper introduces an analytic model to estimate the task response time for loosely coupled distributed systems. The model considers such factors as the precedence relationships among software modules, interprocessor communication, interconnection network delay, module scheduling policy, and assignment of modules to computers. Simulation experiments are used to validate the assumptions of the analytic model. Applications of the model to the study of such design issues for distributed systems as module assignment, precedence relationships, module scheduling policies, and database management algorithms are discussed.

### 1. INTRODUCTION

With the advent of low-cost VLSI and communication technologies, distributed processing (DP) has become an economically and technologically attractive computer architecture. The DP system considered in this paper consists of multiple computers, each with its own memory and peripherals, connected by an interconnection network.

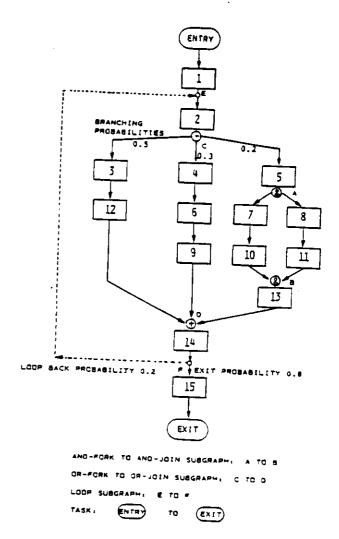

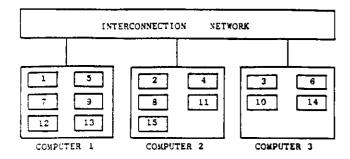

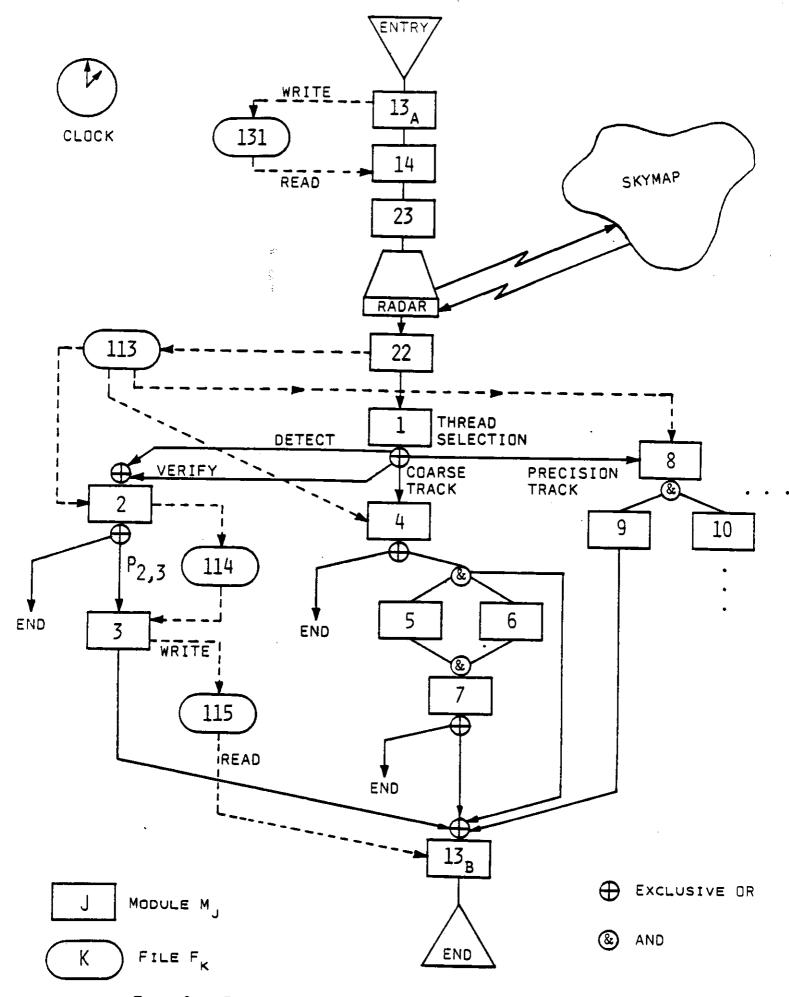

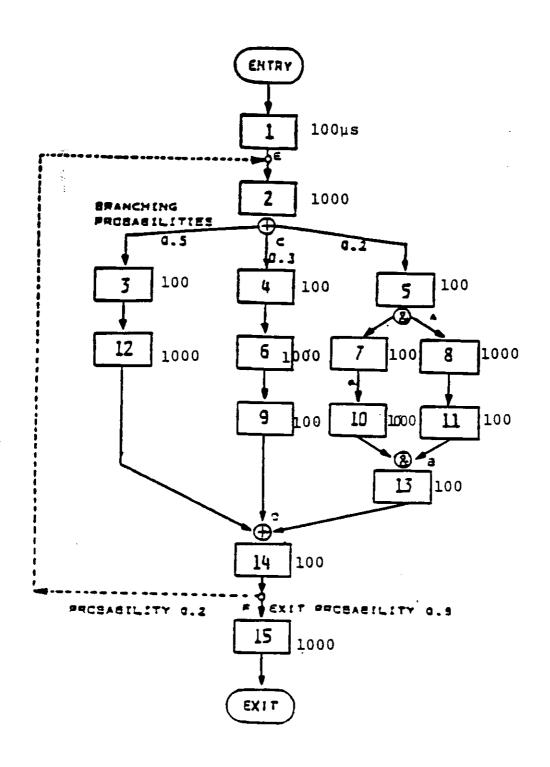

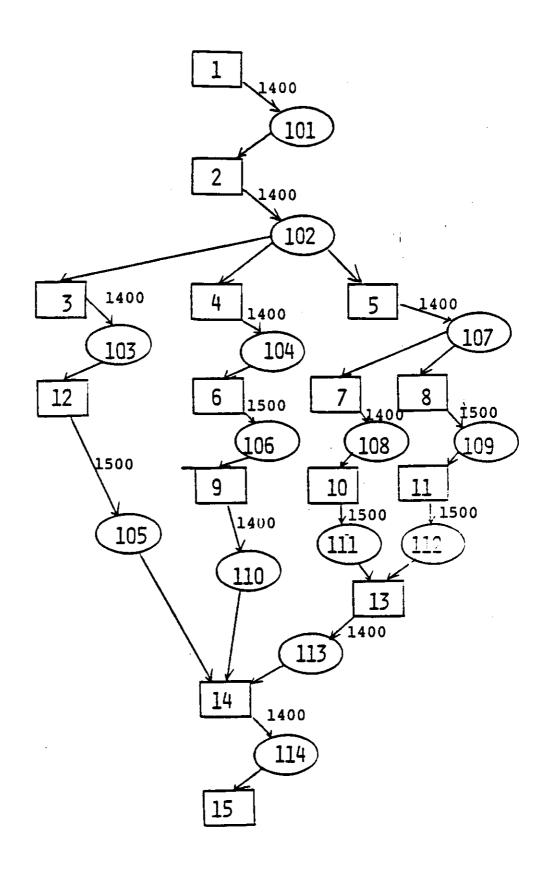

In a DP system, an application task is often partitioned into several sub-tasks (i.e., software modules) which are assigned to a set of computers for processing. An example of a task consisting of fifteen modules assigned to a system with three computers is shown in Figure 1. The logical structure and precedence relationships among the software modules may be represented by a task control-flow graph. The task is repeatedly invoked to meet the processing requirements (e.g., processing return signals from a radar). After a module completes its execution, it sends messages to enable (invoke) its succeeding module(s) as indicated in the task control-flow graph. In addition, when a

Figure 1a. A Sample Task Control-Flow Graph

module finishes its execution, it may also send messages to update the shared data files on other computers. Such message exchanges among modules are referred to as intermodule communication (IMC)<sup>1</sup>. The overhead for communications among modules that reside on the same computer is usually small and can be assumed to be negligible. If messages are sent between modules that reside on different computers, the messages are called interprocessor communication (IPC). IPC re-

This work was supported by the Ballistic Missile Defense Advanced Technological Center under Contract DASG60-83-C-0019 and the U.C. MICRO Grant P-5607-N-84.

Figure 1b. Assignment of Modules to Computers

quires such extra processing as communication protocol and management of the distributed data files, and incurs interconnection network delay. Therefore IPC has significant impact on the system performance and response time.

If data are shared among modules residing on different computers, to provide fast local accessing and to enhance file availability, some of the shared data files are replicated on several computers. However, maintaining the data consistency of the replicated copies requires the use of a concurrency control mechanism (e.g., locking, timestamp, exclusive-writer protocol). Therefore, planning a DP system is complicated by many such complex and interdependent design issues as module and file assignment2, module scheduling policy, database management algorithm, etc. Presently, there is no systematic methodology for designing DP systems. Existing system designs use ad hoc methods which result in a trial-and-error approach. Further, since DP systems often are required to perform time critical functions, response time is an important performance measure. Simulation techniques are used to estimate the response time, but such approaches are time-consuming and expensive. This motivates us to develop an analytic model for estimating the response time for DP systems. The model can be used as a unified approach for studying various DP design issues and exploring the tradeoffs among different design choices.

We shall first present our task response time model based on module response times and the weighted task control-flow graph. Next, we present a set of simulation experiments to validate the assumptions used in the model for various types of logical structures and precedence relationships among modules. Finally, we discuss the use of the model to study the interrelationships among task response time, module assignment, precedence relationships, scheduling policy for module executions, and database management algorithms.

### 2. A TASK RESPONSE TIME MODEL

Queueing networks \*- are commonly used to model DP systems. In such models, computers are represented as servers, modules as customers, and task invocations correspond to external arrivals. Customers are routed for service in accordance with the task control-flow graph and the module assignment. In DP systems, a module may enable more than one modules. This is referred to as a FORK in the graph. Alternatively, a module may have several immediate predecessor modules which must complete their executions before the succeeding module can be executed. This is referred to as a JOIN. When a control-flow graph consists of FORKs and JOINs, the routing scheme in the queueing network model is inadequate to represent the logical relationships among modules. Thus the system cannot be represented by a tractable queueing network model. Therefore, we present a new model to estimate the task response time.

Task response time, or port-to-port (PTP) time, is the time from the request of a task invocation to the completion of its execution. Since a task may be repeatedly invoked and the modules are enabled according to the sequence as indicated in the control-flow graph, task response time consists of module waiting times, module execution times and precedence waiting times. Module waiting time is the time from a module invocation arrival until it starts its execution on a computer. This waiting time is the time spent waiting for module executions and input IPC processings. Module execution time is the sum of a module's execution time and its output IPC time. Let the sum of a module's waiting time and execution time be denoted as module response time. The precedence waiting time is the intermodule synchronization delay due to the precedence relationships among modules. Our task response time model consists of two sub-models: module response time model and weighted control-flow graph model. The first sub-model computes the module response times, while the latter considers the precedence waiting times.

#### 2.1 Module Response Time Model

For a given module assignment, each computer will execute a fixed set of modules. The response time of a module is the time from its invocation to the completion of its execution. Thus module response time includes waiting (queueing) time and module execution time. If a module needs to send messages to other computers, the output IPC time is included as a part of the module execution time. Further, these IPC's are transmitted over the interconnection network, and eventually arrive at their destinations. These input IPC's on the destination computers can be viewed as a special module which also contends for processing. Based on the module assignment and IMC's among modules, IPC processing times can be obtained. Let the

module execution times be characterized by probability distribution functions (PDF's). Then each computer can be modeled as a queueing system with several modules (customers of different types) with specified service distributions. Based on the logical structures among modules and task invocation rate, the invocation rate of each module on the computer can be determined. In queueing terminology, module invocations are customer arrivals. If several modules on the same computer are invoked simultaneously, this results in a bulk module invocation.

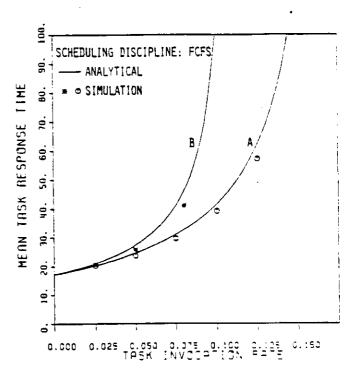

In our model, we assume that 1) the module invocation arrival (single or bulk) processes are independent of each other, and 2) module invocation interarrival times are Poisson distributed. To illustrate the concept, let us determine the modules' response times on a computer that uses first-come-first-serve (FCFS) scheduling policy\* for module executions.

Consider a computer that has n distinct module invocations (single or bulk invocations), and the arrival rate for the  $i^{th}$  module invocation be  $\lambda_i$  and the Laplace Transform (L.T.) of the service requirement be  $U_i'(s)$  for i=1,2,...n. For a bulk invocation that invokes a set M of distinct modules (referred to as module bulk), the corresponding service requirement is  $U_i'(s) = \prod_{n \in M} X_n'(s)$ , where  $X_n'(s)$  is the L.T. of the service time of module m.

Based on the assumptions 1 and 2, this queueing system is an extension of the regular FCFS M/G/1 queue with total arrival rate  $\lambda = \sum_{i=1}^{n} \lambda_i$ , and the L.T. of service time for each invocation arrival is  $U'(s) = \sum_{i=1}^{n} \frac{\lambda_i}{\lambda_i} U'_i(s)$ . For the M/G/1 queue, the first two moments of the module bulk waiting time from the bulk invocation arrival until its first module starts to execute are

$$\overline{w} = \frac{\sum_{i=1}^{n} \lambda_i \overline{u_i^2}}{2(1-\rho)} \tag{1}$$

and

$$\overline{w}^2 = 2(\overline{w})^2 + \frac{\sum_{i=1}^4 \lambda_i \overline{u_i^3}}{3(1-\rho)}$$

(2)

where:

$\overline{u_i^n} = n^{th}$  moment of service time for  $i^{th}$  module invocation,  $\rho = \text{server utilization} = \sum_{i=1}^{n} \lambda_i \overline{u_i^1},$

$\overline{w}$  = average module bulk waiting time.

From Eqs.(1) and (2), we obtained the variance of module bulk waiting time as

$$\sigma_{w}^{2} = \overline{w^{2}} - (\overline{w})^{2} = 2(\overline{w})^{2} + \frac{\sum_{i=1}^{6} \lambda_{i} \overline{u_{i}^{2}}}{3(1-\rho)} - \left\{ \frac{\sum_{i=1}^{6} \lambda_{i} \overline{u_{i}^{2}}}{2(1-\rho)} \right\}^{2}$$

(3)

In a bulk invocation, a set of modules are invoked at the same time. Based on the resource requirements, the operating system schedules the execution sequence for these modules. Let the sequence be  $j_1, j_2, ..., j_k, ..., j_m$ . The response time (a random variable) for module  $j_k$  is

$$t(j_k) = w + \sum_{i=1}^k x(j_i)$$

(4)

where:

w = module bulk waiting time, $x(j_i) = \text{execution time for module } j_i$ .

The average response time  $T(j_k)$  for module  $j_k$  can be obtained by taking the expected values of Eq.(4). We have

$$T(j_k) = \overline{w} + \sum_{i=1}^k \overline{x}(j_i)$$

(5)

Since w,  $x(j_i)$  and  $x(j_k)$  are independent random variables, the variance  $\sigma_i^2(j_k)$  of the response time for module  $j_k$  is the sum of variances of each component in Eq.(4). Hence

$$\sigma_{1}^{2}(j_{k}) = \sigma_{w}^{2} + \sum_{i=1}^{k} \sigma_{x}^{2}(j_{i})$$

(6)

where  $\sigma_{r}^{2}(j_{k})$  is the variance of execution time for module  $j_{k}$  and  $\sigma_{\tau}^{2}$  is given in Eq.(3). For the case of a single module invocation, there will be only a single module in the execution sequence.

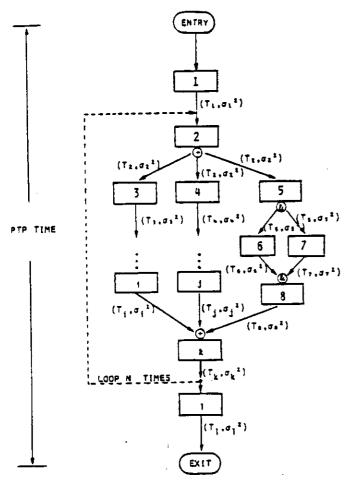

### 2.2 Weighted Control-Flow Graph Model

To take into consideration the precedence waiting times due to the intermodule relationships as indicated in the task control-flow graph, we map the mean and variance of the module response times (computed by the module response time model) onto the controlflow graph as arc weights (Figure 2). The response time for module i is assigned as the weights for all arcs emerging from module i in the control-flow graph. After the execution of module i, if it enables module j which is residing on a different computer, the module enablement message is transmitted via the interconnection network. Since the network delay is independent of module response times, the mean and variance of network delay\*\* can be added to the weight of the arc from module i to j. Then the task response time can be estimated from this weighted control-flow graph model.

<sup>\*</sup>The model can be applied to other module scheduling policies with the use of appropriate queueing delay equations.

<sup>\*\*</sup>Network delays among any pair of computers may be different depending upon the characteristics of the interconnection network.

$T_i$  - MEAN MODULE i RESPONSE TIME  $\sigma_i^2$  - VARIANCE OF MODULE i RESPONSE TIME

Figure 2. Weighted Control-Flow Graph for Response Time Estimations

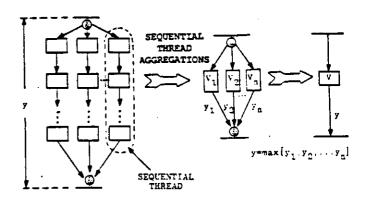

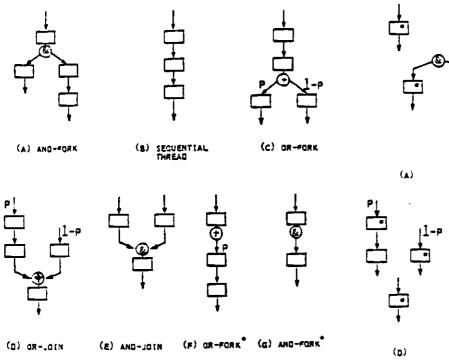

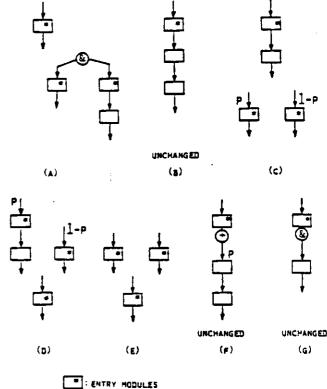

According to the logical structures and precedence relationships among software modules, there are four common types of control-flow subgraphs: sequential thread. And-Fork to And-Join, Or-Fork to Or-Join, and loop (Figures 3 to 6). A task control-flow graph may contain a combination of these basic logical relationships among modules. Each of these graphs can be reduced to a single node graph. Such successive graph reductions yield the estimation of the task response time.

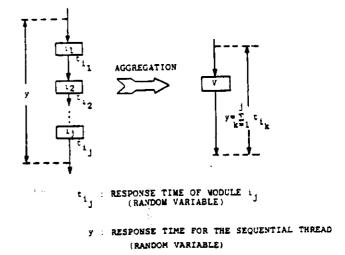

### 2.2.1 Sequential Thread Subgraph

Sequential thread subgraph (Figure 3) is a sequence of modules connected in series in which each module (except the last) has a single successor. Modules execute in the sequence indicated by the thread. Assuming that module response times represented by arc weights are random variables, then the total response time of the thread is the sum of all arc weights of each module.

Figure 3. Sequential Thread

Figure 4. And-Fork To And-Join Subgraph

### 2.2.2 And-Fork to And-Join Subgraph

This subgraph begins from a module which simultaneously enables several succeeding modules (an and-fork) and ends at a module which is enabled only when all of its preceding modules have completed their executions (an and-join) as shown in Figure 4. This subgraph may correspond to the case in which the modules assigned to different computers require concurrent processing. Since sequential threads can be reduced to a single node as mentioned above, the and-fork to and-join subgraph can be aggregated into several nodes  $V_i$  with response time  $y_i$  for i=1,2,...n (Figure 4). Because of the and-join function, the response time of the subgraph is the maximum of  $y_i$ 's.

Computing the response time for this subgraph requires the knowledge of the PDF's for y,'s, which is rather complicated. In this study, we shall emphasize mainly the average task response time, which usually can be determined by the first two moments of module response times. Therefore, these moments are derived from the module response time model. According to the coefficients of variation of y,'s, they can be approxi-

mated by either Erlangian or hyper-exponential distribution functions. Assuming that y,'s are independent, the joint PDF for y,'s can be computed. Thus the mean and variance of the response time for the subgraph can be obtained.

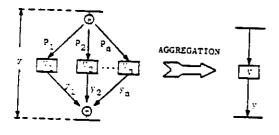

### 2.2.3 Or-Fork to Or-Join Subgraph

This type of the subgraph consists of an or-fork and an or-join as depicted in Figure 5. At the or-fork, the module enables one of its succeeding modules. This type of subgraph facilitates the system to process one out of several threads based on certain selection criteria. The branching probability to execute each thread can be measured or estimated from the IMC data. The response time for the subgraph is the weighted response times of all these threads.

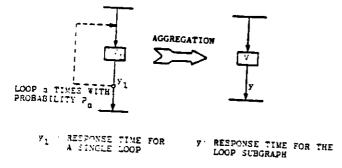

### 2.2.4 Loop Subgraph

Loops are often contained in a task control-flow graph for repeatedly processing a set of modules for a task invocation. A loop may contain any of the aforementioned subgraphs. After aggregating these subgraphs, a loop may be represented by a single cyclic node graph as shown in Figure 6. The arc weight is the response time of executing a single loop. The response time of the loop subgraph can be computed from the average number of times that the loop is executed multiplied by the time required to execute a single loop.

$P_{L}$  = SHANCHING PROBABILITY (TO ENABLE MODULE  $V_{L}$ )  $\frac{\pi}{2} = P_{L} = L$

Figure 5. Or-Fork To Or-Join Subgraph

Figure 6. Loop Subgraph

### 2.3 Module Response Times With Dependent Module Invocations

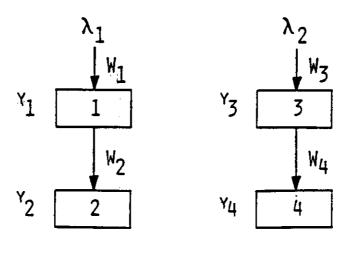

In Section 2.1, module invocations are assumed to be independent and their interarrival times are Poisson distributed (assumptions I and 2). Thus, the logical dependency and the precedence relationships among modules are neglected when computing the module response times. The independence assumption is based on the following observations. Each computer is allocated with several modules which are enabled by modules residing on other computers. Since the operation of each computer is independent of each other, the module invocation arrival processes at each computer are random and thus can be approximated by independent Poisson processes. However, if a module is invoked by another module residing on the same computer (e.g., assigning a sequential thread to the computer), then the module invocations are dependent and non-Poisson arrivals. The error introduced in computing the mean module response times in such cases may be unacceptable. Therefore we introduce the following generalized model to compute the mean module response times for dependent module invocations.

### 2.3.1 Partitioning the Control-Flow Subgraphs

Based on a module assignment, we partition the control-flow graph into a set of subgraphs such that the modules of each subgraph are allocated to the same computer. Each control-flow subgraph on a computer is invoked by other computers via the interconnection network. Examples of such subgraphs are shown in Figure 7. Due to the relationships among modules as indicated in the subgraphs, the invocations of these modules are dependent upon each other. In addition, the dependency among the modules at the forks and joins increases the computation complexity for module response times. For tractability while considering the precedence relationships among modules, we further partition the subgraphs into several smaller ones at the forks or joins. As a result, the partitioned subgraphs become sequential threads (Figure 8). Figure 8a is a special case where two sequential threads are invoked simultaneously via bulk module invocations as they succeed an and-fork in the original control-flow subgraph. Further, if a sequential thread has an or-fork (Figure 8f) and the control branches to a module residing on another computer, then the execution terminates at the or-fork.

# 2.3.2 Mean Module Response Times for Partitioned Subgraphs

Since computing the mean module response time is simpler than computing its variance, we are able to relax assumptions I and 2. Let us refer to the first module of each sequential thread in a subgraph as the entry module, and other modules as non-entry modules. We assume: 1a) the invocations for the entry module(s)

MODULES SUCCEEDING THE OR-FORK (AND-FORK)

ARE RESIDING ON DIFFERENT COMPUTERS

Figure 7. Examples of Control-Flow Subgraphs that Allocated on a Computer

of each subgraph are independent of each other, 2a) the interarrival times of these invocations are exponentially distributed (i.e., Poisson arrival processes). In this case, only the invocations for the entry modules are independent and Poisson arrivals, and the invocations for non-entry modules may be dependent and non-Poisson arrivals. Thus the mean module response times computed under these relaxed assumptions include such module precedence relationships as sequential threads, bulk module invocations at and-forks, and branching at or-forks.

Let us consider the response times for entry modules. Due to Poisson arrivals, the average waiting time for a given entry module is the processing time required to execute all the module invocations existing (waiting or being executed) on the computer upon the arrival of the entry module invocation. When several entry modules are invoked simultaneously, these modules are executed in a predefined sequence. Except the first module in the sequence, the mean module waiting time for a given entry module is the sum of the module bulk waiting time and the execution times of those modules processed prior to the module (Same as Eq.(4)).

Figure 8. Partitioned Control-Flow Subgraphs of Figure 7

. Let us now consider the waiting times for nonentry modules. After an entry module finishes its execution, it enables its succeeding module as indicated in the subgraph. Since the invocation arrivals for the non-entry modules no longer form a Poisson arrival process, we need to keep track of the 'history' of the module executions since the arrival of that entry module invocation. During the waiting time of the entry module, new module invocations may arrive from other computers, and some of modules waiting in front of the entry module may invoke their succeeding modules. These module executions will become the waiting time for the non-entry module, which can be divided into three components, and computed as shown in the Appendix. The module response times can be obtained by summing the respective waiting and execution times.

Our study reveals that for most subgraphs, the module response times based on independent and Poisson module invocation assumptions are very close to those of the dependent module invocations. The dependent module invocation approach provides more accurate module response times only when the modules assigned on a computer form a long sequential thread. This reveals that assumptions 1 and 2 are reasonable, and provide good approximations for most cases.

<sup>\*</sup>For mathematical tractability, the variances of module response times are computed under the independent Poisson assumptions.

### 3. MODEL VALIDATION

To validate the proposed task response time model, simulation experiments were performed via two simulation packages: a queueing network based simulation package PAWS 7, and a simulator of the Distributed Processing Architecture Design (DPAD) System \* for real time space defense applications. In the PAWS simulation, computers are modeled as servers, and module invocations are represented as customers which request services from the servers. The service times correspond to the module execution times. After receiving service, a customer is transferred to another server queue according to the task control-flow graph and the module assignment. A customer goes through the interconnection network if it is transferred from one server to another. The network is represented by a server which always delays each customer according to the network delay distribution function before passing the customer to its destination server. As a result, the module invocations are dependent upon each other, and their arrivals are non-Poisson distributed. Further, the queueing discipline on a computer is also used for the corresponding server queue. For an AND-FORK operation, the module invocation is split into several modules and routed to their appropriate servers. For an AND-JOIN operation, the module following the join waits until all precedent modules complete their executions. The precedence and logical relationships among modules are preserved in the simulation. Therefore, PAWS provides a flexibility for testing different types of task control-flow graphs. However, it uses idealized external inputs (e.g., Poisson task invocation arrivals) and does not include the detailed operating system overhead.

We have performed the simulation to obtain the mean PTP times for selected types of task control-flow graphs. To reach the steady state of the queueing systems, the task is invoked ten thousand times for each simulation run. Further, each simulation experiment is repeated five times with different initial random numbers to reduce the statistical fluctuation. In this paper, let us consider the sample task control-flow

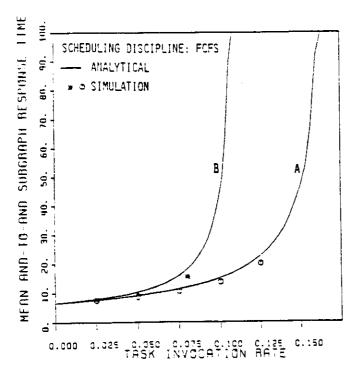

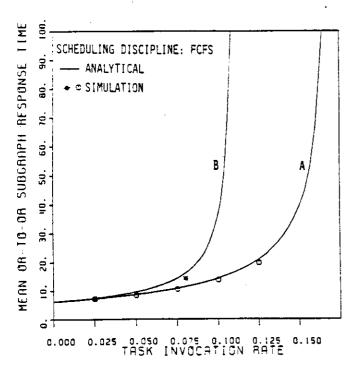

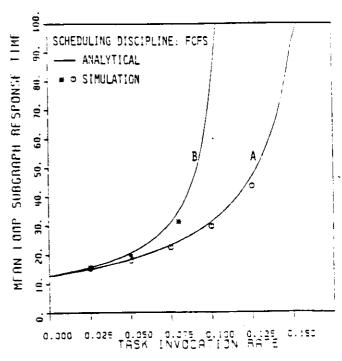

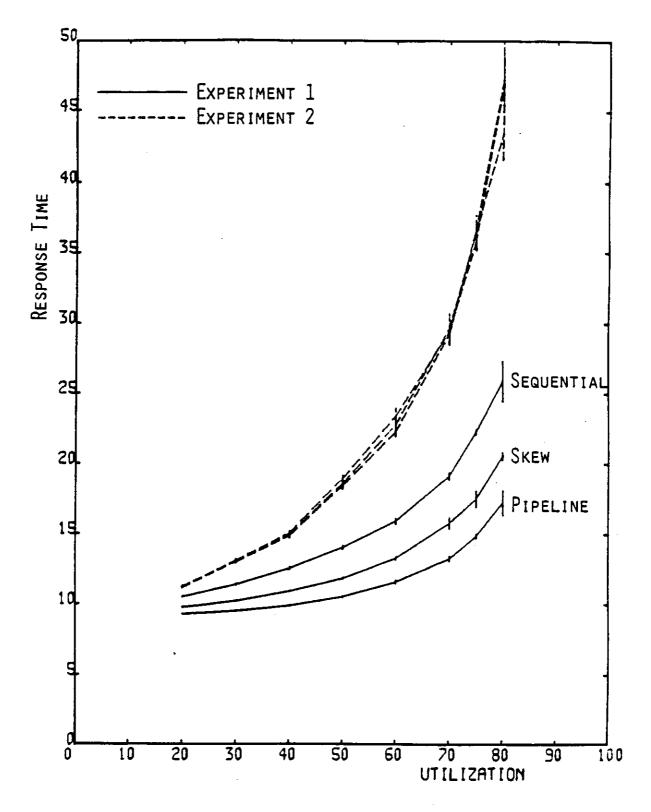

graph in Figure 1a with its parameters given in Table 1. It consists of sequential threads, an And-Fork to And-Join, an Or-Fork to Or-Join, and a loop. These modules are assigned to three identical computers for processing, and the system has a constant network delay of 0.2 second for message exchanges among computers. Figures 9 to 12 present the mean response times for these subgraphs and the whole task for the module assignments (Table 2). We aggregate the response times of sequential threads, the and-fork to and-join, the or-fork to or-join, and the loop, and finally obtain the PTP time for the entire graph. Besides this control-flow graph, we have also studied the performance of the analytical model for various types of control-flow structures. The fact that mean response times from the analytical model compare closely with that of simulations reveals that the assumptions used in the analytical model (independent and Poisson module invocation arrivals) are good approximations for response time estimations.

The PAWS simulation is very time-consuming. Depending on task invocation rates and control-flow graphs, each simulation point requires five to eight hours of VAX-11/780 processing time. While for the analytical model, the response time computation for a given module assignment under various loading environments requires less that one minute of CPU time. This represents a reduction of three orders of magnitude in computation time!

| MODULES        | MEAN EXECUTION TIME | EXECUTION TIME<br>DISTRIBUTION |

|----------------|---------------------|--------------------------------|

| 1, 2, 3, 4, 5  | 1                   | EXPONENTIAL                    |

| 6, 7, 8, 9, 10 | 2                   | EXPONENTIAL                    |

| 11,12,13,14,15 | 3                   | EXPONENTIAL                    |

Table 1. Module Execution Times for the Sample Control-Flow Graph (Figure 1a)

| COMPUTERS   | CF                    | CPU 1                                           |                           | CPU 2                                           |                     | CPU 1                                     |  |

|-------------|-----------------------|-------------------------------------------------|---------------------------|-------------------------------------------------|---------------------|-------------------------------------------|--|

| ASSIGNMENTS | HODULES<br>ASSIGNED   | PROCESSING<br>LOAD (SEC) PER<br>TASK INVOCATION | MODULES<br>ASSIGNED       | PROCESSING<br>LOAD (SEC) PER<br>TASK INVOCATION | MODULES<br>ASSIGNED | PROCESSING LUAD (SEC) PER TASK INVOCATION |  |

| A           | 1, 5, 7,<br>9, 12, 13 | 5.125                                           | 2, 4, 8,<br>11, 15        | 5.875                                           | 3, 6, 10, 14        |                                           |  |

| В           | 1, 3, 5,<br>7, 13     | 3.125                                           | 2, 6, 8, 9,<br>11, 12, 15 | 8.875                                           | 4, 10, 14           | 4.625                                     |  |

Table 2. Module Assignments & Computer Processing Load for the Sample Control-Flow Graph

Figure 9. Mean Response Time for the And-Fork to

And-Join Subgraph of the Sample

Control-Flow Graph (Figure 1a)

Figure 10. Mean Response Time for the Or-Fork to Or-Join Subgraph of the Sample Control-Flow Graph

Figure 11. Mean Response Time for the Loop Subgraph of the Sample Control-Flow Graph

Figure 12. Mean Task Response Time for the Sample Control-Flow Graph

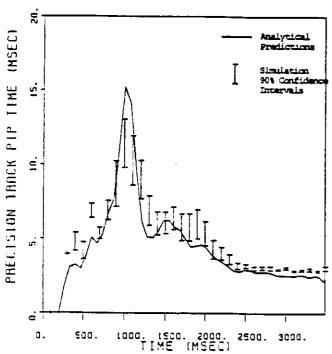

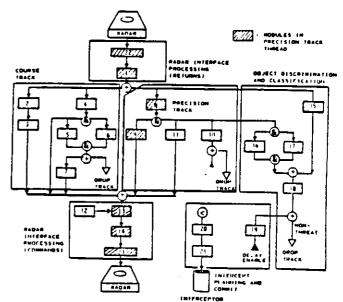

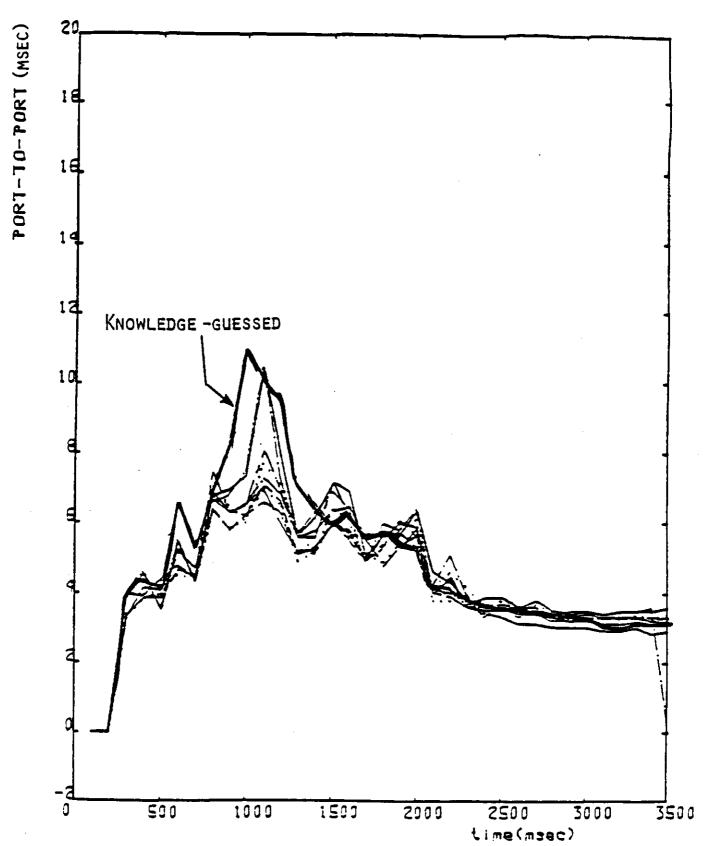

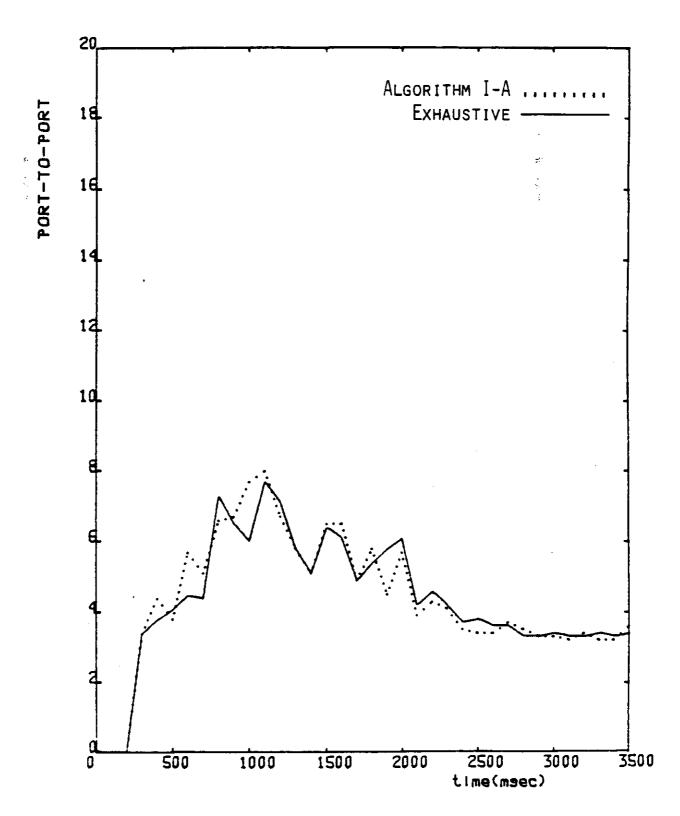

We now describe the model validation via the DPAD simulator\*. The DPAD system is a real time DP system which processes radar return signals for space defense applications. The DPAD simulator provides detailed operating system operations for module scheduling and IPC message exchanges among computers. Further, non-Poisson task invocation arrivals are used. Its task control-flow graph is shown in Figure 13. The module assignment and module priorities are shown in Table 3. The processing thread for precision track function is indicated by shaded modules in Figure 13. For input data to the analytical model, we collected the IMC data, module execution times (Table 4) and invocation rates in every 100-msec time interval from the DPAD simulator. Since the DPAD System uses a priority module scheduling policy rather than FCFS, queueing formulas were derived to compute the module response times for this scheduling discipline. The PTP time was generated for each of these time intervals. To obtain the 90% confidence intervals for the task response time, the simulation was repeated five times. From Figure 14, we note that the PTP time predictions are close to the simulation measurements. This indicates that the model also provides a good response time estimation for non-Poisson task invocation arrivals with priority module scheduling policy and IPC overhead.

Figure 14. Comparing Analytical Predictions with the DPAD Simulation

Figure 13. The Task Control-Flow Graph for the DPAD System

| COMPUTERS | NODULE ASSIGNMENT                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU 1     | $\mathbf{M}_{1}(1), \ \mathbf{M}_{2}(1), \ \mathbf{M}_{4}(1), \ \mathbf{M}_{6}(1), \\ \mathbf{M}_{8}(1), \ \mathbf{M}_{10}(1), \ \mathbf{M}_{16}(1), \ \mathbf{M}_{22}(4)$   |

| CPU 2     | $\mathbf{M}_{3}(1), \ \mathbf{M}_{5}(1), \ \mathbf{M}_{9}(1), \ \mathbf{M}_{17}(1), \\ \mathbf{M}_{18}(1), \ \mathbf{M}_{19}(5), \ \mathbf{M}_{20}(6), \ \mathbf{M}_{21}(6)$ |

| СРИ З     | $\mathbf{M}_{7}(1), \ \mathbf{M}_{11}(1), \ \mathbf{M}_{12}(1), \ \mathbf{M}_{13}(3), \\ \mathbf{M}_{14}(2), \ \mathbf{M}_{15}(1), \ \mathbf{M}_{23}(4)$                     |

$M_{\chi}(i)$ : Module x with priority 1.  $M_{\chi}(i)$  has higher priority than  $M_{\chi}(j)$  if i > j.

Table 3. A Module Assignment for the DPAD System

| MODULES          | HEAN EXECUTION<br>TIME 'BALL                             | CORF. OF<br>VARIATION                                    |

|------------------|----------------------------------------------------------|----------------------------------------------------------|

| 2<br>3<br>4<br>5 | 0.157043<br>0.213522<br>0.297477<br>0.422061<br>0.179127 | 0.300161<br>0.223414<br>0.300066<br>0.385611<br>0.300042 |

| 6<br>7<br>8<br>9 | 0.321826<br>0.325322<br>1.228163<br>0.659989<br>0.535785 | 9.252115<br>9.178972<br>0.307536<br>9.300000<br>0.000226 |

| 11               | 0.300000                                                 | 0.000000                                                 |

| 12               | 0.300000                                                 | 0.30000                                                  |

| 13               | 0.314381                                                 | 0.302388                                                 |

| 14               | 0.131386                                                 | 0.303647                                                 |

| 25               | 0.300000                                                 | 0.300000                                                 |

| 16               | 0.717703                                                 | 0.300090                                                 |

| 17               | 1.317310                                                 | 0.300003                                                 |

| 18               | 0.656889                                                 | 0.302284                                                 |

| 19               | 3.339637                                                 | 0.300003                                                 |

| 20               | 6.695341                                                 | 9.000012                                                 |

| 21               | g.730000                                                 | 0.300000                                                 |

| 22               | g.380173                                                 | 0.317631                                                 |

| 23               | g.162149                                                 | 0.305163                                                 |

Table 4. Module Execution Times (Including Output IPC) for the DPAD System Averaged over 35 100-msec Time Intervals

The DPAD simulator was originally developed at TRW and subsequently enhanced at UCLA to include facilities for measuring IMC data, module execution time and invocation statistics.

### 4. MODEL APPLICATIONS

The proposed model can be used to study the effect on response time of such design issues as module assignment and precedence relationships, module scheduling disciplines and database management algorithms. With the response time as a performance measure, the model can be used to study the tradeoffs among various design choices and to provide us insight into planning and evaluating distributed systems.

### 4.1 Module Assignment and Precedence Relationships

The assignment of modules to computers is an important problem in DP system design. Module assignment affects the response time, throughput, and system reliability. The factors that affect the module assignments are: a) computer processing capacities and their utilization factors, b) IMC among modules, and c) logical and precedence relationships among modules. Several approaches to the assignment problem in distributed systems have been proposed 9-12. However, each of these approaches has its shortcomings such as neglecting queueing effect and precedence relationships. Therefore, the 'optimal' module assignments generated by them do not provide low response times on the actual systems. Our proposed model takes both computer load and precedence relationships into consideration. For a given module assignment, a module scheduling policy and a data management algorithm, the task response time can be estimated from the proposed model. The proposed model can be used to investigate the performance in terms of task response time of module assignment strategies with various module precedence relationships at different operating environments. This study provides insight into the interrelationship among precedence relationships, module assignment and task response time.

### 4.2 Module Scheduling Disciplines

For a given module assignment, the scheduling policy for module execution affects the response time. For example, to reduce operating system overhead, invocations for the same module may be delayed until a predefined number of module invocations have arrived and are executed in a batch manner. To avoid excessive waiting, a time-out mechanism may be used in conjunction with this scheduling policy. The proposed model can be employed to study the relationships among time-out constant, batch size, operating system overhead and the PTP time for this scheduling algorithm. Further, it can investigate the optimal assignment of module priorities for head-of-line priority scheduling policy and the relationships among scheduling policy, module assignment and the PTP time.

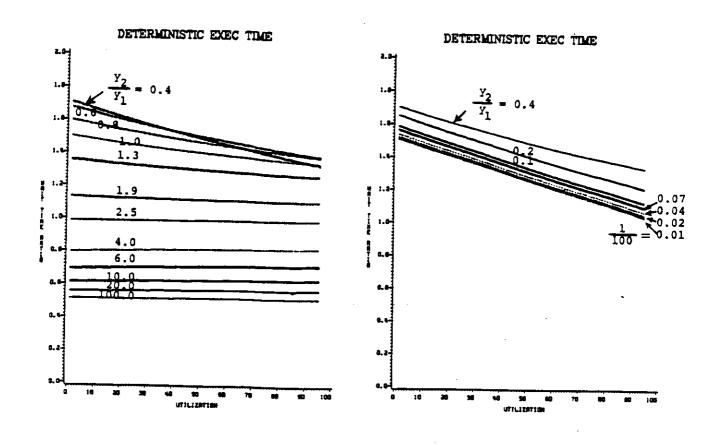

### 4.3 Database Management Strategies

Distributed systems require protocols to ensure internal and mutual data consistency for simultaneous access of replicated data files. These protocols require extra IPC, processing, and increase module response delays. Commonly used techniques for consistency controls are locking, timestamp, and exclusive-writer protocol 13.14. In the proposed model, the effect of IPC can be included as a special module execution. If the module execution has to be delayed for handling the data consistency problem, the module execution time is correspondingly prolonged. Thus the model can be used to study the overhead in terms of PTP time of several commonly used database concurrency control algorithms such as locking, timestamping, and the exclusive-writer protocol. The results of these investigations should provide insight into the performance as well as overhead of concurrency control algorithms for distributed systems at various operating environments.

#### 5. CONCLUSIONS

A new task response time model is presented for estimating the PTP time for distributed processing systems. The model maps the module response times into the task control-flow graph as arc weights and estimates the PTP time from the weighted task controlflow graph model. Since this approach considers the queueing effects, the interconnection network delays, and the logical relationships among modules, the model provides accurate PTP time prediction. Simulation experiments reveal that the proposed model provides fairly accurate PTP time. The model can be used to study module assignment problem and the effect of precedence relationships among modules on the PTP time. In addition, it can be used to study other design issues such as module scheduling policy, database management algorithm, etc. Thus this model serves as a valuable tool for the systematic planning and designing of distributed processing systems.

### Acknowledgement

The authors wish to thank Min-Tsung Lan of UCLA and Joseph Hellerstein of IBM Thomas J. Watson Research Center (formerly of UCLA) for their effort in collecting various statistics for our DPAD model validation.

#### REFERENCES

[1] W.W. Chu. M.T. Lan and J. Hellerstein, "Estimation of Intermodule Communication (IMC) and Its Applications in Distributed Processing Systems," *IEEE Trans. on Computers*, Vol.C-33, No.8, Aug. 1984, pp.691-699.

- [2] W.W. Chu, L. Holloway, M.T. Lan and Kemal Efe, "Task Allocation in Distributed Processing," IEEE Computer, Nov. 1980, pp. 57-69.

- [3] F. Basket, K.M. Candy, R. Muntz, and F. G. Palacios. "Open, Closed, and Mixed Networks of Queues with Different Classes of Customers," Journal of the ACM. Vol. 22, No. 2, April 1975, pp. 248-260.

- [4] P. Heidelberger, and K.S. Trivedi, "Queueing Network Models for Parallel Processing with Asynchronous Tasks," IEEE Trans. son Computers, Nov. 1982, pp. 1099-1109.

- [5] E.D. Lazowska, J. Zahorjan, G.S. Graham & K.C. Sevcik, Quantitative System Performance: Computer System Analysis Using Queueing Network Models, Prentice-Hall, New Jersey (1984).

- [6] C.H. Sauer and K.M. Chandy, Computer Systems Performance Modeling, Prentice-Hall, New Jersey (1981).

- [7] R. Berry, K.M. Chandy, J. Misra, and D. Neuse, PAWS 2.0 Performance Analyst's Workbench System: User Manual, Information Research Associates, Austin, Texas, Dec. 1982.

- [8] M.L. Green, E.Y.S. Lee, S. Majumdar, and D.C. Shannon, "Phase III of Distributed Processing Architecture Design (DPAD) Program -- The DDP Underlay Simulation Experiment: Tactical Applications and d-RTOS Models," Special Report 35010-79-A005, TRW Defense and Space Systems Group, May 15, 1980.

- [9] H.S. Stone, "Multiprocessor Scheduling with the Aid of Network Flow Algorithms," IEEE Trans. on Software Eng., Vol.SE-3, No.1, Jan. 1977, pp.85-93.

- [10] G.S. Rao, H.S. Stone and T.C. Hu, "Assignment of Tasks in a Distributed Processor System with Limited Memory," *IEEE Trans. on Computers*, Vol.C-28, No.4, April 1979, pp.291-299.

- [11] P.Y.R. Ma, E.Y.S. Lee and M. Tsuchiya, "A Task Allocation Model for Distributed Computing System." IEEE Trans. on Computers, Vol.C-31, No.1, Jan. 1982, pp.41-47.

- [12] T.C.K. Chou and J.A. Abraham, "Load Balancing in Distributed Systems," *IEEE Trans. on* Software Eng., Vol.SE-8, No.8, July 1982, pp.401-412.

- [13] P.A. Bernstein and N. Goodman, "Concurrency Control in Distributed Database Systems," Computing Surveys 13, 2, June 1981, pp. 185-221.

- [14] W.W. Chu and J. Hellerstein, "The Exclusive-Writer Approach to Updating Replicated Files in Distributed Processing Systems," to appear in *IEEE Trans. on Computer*, 1985.

[15] J.D.C. Little, "A Proof of the Queueing Formula  $L = \lambda W$ ," Operations Research, 9, pp.383-387(1961).

### Appendix

# Computation of Mean Module Response Times with Dependent Invocations

Consider a computer allocated with modules of v distinct control-flow subgraphs. Each subgraph consists of one or more sequential threads which may be invoked simultaneously (See Figure 8a). Assume that the  $i^{th}$  subgraph consists of  $b_i$  sequential threads, and the  $j^{th}$  sequential thread comprises  $d_i(j)$  modules for  $j=1,2,...b_i$ . For a subgraph consists of a single sequential thread, then  $b_i = 1$ . Let  $M_i(j;k)$  be the  $k^{th}$  module (starting from the entry module) of the jth sequential thread for the  $i^{th}$  subgraph. In addition, let  $P_i(j;k,t)$  be the probability of invoking  $M_i(j;t)$  given that  $M_i(j;k)$  is executed for  $i=1,2,...v, j=1,2,...b_i$  and  $1 \le k \le t \le d_i(j)$ . Thus if a subgraph does not contain any or-fork,  $P_i(j;k,t) = 1$ for all k and i. For a subgraph containing a branch of an or-fork, the modules in this branch are not invoked if the control branches to the modules that do not reside on the same computer. Thus we have,

$$P_{i}\left(j;k,k\right)=1\tag{A.1}$$

and

$$P_i(j;k,k+a) = \prod_{l=k}^{k+a-1} P_i(j;l,l+1)$$

(A.2)

for  $1 \le k \le k + a \le d_i(j)$ .

### Mean Waiting Time for Entry Modules

Let  $W_i(j;k)$  be the mean waiting time for module  $M_i(j;k)$ . According to the assumptions 1a and 2a, the mean waiting time for  $M_i(1;1)$  (i.e., an entry module) for all i=1,2,...v under the first-come-first-serve discipline is the average time to complete the current module execution and all the modules in the job queue on the computer when the invocation for  $M_i(1;1)$  arrives. Thus we have

$W_{i}(1;1) = W_{s} + \sum_{t=1}^{s} \sum_{s=1}^{b_{s}} \sum_{s=1}^{d_{s}(s)} \overline{\pi}_{i}(s;t) \overline{z}_{i}(s;t)$ (A.3)

where:

$\overline{n}$ , (s:t) = average number of invocations for M, (s:t) waiting in the job queue,

$\tilde{z}_{i}(s;t) = \text{average execution time for } M_{i}(s;t)$

$W_{s} = \text{mean residual module execution time}$   $= \sum_{t=1}^{r} \sum_{s=1}^{t_{r}} \sum_{t=1}^{t_{s}(s)} \frac{1}{2} \lambda_{r}(s;t) \overrightarrow{\mathcal{F}}_{r}(s;t),$

$\overrightarrow{F}_{r}(s;t) = \text{ second moment of execution time for } M_{r}(s;t),$

$\lambda_r(s;t) = \text{invocation rate for } M_r(s;t).$

Based on Little's result<sup>18</sup> (i.e.,  $\overline{n}$ ,  $(s:t) = \lambda$ , (s:t) W, (s:t)) and substituting the computer utilization of M, (s:t),  $\rho$ ,  $(s:t) = \lambda$ , (s:t)  $\overline{x}$ , (s:t), into Eq.(A.3), we have

$$W_{i}(1;1) = W_{i} + \sum_{r=1}^{q} \sum_{t=1}^{t_{r}} \sum_{t=1}^{d_{i}(s)} \rho_{i}(s;t) W_{i}(s;t)$$

(A.4)

For simplicity in notation, we can order the thread index j such that the execution sequence for the bulk module invocations is to execute module  $M_i(j;1)$  before module  $M_i(j;1)$  for j < s. Thus the mean waiting time  $W_i(j;1)$  is

$$W_{i}(j;1) = W_{i}(1;1) + \sum_{i=1}^{j-1} \vec{z}_{i}(s;1)$$

(A.5)

for i=1,2,...v, and  $b_i \geq j \geq 2$ .

### Mean Waiting Time for Non-Entry Modules

Let us consider the waiting time for the nonentry modules  $M_i(j;k)$  (i.e., with  $k\geq 2$ ). After completing its execution, a module invokes its succeeding module, if any, and places the invocation at the end of the job queue. Since these invocation arrivals are dependent and non-Poisson distributed, we need to keep track of the invocations generated from the modules residing on the local computer as well as the newly arrived module invocation from other computers. The waiting time for the non-entry modules can be divided into three components. The first component, W1, (j:k), is due to the executions of the succeeding modules invoked by the module invocations which are being executed or waiting in the job queue upon the arrival of the invocation for  $M_i(j;1)$ . The second component,  $W2_i(j;k)$ , is due to the waiting for the module executions invoked by the bulk module invocations (i.e.,  $M_i(s;1)$ ,  $s=1, \dots b_i$  and  $i \neq j$ . The last component, W3, (j:k), is the waiting time due to the module invocations from other computers that arrive after the invocation for the entry module and their succeeding modules. Thus,

$$W1_{r}(j;k) = \sum_{r=1}^{r} \sum_{k=1}^{k_{r}} \sum_{s=1}^{k_{r}(s)-k+1} \overline{n}_{r}(s;t) P_{r}(s;t,t+k-1) \overline{z}_{r}(s;t+k-1)$$

$$+\sum_{r=1}^{\tau}\sum_{s=1}^{t_r}\sum_{t=1}^{t_r(s)-k+1}\rho_r(s;t)P_r(s;t,t+k-1)\overline{x}_r(s;t+k-1) \qquad (A.6)$$

The first term of Eq.(A.6) is the total time for executing the succeeding modules invoked by  $M_r$  (s:t) waiting in the job queue upon the arrival of the invocation for  $M_r$  (j:1). Similarly, the second term is the execution times of the modules succeeding the module  $M_r$  (s:t) which has probability  $\rho_r$  (s:t) of being executed when the invocation for  $M_r$  (j:1) arrives.

According to the definition of invocation probability  $P_r(s;t,t+k-1)$ ,

$$\lambda_r(s;t+k-1) = \lambda_r(s;t) P_r(s;t,t+k-1)$$

(A.7)

Applying Little's result and substituting Eq.(A.7) and  $\rho_{+}(s;t) = \lambda_{+}(s;t) \overline{z}_{+}(s;t)$  into Eq.(A.6), after some algebraic manipulation, it yields

$$W1, (j;k) = \sum_{r=1}^{n} \sum_{s=1}^{k_r} \sum_{s=1}^{d_j(s)\cdot k+1} \rho_r(s;t+k-1)[W_r(s;t)+\overline{x}_r(s;t)] \quad (A.8)$$

The second component of  $W_i(j;k)$  is

$$W2, \{j;k\} = \sum_{s=1}^{i-1} P_i(s;1,k) \, \overline{z}_i(s;k) + \sum_{s=j+1}^{k_i} P_i(s;1,k-1) \, \overline{z}_i(s;k-1) \quad (A.9)$$

The first term in Eq.(A.9) is the execution times for the modules succeeding the entry module(s)  $(M_i(s;1))$  for s < j that are executed before  $M_i(j;1)$  in the bulk module invocation. The second term is the execution times of those modules succeeding the entry module(s)  $(M_i(s;1))$  for s > j executed after  $M_i(j;1)$ .

The third component of  $W_i(j;k)$  is used to keep track of the new module invocations that arrive after the invocation for the entry module  $M_i(j;1)$  and their succeeding modules subsequently generated from the newly arrived invocations. Thus, we have

$$W3, \{j;k\} = [W, \{j;k-1\} + \overline{z}, \{j;k-1\}] \sum_{r=1}^{r} \sum_{s=1}^{r_{r}} \lambda_{r}(s;1) \overline{z}_{r}(s;1) + [W_{i}(j;k-2) + \overline{z}, \{j;k-2\}] \sum_{r=1}^{r} \sum_{s=1}^{k_{r}} \lambda_{r}(s;1) P_{r}(s;1,2) \overline{z}_{r}(s;2) + \frac{1}{r} \sum_{s=1}^{r} \lambda_{s}(s;2) P_{s}(s;2) P_{s}(s;2) + \frac{1}{r} \sum_{s=1}^{r} \lambda_{s}(s;2) P_{s}(s;2) P_{$$

$$+[W_{r}(j;1)+\overline{x}_{r}(j;1)]\sum_{r=1}^{q}\sum_{\substack{s=1\\d(s)\geq k-1}}^{\frac{k}{r}}\lambda_{r}(s;1)P_{r}(s;1,k-1)\overline{x}_{r}(s;k-1) \quad (A.10)$$

Due to the first-come-first-serve scheduling, those module invocations from other computers arriving during the response time (waiting plus execution) of  $M_i(j;k-1)$  contribute a part of the waiting time for  $M_i(j;k)$ . Thus the first term of Eq.(A.10) is the total time for executing those module invocations arriving during the response time of  $M_i(j;k-1)$ . Likewise, the remaining terms of Eq.(A.10) are the times for executing those module invocations from the same computer where  $P_r(s;1,t)$  represents the probability that  $M_r(s;1)$ After substituting  $\lambda_{s}(s;t)$ invokes  $M_r(s;t)$ . and  $\rho_r(s;t) = \lambda_r(s;t) \overline{x}_r(s;t)$  into  $=\lambda$ , (s;1) P, (s;1,t)Eq.(A.10), and simplifying, we have

$$W3_{i}(j;k) = \sum_{i=1}^{k-1} \left\{ \left[ W_{i}(j;t) + \overline{z}_{i}(j;t) \right] \sum_{r=1}^{k} \sum_{\substack{i=1\\ \delta_{i}(s) \geq k-t}}^{\delta_{r}} \rho_{r}(s;k-t) \right\} \quad (A.11)$$

Therefore, the mean module waiting time for  $M_i(j;k)$  is

$$W_{i}(j;k) = W1, (j;k) + W2, (j;k) + W3, (j;k)$$

(A.12)

for

$$i=1,2,...v$$

,  $j=1,2,...b_i$ , and  $d_i(j) \ge k \ge 2$ .

The mean module waiting time for each module is expressed in Eq.(A.4), (A.5) or (A.12). They can be determined by solving this set of linear equations. The mean response time for each module is the sum of its mean waiting time and mean execution time.

### CHAPTER III

# PRECEDENCE RELATIONS AND TASK ALLOCATION FOR DISTRIBUTED REAL-TIME SYSTEMS

# PRECEDENCE RELATIONS AND TASK ALLOCATION FOR DISTRIBUTED REAL-TIME SYSTEMS

### 1. INTRODUCTION

Although computer speed has increased several orders of magnitude during the past decades, the demand for computing capacity increases more rapidly. Many real-time applications require speed capability not achievable by a single processor. One approach to this problem is via distributed data processing (DDP) that concurrently processes an application on multiple processors. If properly designed and planned, DDP provides a more economical and reliable approach than the centralized processing with a single high-speed processor.

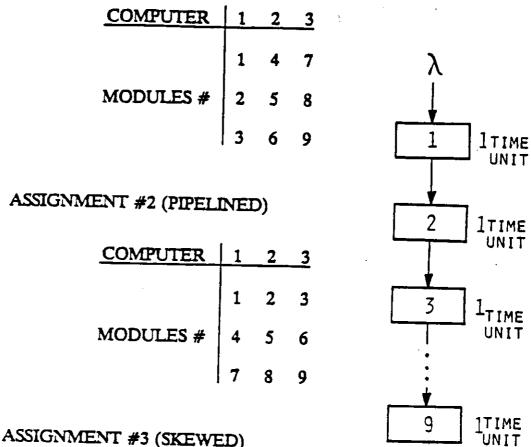

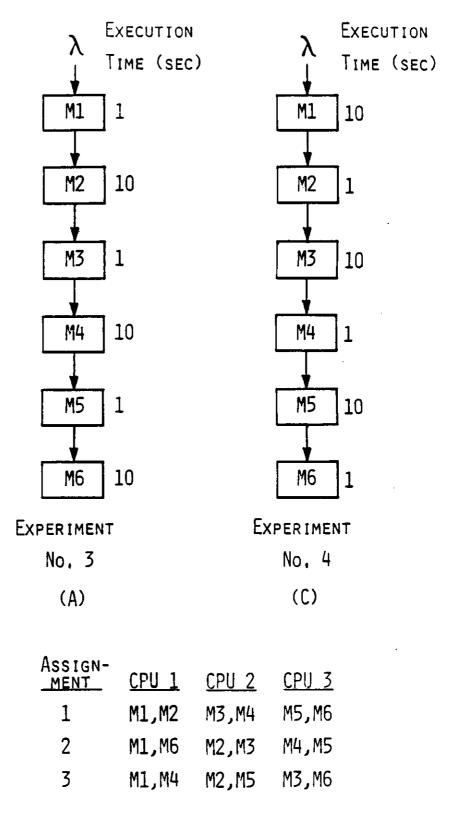

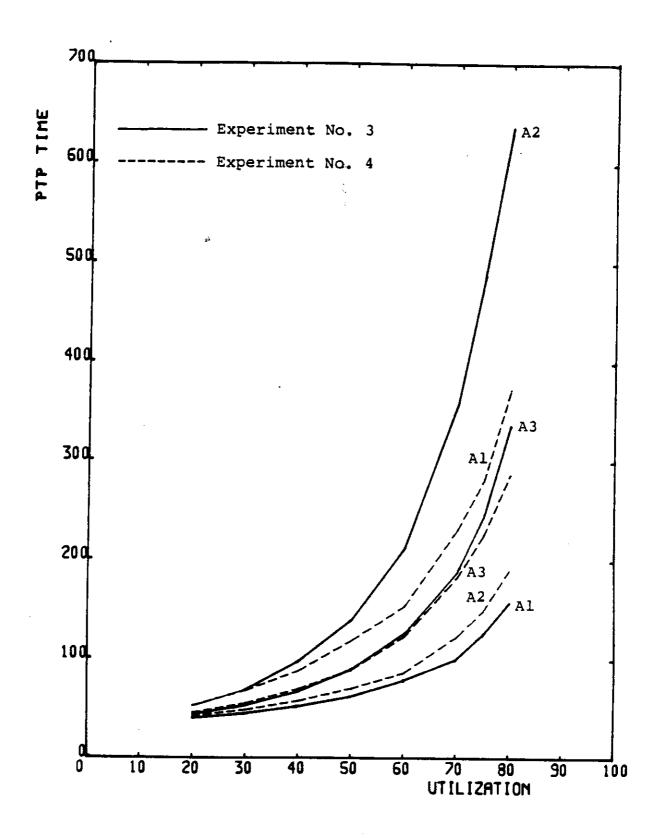

Task partitioning and task allocation are two major steps in the design of DDP systems [CHU80]. If these steps are not done properly, an increase in the number of processors in a system may actually result in a decrease of the total throughput. Assuming the software for an application (a task) has been partitioned into a set of program modules (or, subroutines), we study how to properly allocate (assign) these modules to the set of processors in the DDP system.

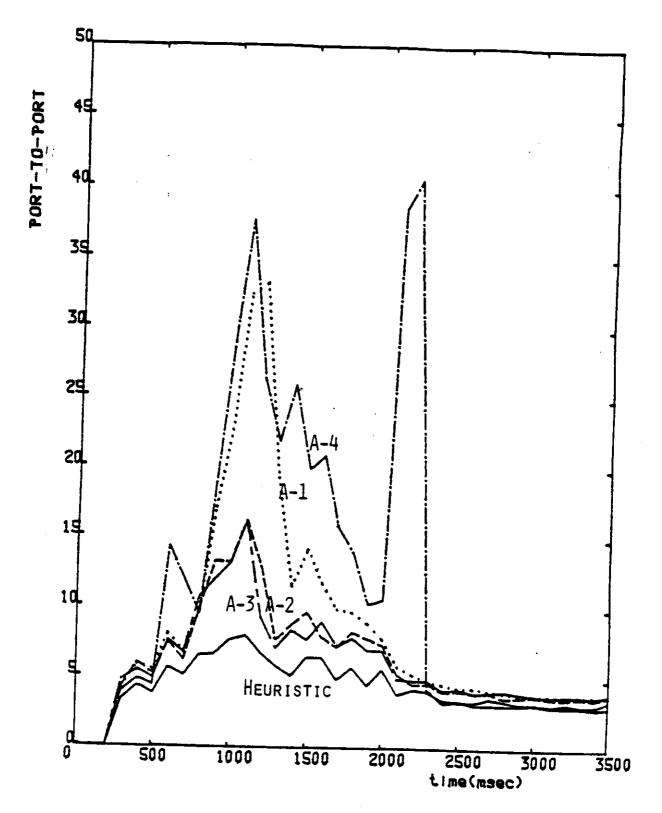

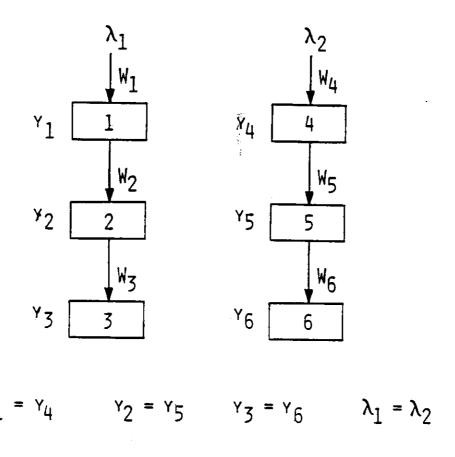

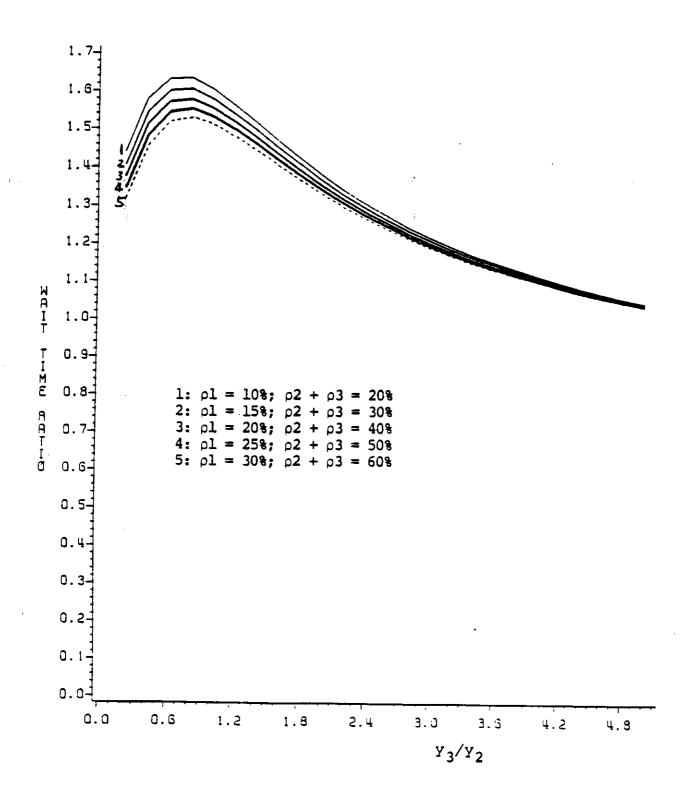

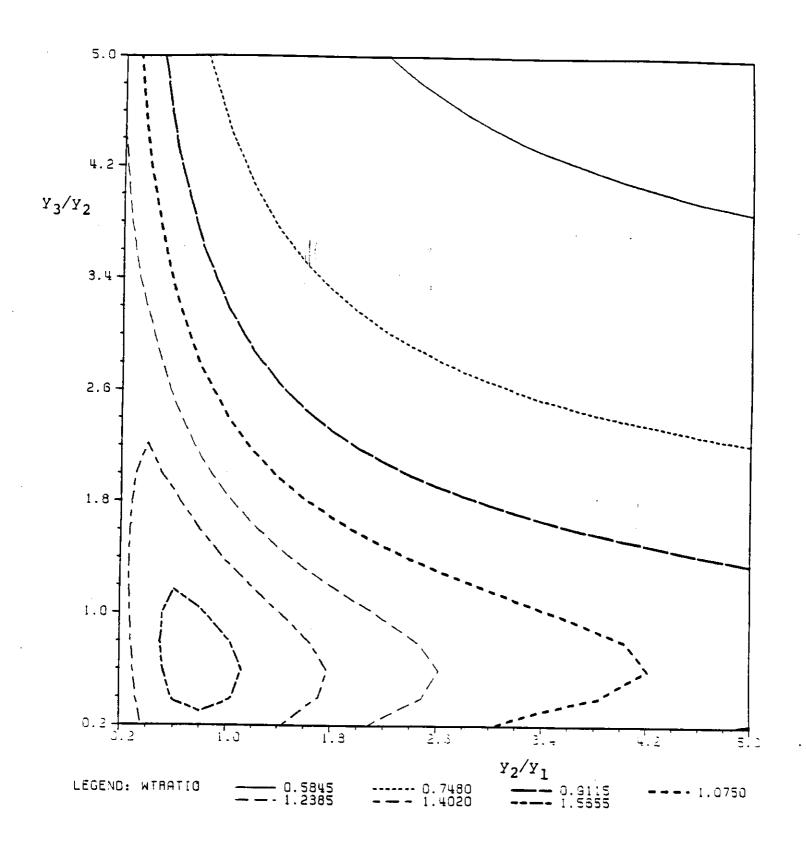

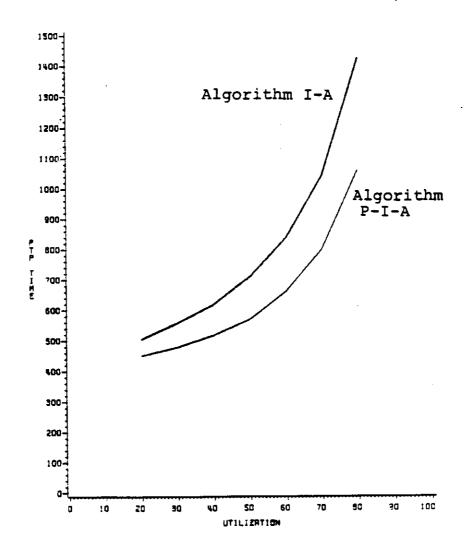

We shall first present the three important input parameters for task allocation: intermodule communication (IMC), accumulative execution time (AET) of each module, and precedence relations (PR) among program modules. Next, we propose an objective function for task allocation that is based on IMC and AET. A task-allocation algorithm based on that objective function is then proposed. The PR states that a program module should not be enabled before all its predecessor(s) finish execution. Simulation and analytical results are shown and they reveal that the program-size ratio between a module and its predecessor module plays an important role in task allocation, in terms of task response time. An improved

task-allocation algorithm, based on PR, IMC, and AET, is then proposed. Examples are given to illustrate the performance improvement when PR is considered in the task allocation.

### 2. A NEW OBJECTIVE FUNCTION FOR TASK ALLOCATION

### 2.1 Key Parameters

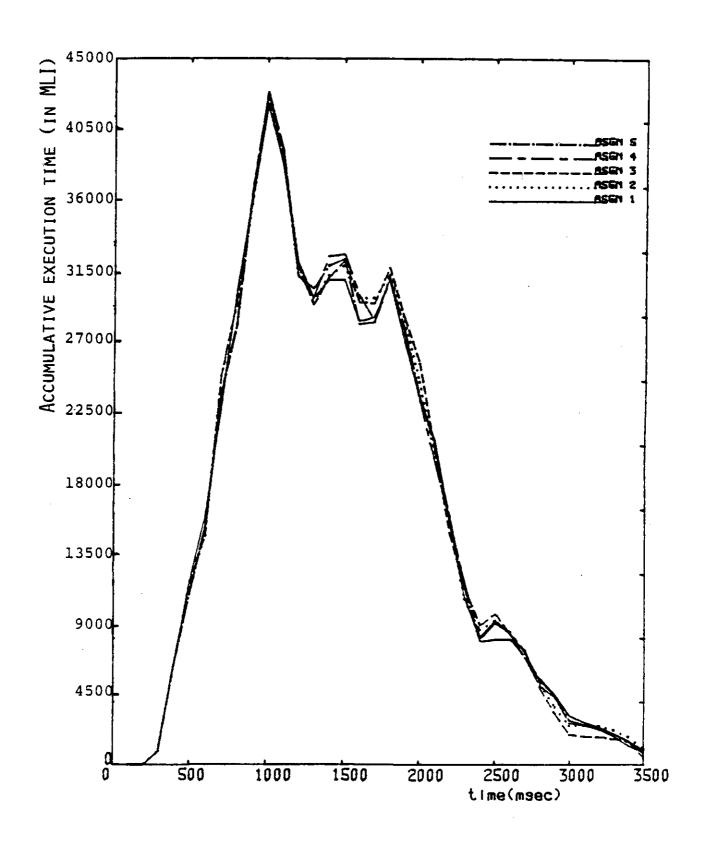

The three parameters that play important roles in module assignment are intermodule communication (IMC), accumulative execution time (AET) of each module, and precedence relations (PR) among program modules. The AET for a module  $M_j$  during a time interval  $(t_h, t_{h+1})$  is the total execution time incurred for this module during that time interval, i.e.,

$$T_j(t_h, t_{h+1}) = N_j(t_h, t_{h+1}) y_j(t_h, t_{h+1})$$

where  $N_j(t_h,t_{h+1})$  = number of times module  $M_j$  executes during  $(t_h,t_{h+1})$ , and  $y_j(t_h,t_{h+1})$  = average execution time of  $M_j$  during  $(t_h,t_{h+1})$ . Both the  $y_j$  and AET can be expressed in machine-language instructions (MLI) executed. Although the execution time of a machine-language instruction varies from instruction to instruction, we can use the mean instruction execution time given the mix ratios for various different instructions. Our study reveals that both the number of module executions and the AET are almost independent of module assignments when the load offered to the system is fixed. Fig. 1 shows that the AETs produced by five different assignments for a module in a space-defense distributed system 1 are almost identical.

IMC is the communication between program modules through shared files. When a module on a processor writes to or reads from a shared file on another processor, such IMC becomes IPC (interprocessor communication) and requires processing overhead. The importance of IPC minimization has been recognized by many researchers [CHU78, GENT78,

<sup>&</sup>lt;sup>1</sup> This system, the Distributed Processing Architecture Design (DPAD) system, will be used as an example in Section 3. A portion of its control-and-data-flow graph is given in Fig. 2.

Fig. 1. Accumulative execution time for Module  $M_8$ ,  $T_8(\tau$ ,  $\tau$ +100msec)

FIG. 2. EXAMPLE 1: A CONTROL-AND-DATA-FLOW GRAPH FOR A SPACE-DEFENSE TASK

IRAN82, WU84, CHU84b]. IPC can be reduced by assigning a pair of heavily communicating modules to the same processor. IMC can also be assumed to be independent of module assignments [LAN85]. A method for estimating both IMC and AET has been reported in [CHU84b].

IPC varies with module assignments because the occurrence of IPC between two communicating modules depends on whether these two modules are assigned to different processors. For example, if two modules communicate through a replicated shared file and reside on different processors, then the file is replicated on each processor. When a module updates the file, it updates the copy on its local processor. It then sends the updates to the remote processor, resulting in IPC which requires processing load on both the sending and receiving processors. Such IPC is eliminated if the two modules are assigned to the same processor since both modules are sharing the same local file copy.

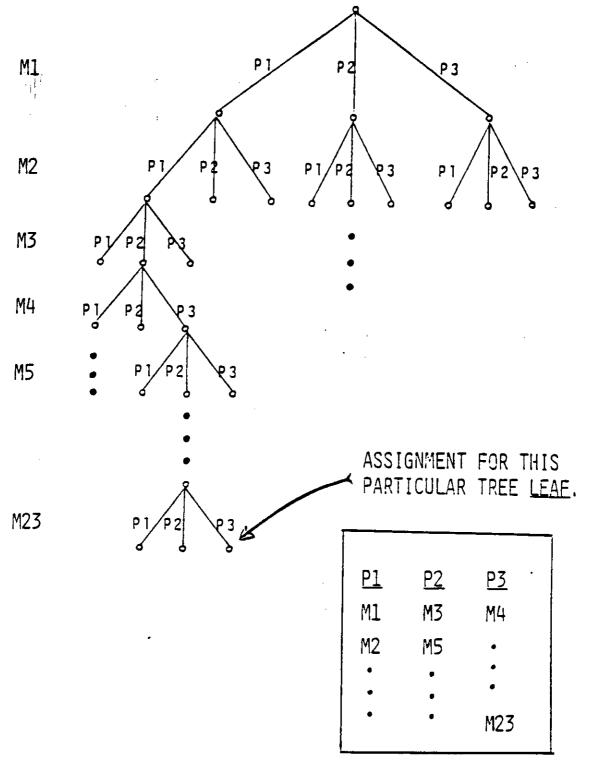

### 2.2 The Objective Function

Since each module can be assigned to any of the S processors, there are  $S^J$  different ways to assign J modules to S processors, assuming that each module is assigned to one and only one processor. This can be represented by an assignment tree with  $S^J$  leaves, each leaf corresponding to a possible assignment. This tree has J levels, each representing a module. At each non-leaf node there are S downward branches, each representing the choice of a processor to host the particular module. An example with J=23 and S=3 is shown in Fig. 3.

An exhaustive search approach for module assignment is to search every leaf of the assignment tree. The optimal module assignment is the one that minimizes (or maximizes, e.g., throughput) the given objective function. Exhaustive search is usually undesirable because of the enormous amount of time required. For example, if the computation time for a leaf is 250 ps on a computer system, then the enumeration for a tree with 3<sup>20</sup> leaves requires about 10

Fig. 3. An Assignment Tree

days of processing time which is prohibitive.

Existing approaches to task allocation can be divided into three categories: graph-theoretic [JENN77, STON77, STON78a, STON78b, RAO79, BOKH79, BOKH81, CHOU82], integer 0-1 programming approach [CHU69, CHU80, MA82], and heuristic approach [GYLY76, EFE82]. Many of these methods try to minimize a job's total cost which is defined as the sum, across all processors, of both processing cost and IPC cost dedicated to that job. This might be acceptable for a distributed system shared by multiple simultaneous non-real-time applications (jobs), each having program modules running on some or all of the multiple processors. Such applications attempt to maximize the total throughput. For a distributed system with identical processors, their formulation is equivalent to the minimization of IPC since the processing cost is fixed.

For real-time systems, response time is the most important performance measure. A computer system is designated solely for a specific application, i.e., the system is not shared by any other application. The system is required to finish a certain task within a specified time limit. Merely minimizing IPC alone may not produce a good assignment. In fact, a minimum-IPC assignment will assign all program modules to a single processor which will saturate the system and thus yield poor response time.

The processor with the heaviest loading in a distributed system is the one that causes the bottleneck. For instance, for a system with three processors, an assignment requiring 58%, 60%, and 61% of processor utilizations might have a better response time than a second assignment with 20%, 40% and 90% utilizations. This is mainly due to the fact that the second assignment has a bottleneck processor more heavily loaded than the first assignment, and queuing delay is a non-linear function that rises rapidly with the level of bottleneck (processor load).

The processor load consists of the loads due to 1) program module execution and 2) IPC. Therefore, both AET and IPC play important roles in module assignment and thus influence task response time. AET is usually represented in MLI (see Section 2.1). The number of transferred IPC words can be converted into the MLI's spent by both processors that send and receive the IPC.

For a given assignment X, the work load L(r;X) on a given processor r is

$$L(r;X) = \sum_{j=1}^{J} x_{jr} T_{j} + \sum_{\substack{s=1\\s \neq r}}^{S} \left[ IPC(r,s;X) + IPC(s,r;X) \right]$$

(1)

where  $X=[x_{jr}]$  is the assignment matrix in which  $x_{jr}=1$  indicates that module  $M_j$  is assigned to processor r. The first term in the equation is the AET for all modules assigned to processor r. The second term is IPC overhead which consists of two parts: overhead due to the IPC originated from processor r to other processors, and incoming messages to processor r from other processors. For a system whose file-update messages dominate the IPC traffic, we can ignore other types of IPC such as module enablement messages and system control messages. The total overhead due to outgoing IPC at processor r is

$$\sum_{\substack{s=1\\s\neq r}}^{S} IPC(r,s;X) = w \sum_{j=1}^{J} x_{jr} \sum_{k=1}^{K} V_{jk} \sum_{\substack{s=1\\s\neq r}}^{S} \delta_{ks}$$

(2)

where K is the number of files used in the distributed system;  $V_{jk}$  is the IMC message volume sent from  $M_j$  to update the replicated file  $F_k$ ;  $\delta_{ks}$  indicates whether a replicated copy of  $F_k$  resides at processor s; the term  $\sum_{\substack{s=1\\s\neq r}}^{S} \delta_{ks}$  gives the number of remote copies of  $F_k$  that must be

updated; and w is a weighting constant for converting the message volume into MLI's. For a system with message-broadcasting capability, a file update need only be sent out once; thus the term  $\sum_{s=1}^{S} \delta_{ks}$  in eq. (2) should be replaced by the constant one.

Similarly, the total overhead at processor r for incoming IPC from all remote sites is

$$\sum_{\substack{s=1\\s\neq r}}^{S} IPC(s,r;X) = w \sum_{\substack{s=1\\s\neq r}}^{S} \sum_{j=1}^{J} x_{js} \sum_{k=1}^{K} V_{jk} \, \delta_{kr}$$

(3)

Based on our previous discussion, we propose to use the work load of the bottleneck processor (in unit of MLI) as the objective function for module assignment, i.e.,

$$Bottleneck(X) = \max_{r=1}^{S} \left\{ L(r;X) \right\}$$

(4)

We want to find the assignment that yields the minimum bottleneck [CHU84a] among all possible assignments in the assignment tree, i.e.,

$$\min_{X} \left\{ Bottleneck(X) \right\} \tag{5}$$

Substituting eqs. (1) and (4) into eq. (5) yields

$$\min_{X} \left\{ \max_{r=1}^{S} \left[ AET(r) + IPC(r) \right] \right\}$$

(6)

where AET(r) and IPC(r) are the total module execution time and total IPC overhead incurred at processor r.

A good assignment can be obtained from minimizing IPC and balancing processor loads among the set of processors. A minimum-bottleneck assignment generally has low IPC and fairly balanced processor loads because:

- 1. If the loads were not fairly balanced for an assignment, the bottleneck (highest load among all processors) would be high and this assignment would not be a minimum-bottleneck assignment.

- 2. If a given assignment had high IPC, the sum of processor loads over all processors would be

|  | • |  |  |  |

|--|---|--|--|--|

IPC during Phase I, heavily communicating modules are combined into groups if the AET's of the resulting groups are not too large. Each group is a set of modules which will be assigned as a single unit to a processor during Phase II. The computation required for Phase I is small because this phase is a linear-time algorithm. Phases II assigns the module groups to available processors such that the bottleneck (in the most heavily utilized processor) is minimized. Our algorithm assumes that

- 1. there are J modules,  $M_1, M_2, \ldots, M_J$ , and S processors;

- 2. the average AET (over the peak-load period),  $T_j$ , for all modules  $M_j$  (j=1,...,J) are given;

- 3. the average IMC between any module pair  $M_i$  and  $M_j$ ,  $IMC_{i,j}$ ,  $(i=1,...J;\ j=1,...J)$  is given.

### **ALGORITHM I-A:**

Phase I: Combine modules with large IMC into groups to reduce total system load.

1.1 Initially list all module pairs  $(M_i, M_j)$  in the descending order of IMC volume.

Calculate average AET and average processor load:

$$\overline{AET} \leftarrow \sum_{j=1}^{J} T_j / J$$

$$\overline{PL} \leftarrow \sum_{j=1}^{J} T_j / S$$

Set threshold values for IMC volume and for processor load:

$$\theta_{IMC} - \overline{AET} \times \alpha \%$$

$\theta_{PL} - \overline{PL} \times \beta \%$

Let each program module form a distinct group (a set):  $G_j \leftarrow \{M_j\} \quad j = 1,...,J$

1.2 If no more pairs exist in the module-pair list go to Phase II.

Pick the next pair of modules,  $M_i$  and  $M_j$ , and delete this pair from the list.

- 1.3 If  $IMC_{i,j} \leq \theta_{IMC}$  go to Phase II.

- 1.4 Find the group  $G_s$  that contains  $M_i$ , and the group  $G_t$  that contains  $M_j$  (i.e.,  $M_i \in G_s$ ,  $M_j \in G_t$ ). If s = t (i.e., if  $M_i$  and  $M_j$  are already in the same group)

- 1.5 If  $T_s + T_t > \theta_{PL}$  go to Step 1.2.

Combine the two groups

$$G_s$$

and  $G_t$  into a single one:

$$G_s \leftarrow G_s \cup G_t$$

$$G_t \leftarrow \emptyset$$

$$T_s \leftarrow T_s + T_t$$

$$T_t \leftarrow 0$$

1.7 Go to Step 1.2.

Phase II: Assign module groups to processors.

- 2.1 Perform an exhaustive search through the new assignment tree for the assignment that has the smallest bottleneck.

- 2.2 Stop.

Note Phase I reduces J modules to G groups, G < J, which corresponds to a much smaller assignment tree. Let us now discuss the rationale of Steps 1.3 and 1.5, respectively.

- For a pair of modules whose IMC is smaller than the IMC threshold  $\theta_{IMC}$  (  $\alpha$  % of  $\overline{AET}$ ), merging them gives little benefit in terms of the IPC saved. Our experience reveals that a should range between 1% to 10%.

- Our assignment algorithm reduces large IPC. However, when merging two groups into one, we should leave some processing capacity in the resulting new group for accommodating the remaining IPC and the possible grouping with some other module groups. If two groups were combined and formed a group that was too large, we could not obtain a balanced-load assignment during Phase II. Therefore, the processor-load threshold  $\theta_{PL}$  is limited to  $\beta$  % of the average processor load  $\overline{PL}$ .

### 3.2 Example 1: the DPAD System

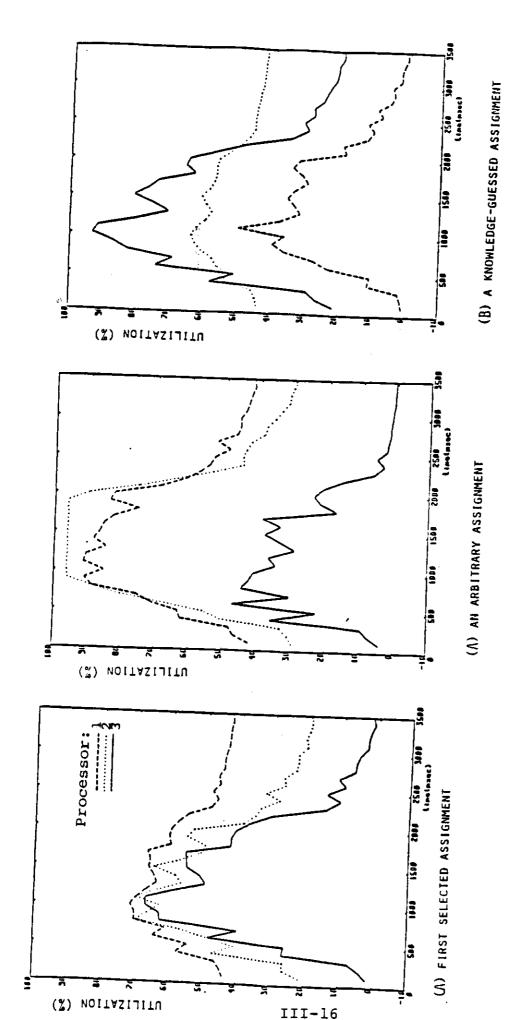

In this section we demonstrate the performance of both the proposed objective function and Algorithm I-A by applying them to an example system, the Distributed Processing Architecture Design (DPAD) system. The DPAD system was developed to manage the data processing and radar resources for a space-defense application [GREE80, HOFF80]. A portion of its control-and-data-flow graph is given in Fig. 2. The twenty (20) modules are to be assigned to three processors.

### 3.2.1 Performance of the Proposed Objective Function

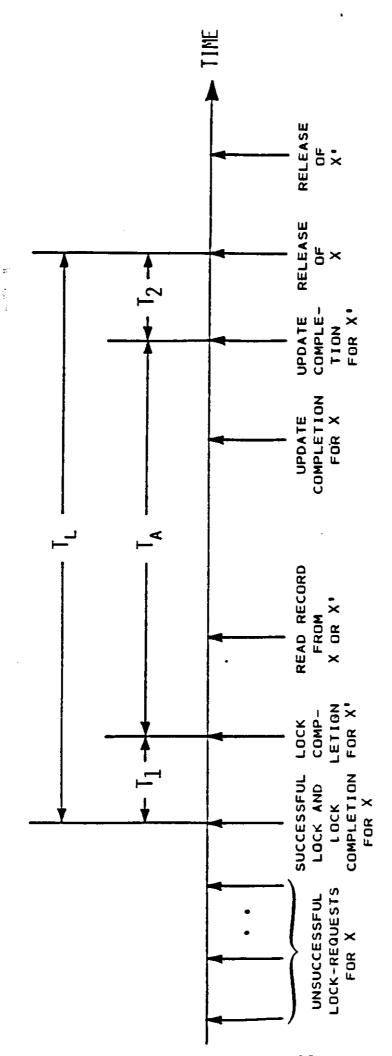

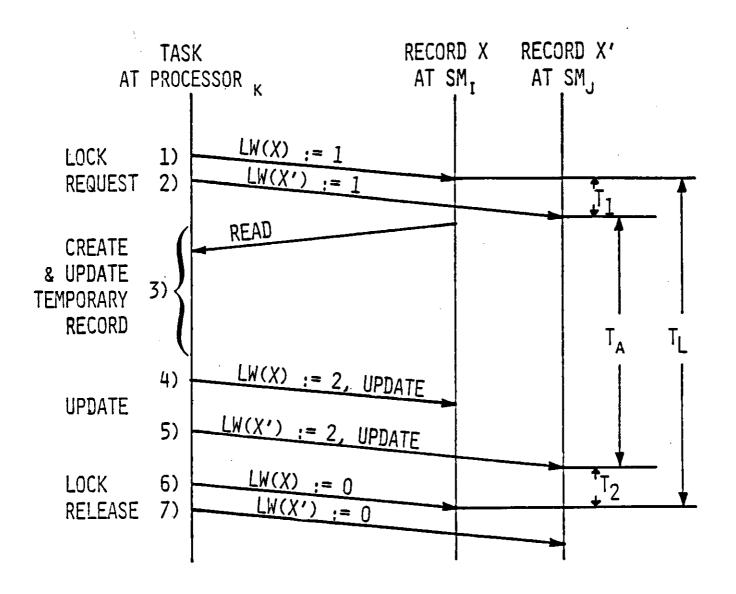

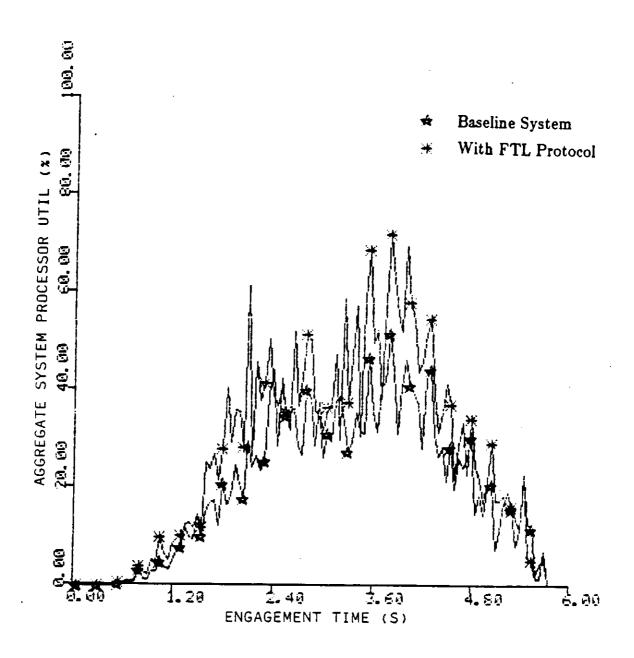

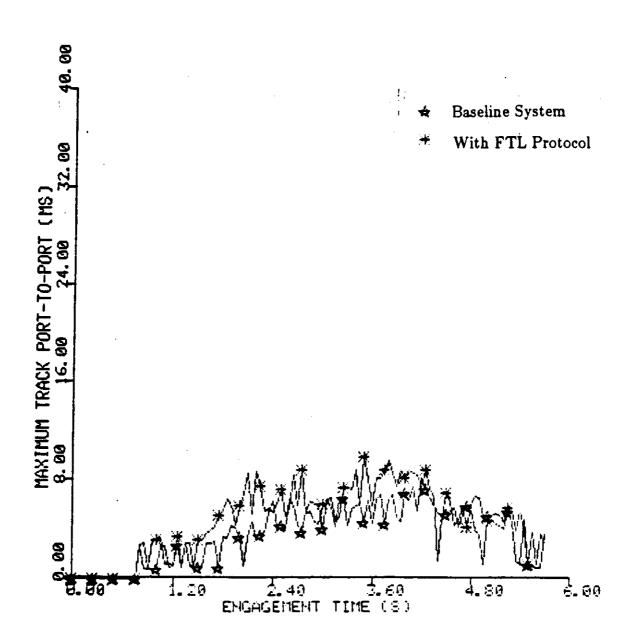

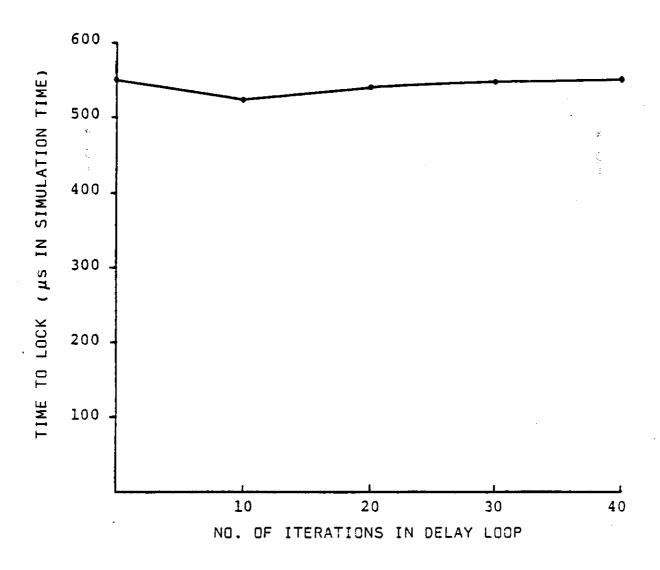

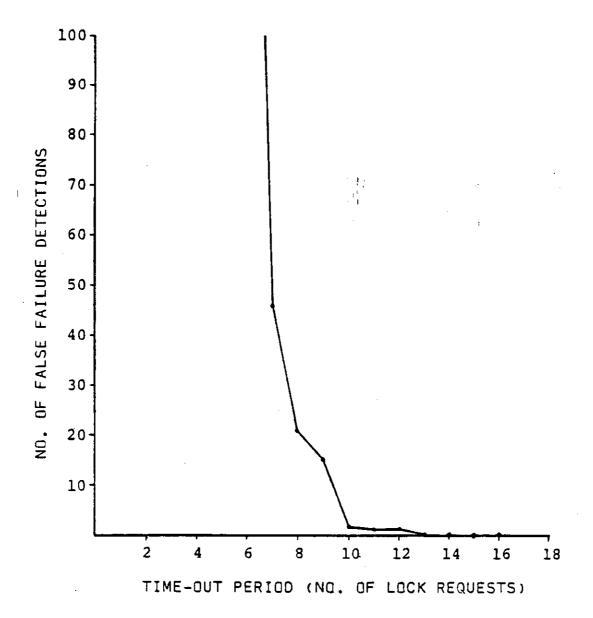

The average AET and IMC during the peak-load period for all modules of the DPAD system are given in Table 1. The identified peak-load period is from 1.0 s to 2.0 s of mission time. For example,  $T_8 = 32,055$  MLI is the average of ten measured AET values within the period, at each increment of 100 ms. Column 3 shows the file(s) updated by the write-module. Each IMC value in column 4 is the total file-update volume for 100 ms, written to the file in column 3 by the write-module in column 1; like AET, this IMC value is an average of ten values in the peak-load period. Column 5 lists all the modules which read the updated file. If a read-module for a file and the associated write-module are on different processors, both processors would have a copy of the file and IPC occurs for updating the replicated file copy.