FTSS: A FAULT-TOLERANT STORAGE SYSTEM SUPPORTING HIGH AVAILABILITY AND SECURITY IN A DISTRIBUTED PROCESSING ENVIRONMENT

Baron O. A. Grey

December 1984 CSD-840066

# UNIVERSITY OF CALIFORNIA Los Angeles

FTSS: A Fault-Tolerant Storage System Supporting High Availability and Security in a Distributed Processing Environment

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Computer Science

by

Baron Octavius A. Grey

© Copyright by

Baron Octavius A. Grey

1985

The dissertation of Baron Octavius A. Grey is approved.

Kirby Baker

Harold Borko

D. Stott Parker

Algirdas Avižienis

Mand Mennels

David Rennels, Committee Chair

University of California, Los Angeles

1985

To

Ermine, Gilbert, Thelma, and Connie

## TABLE OF CONTENTS

|                                         | page     |

|-----------------------------------------|----------|

|                                         |          |

|                                         |          |

| ACKNOWLEDGMENTS                         | хi       |

| VITA                                    | xii      |

| ABSTRACT OF THE DISSERTATION            | xiii     |

| *                                       | ,        |

| 1 INTRODUCTION                          | 1<br>3   |

| 1.1 The Problems of Distributed Storage | 4        |

| 1.1.1 Availability                      | 6        |

| 1.1.2 Extensibility                     | 6        |

| 1.1.4 Functionality                     | 7        |

| - 11-5 Cost                             | 8        |

| 1.2 Centralization as a Solution        | 8        |

| 1.3 The Need for Fault-Tolerance        | 12       |

| 1.4 Related Work                        | 14<br>14 |

| 1.5 Organization of the Thesis          | 14       |

| 2 ARCHITECTURAL DESIGN ISSUES           | 17       |

| 2.1 Introduction                        | 18       |

| 2.1 Introduction                        | 19       |

| 9.3 Application Support                 | 20       |

| 2.4 Host Software Minimization          | 22       |

| 2.5 Multiple-Host Support               | 23       |

| 2.6 Reliability and Availability        | 24<br>25 |

| 2.7 Extensibility                       |          |

| 2.7.1 Hardware Extensibility            | 26<br>26 |

| 2.7.2 Software Extensibility            |          |

| 2.8 Security                            |          |

| 2.9.1 The Transaction Paradigm          | 29       |

| 2.10 Efficiency                         | 31       |

| 2.11 Summary                            | 31       |

|                                         | 20       |

| 3 SOFTWARE SYSTEM MODEL                 | 32<br>32 |

| 3.1 Strawman Storage System             |          |

| 3.2 A Generalized Software Model        |          |

| 3.3 Software Design Overview            |          |

| 3.3.1 Security-Driven Models            |          |

| 3.3.2.1 The Kernel                      |          |

| 3.3.2.2 The Subsystem Level             | 41       |

| 3 2 2 3 The SMS Interface               | 42       |

| 3.4 Implementation of SMS               | 43       |

| 3.4.1 Kernel Implementation             | 40       |

| 3.4.1.1 An Overview                     |          |

| 3.4.1.1.1 Memory Management             | 420      |

|            | 3.4.1.1.2 Process Management                         | 49  |

|------------|------------------------------------------------------|-----|

|            | 3.4.1.1.3 I/O Management                             | 50  |

|            | 3.4.1.2 Kernel Modules                               | 51  |

|            | 3.4.1.2.1 Capabilities                               | 51  |

|            | 3.4.1.2.2 Objects                                    | 52  |

|            | 3.4.1.2.3 Data Abstraction                           | 54  |

|            | 3.4.1.9.4 I/O                                        | 55  |

|            | 3.4.1.2.4 I/O                                        | 55  |

|            | 3.4.2 Subsystem Implementations                      | 56  |

|            | 3.4.2.1 Process Management Subsystem                 | 59  |

| <i>j.</i>  |                                                      | 61  |

|            | 3.4.2.3 Security Subsystem                           | 63  |

| 1          | 3.4.2.4 Transaction Subsystem                        | 65  |

| •          | 3.4.2.5 Object Management Subsystem                  | 67  |

|            | 3.4.2.6 System Monitor Subsystem                     |     |

| 3.5        | Using the System 3.5.1 The Execution Environment     | 68  |

|            | 3.5.1 The Execution Environment                      | 68  |

|            | 2.5.9 Abstract Data Types                            | 73  |

| 3.6        | Building an Operating System Interface               | 75  |

| 3.7        | Summary                                              | 84  |

|            | ·                                                    |     |

| 4 SECU     | RITY ISSUES                                          | 86  |

| 4.1        | Introduction                                         | 86  |

|            | 4.1.1 Limiting the Scope                             | 88  |

| 4.2        |                                                      | 88  |

| 1.2        | 4.2.1 Capability Sealing                             | 90  |

| 4 3        | The Mechanism in Use                                 | 95  |

| 4.0        | 4.3.1 Protection                                     | 97  |

|            | 4.3.2 Revocation                                     | 97  |

|            | Implementation Issues                                | 101 |

| 4.4        | Implementation issues                                | 101 |

|            | 4.4.1 Kernel Support                                 | 106 |

|            | 4.4.2 User Level Support                             | 110 |

| 4.5        | Summary                                              | 110 |

|            | . Dr. Imp. 1001100                                   | 11  |

| 5 AVAII    | LABILITY ISSUES                                      |     |

| 5.1        | Conceptual Framework                                 | 111 |

| 5.2        | Hardware Reliability versus Information Availability | 113 |

| 5.3        | Approaches to Achieving High Availability            | 114 |

| 5.4        | An Information Availability Model                    | 116 |

|            | 5.4.1 Model Definition                               | 117 |

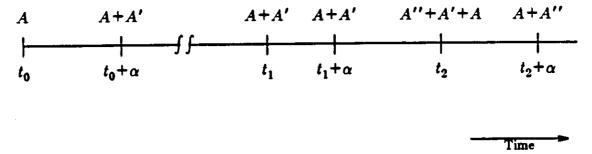

|            | 5.4.1.1 Network System Operation                     | 120 |

|            | 5.4.1.2 Hardware and Software Considerations         | 123 |

|            | 5.4.2 Model Development                              | 123 |

|            | 5.4.3 Reliability Estimation for Storage Sites       | 12  |

|            | 5.4.3.1 The Processor Subsystem                      | 12  |

|            | 5.4.3.2 The Storage Subsystem                        | 12  |

|            | 5.4.3.3 The Storage Site Subsystem                   | 12  |

|            | 5.4.4 Network Availability                           | 12  |

|            | 5.4.4.1 Simple Topologies                            | 13  |

|            | 5.4.4.2 Periodically Renewed Networks                | 13  |

|            | 5.4.4.3 Complex Topologies                           | 13  |

| 5.5        |                                                      | 14  |

| 5.6<br>5.6 |                                                      | 14  |

| 5.0        | Summary                                              | 1-1 |

|            |                                                      |     |

| R FAIII.   | r-tolerant storage system architectures                                        |

|------------|--------------------------------------------------------------------------------|

| 6.1        | T_tandustion                                                                   |

| 6.2        | Architectural Considerations                                                   |

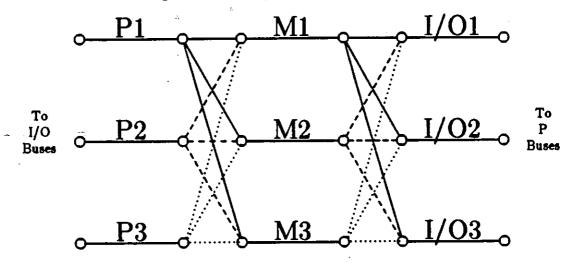

| 0.2        | 6.2.1 Extensible Topologies                                                    |

|            |                                                                                |

|            | a a d a Down Townslands                                                        |

|            | 6.2.1.2 Bus Topologies                                                         |

| 6.3        | A Highly Reliable Architecture for Doin's                                      |

|            | 6.3.1 Hierarchical Tree Systems 6.3.2 Fault-Tolerant Hierarchical Tree Systems |

|            | 6.3.2 Fault-Tolerant Hierarchical Tree Systems                                 |

|            | 6.3.3 The Basic Topology                                                       |

|            | 6.3.4 Properties of the Topology                                               |

|            | 6.3.5 Routing 6.3.6 Extensibility                                              |

|            | 6.3.6 Extensibility                                                            |

| 8.4        | Fault-Tolerance and Reliability                                                |

| 0.1        | 6.4.1 Reliability Analysis                                                     |

|            | 6.4.2 Discussion of Results                                                    |

| A F        | TOCAT!                                                                         |

| 6.5        | Summary                                                                        |

| 6.6        | Summary                                                                        |

| - 2017     | OBJECT STORE: FAULT-TOLERANCE AND OTHER ISSUES                                 |

|            |                                                                                |

| 7.1        | Mapping r 155 onto a radio roleiant rice radio della minima                    |

| 7.2        | Object Representation in the IL                                                |

|            | 7.2.1 Object Representation in the IL                                          |

|            | 7.2.2 Object Representation in the BL                                          |

|            | 7.2.3 Consistency                                                              |

| 7.3        | Location                                                                       |

| 7.4        | Accessing Object Blocks                                                        |

|            | 7 4 1 Write/Undate Access                                                      |

|            | 7.4.2 Read Access                                                              |

| 7.5        | Migration                                                                      |

| 7.6        | Deletion                                                                       |

| 7.7<br>7.7 | _                                                                              |

| 4.4        |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            | 7.7.4 Link Failures                                                            |

|            | 7.7.5 Media Failures                                                           |

|            | 7.7.6 Host Failures                                                            |

| 7.8        | Summary                                                                        |

|            |                                                                                |

| 8 IMPI     | EMENTATION OF FTSS                                                             |

| 8.1        | Introduction                                                                   |

| 8.2        | The Basic System                                                               |

| 8.3        | FTSS Hardware                                                                  |

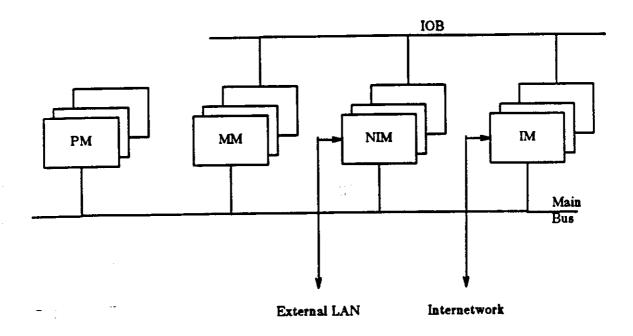

| ٠.٠        | 9.2.1 The Top Level                                                            |

|            | 8 3 1 1 Bus Architecture                                                       |

|            | 8.3.1.1.1 The Main Bus Architecture                                            |

|            | 8.3.1.1.2 The I/O Bus Architecture                                             |

|            | 8.3.1.2 Processor Modules                                                      |

|            | 8.3.1.3 RAM Buffer Modules                                                     |

|            | 8.3.1.4 Network Interface Modules                                              |

|            | 8.3.1.4 Network Interface Modules                                              |

|            | XXIS INTERPREMORK INTERPREDE MODULES                                           |

| 8.3.1.6 Other Modules                                                   | . 232          |

|-------------------------------------------------------------------------|----------------|

| 8 3 2 The Internetwork                                                  | . 232          |

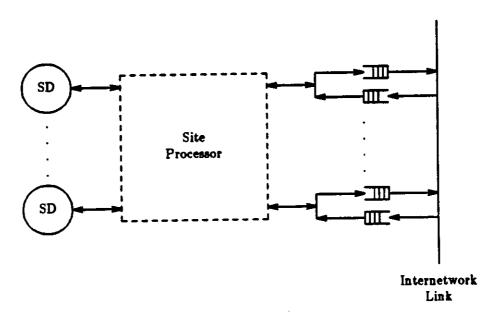

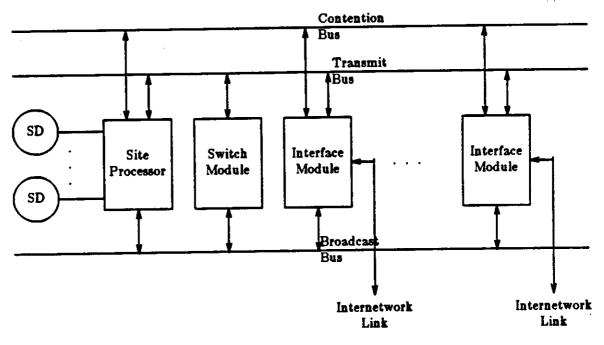

| 8.3.2.1 Storage Site Architecture                                       | . 233          |

| 8.3.2.2 Internetwork Communications                                     | . 237          |

| 8.4 FTSS Software                                                       | . 241          |

| 8.4.1 Distributed SMS Architecture                                      | . 242          |

| 8.4.2 Effect of FT on SMS Architecture                                  | . 243          |

| 8.5 Summary                                                             | . 243          |

| PERFORMANCE ISSUES                                                      | . 246          |

| 9.1 Introduction                                                        | . 246          |

| 9.2 Bandwidth Considerations                                            | . 247          |

| 9.3 The Simulation Model                                                | . 248          |

| 9.3.1 Model Description                                                 | . 248          |

| 9.4 Using the Model                                                     | . 252          |

| 9.4.1 Varying LAN Bandwidth                                             | . 258          |

| 9.4.2 Varying the IL Bandwidth                                          | . 257          |

| 9.4.3 Varying the Processor Bandwidth                                   | . 258          |

| 9.4.4 Varying the RAM Buffer Bandwidth                                  | . 200          |

| 9.4.5 Other Variables                                                   | . 260<br>. 262 |

| 9.5 Summary                                                             | . 202          |

| 10 CONCLUSIONS AND SUGGESTIONS FOR FURTHER RESEARCH                     | i 264          |

| Appendix A Diameter of $T_{2,p,1}$ Trees                                | 268            |

| Appendix B A Simple Distributed Routing Algorithm for $T_{2,p,1}$ Trees | 270            |

| Appendix C FTSS Data Link Control Procedure                             | 272            |

| Appendix D OBJECT-LEVEL ALGORITHMS                                      |                |

| Appendix E EXAMPLES OF OPERATING SYSTEM PRIMITIVES                      | 278            |

| DEFEDENCES                                                              | 284            |

# LIST OF FIGURES

|                                                                              | page |

|------------------------------------------------------------------------------|------|

| Figure 1.1: Distributed Local Network Architecture                           | 4    |

| •                                                                            |      |

| Figure 1.2: Distributed System with File Servers                             | 9    |

| Figure 1.3: Backend System with Distributed Storage System Components        | 11   |

| Figure 1.4: Backend Storage System with Independent Communication Subsystem  | 12   |

| Figure 3.1: Architecture of SMS                                              | 34   |

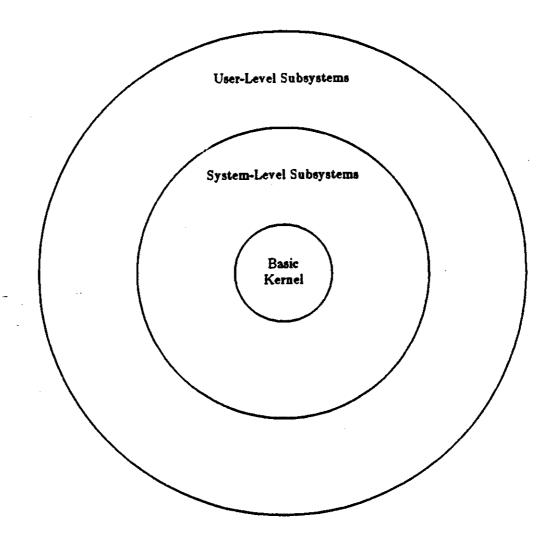

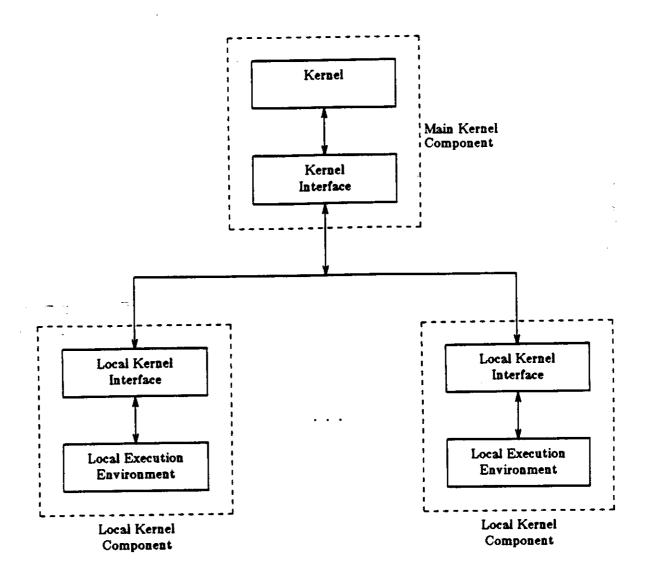

| Figure 3.2: Multi-Level Kernel Architecture                                  | 39   |

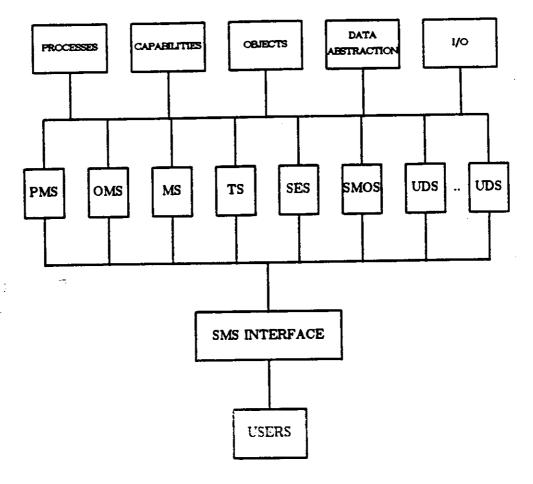

| Figure 3.3: Functional Block Diagram of the SMS                              | 44   |

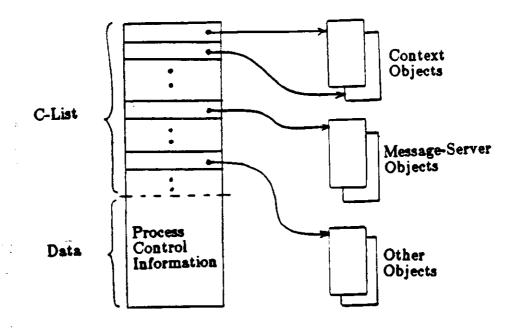

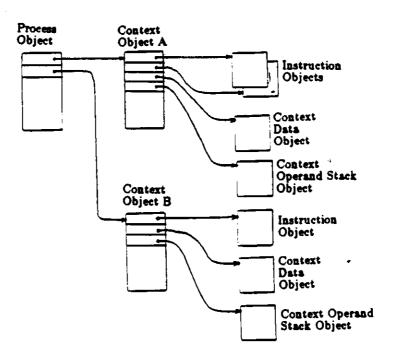

| Figure 3.4: Structure of a Process Object                                    | 71   |

| Figure 3.5: Process Object with Several Contexts                             | 73   |

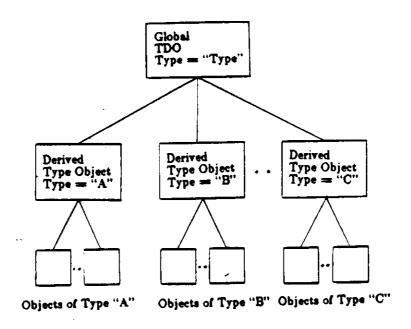

| Figure 3.6: Tree of Object Types                                             | 74   |

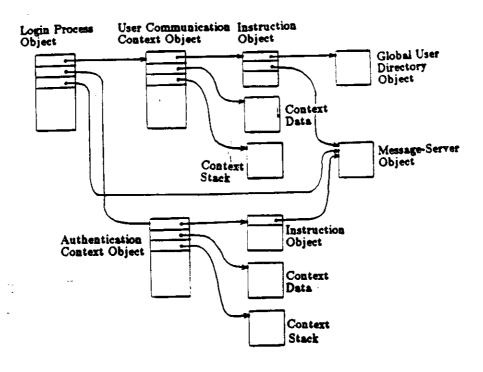

| Figure 3.7: Snapshot of Login Authentication                                 | 80   |

| Figure 3.8: Object Update                                                    | 81   |

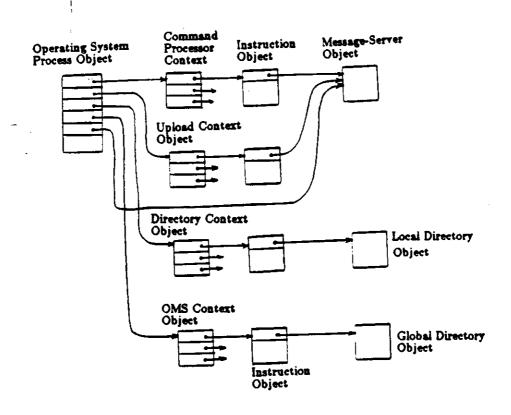

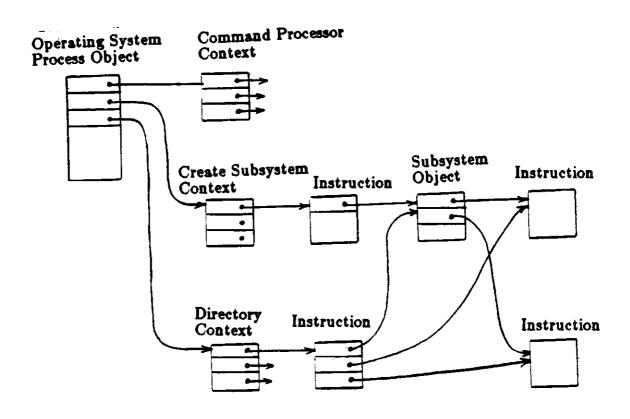

| Figure 3.9: Snapshot During Subsystem Creation                               | 83   |

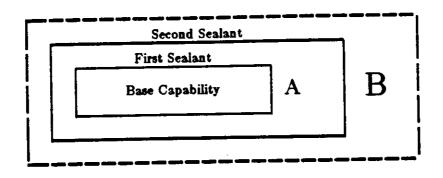

| Figure 4.1: Sealed Capability                                                | 96   |

| Figure 4.2: Organization of the SYS_SEAL object                              | 109  |

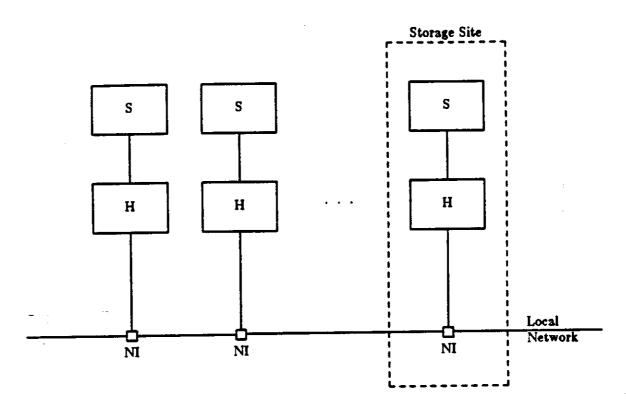

| Figure 5.1: Distributed System of Storage Sites                              | 113  |

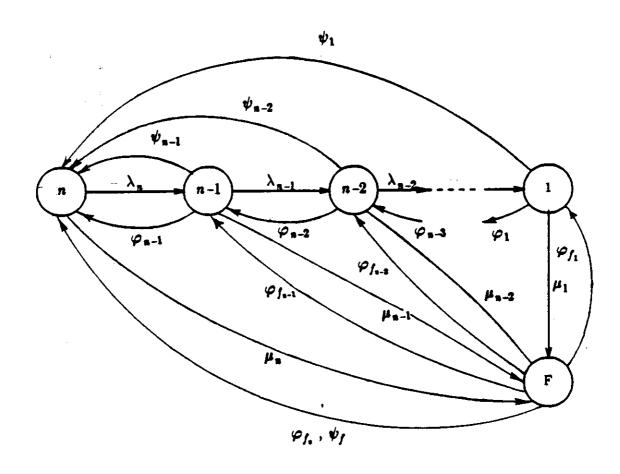

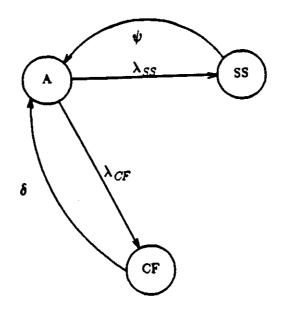

| Figure 5.2: Markov State Diagram of Information Availability                 | 119  |

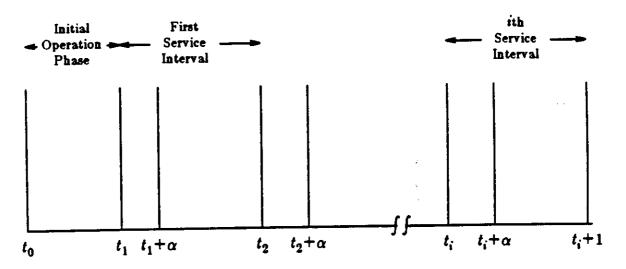

| Figure 5.3: Time Diagram Showing Operation of the LCN                        | 121  |

| Figure 5.4: Markov State Diagram for the Processor Subsystem                 | 124  |

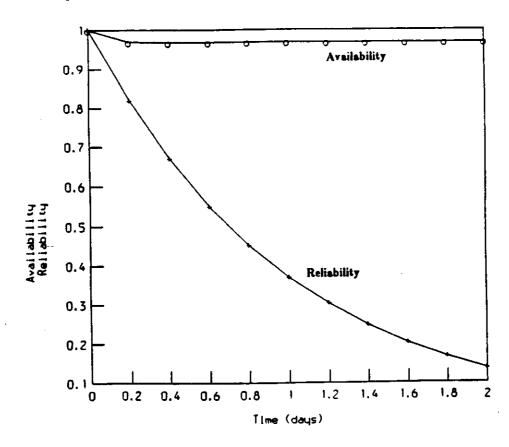

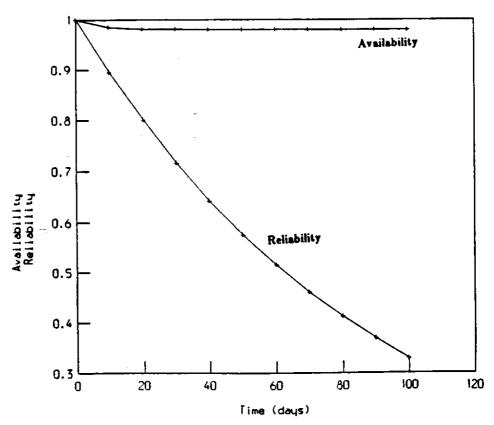

| Figure 5.5: Plot of Reliability and Availability for the Processor Subsystem | 125  |

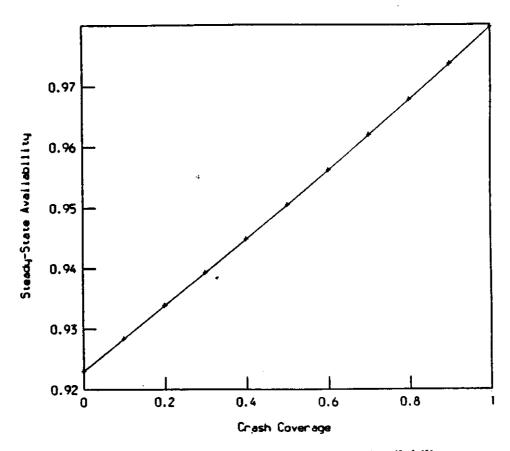

| Figure 5.6: Effect of Crash Coverage on Availability                         | 126  |

| Figure 5.7: Plot of Reliability and Availability for the Storage Subsystem   | 128  |

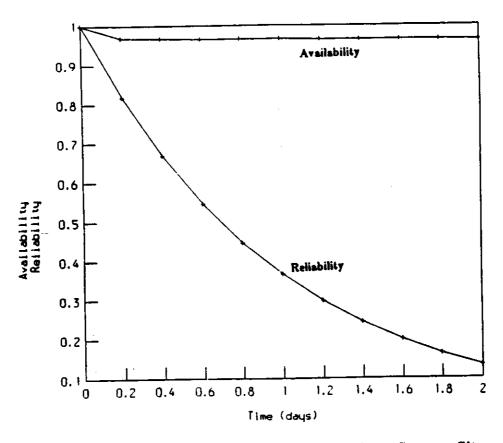

| Figure 5.8: Plot of Reliability and Availability for a Storage Site      | 130 |

|--------------------------------------------------------------------------|-----|

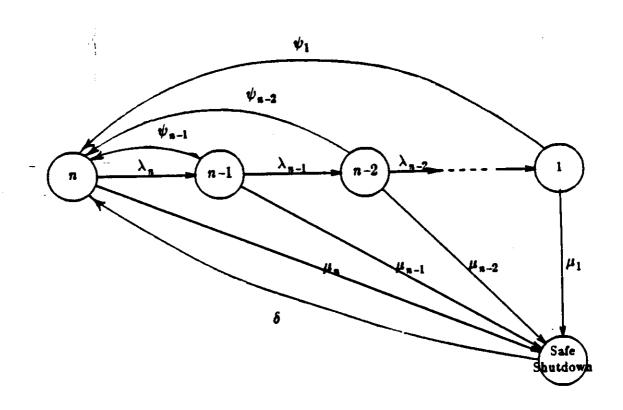

| Figure 5.9: Revised PRC Model                                            | 134 |

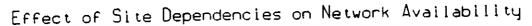

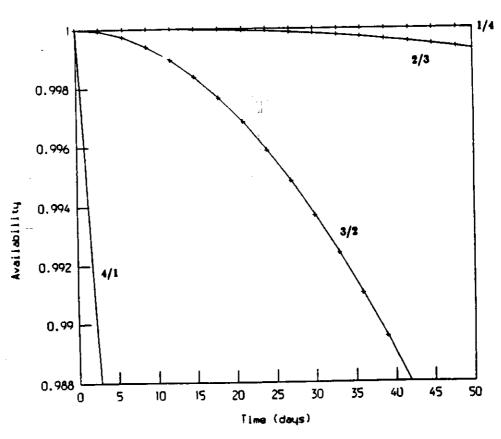

| Figure 5.10: Effect of Site Dependencies on Network Availability         | 137 |

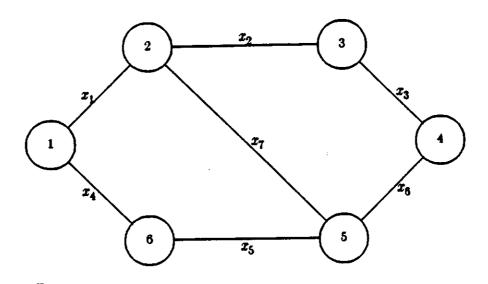

| Figure 5.11: Multi-Connected Computer Network                            | 139 |

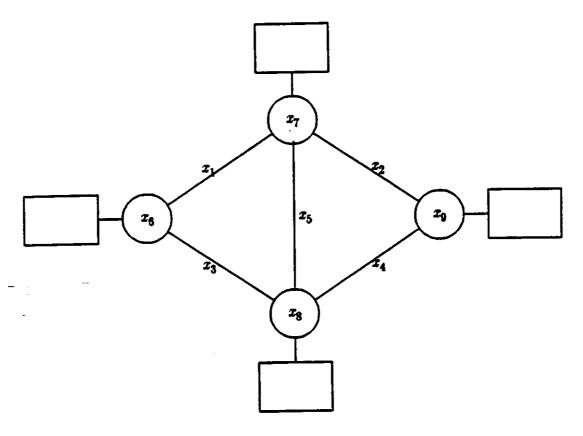

| Figure 5.12: Bridge Subnetwork of an Application Program                 | 140 |

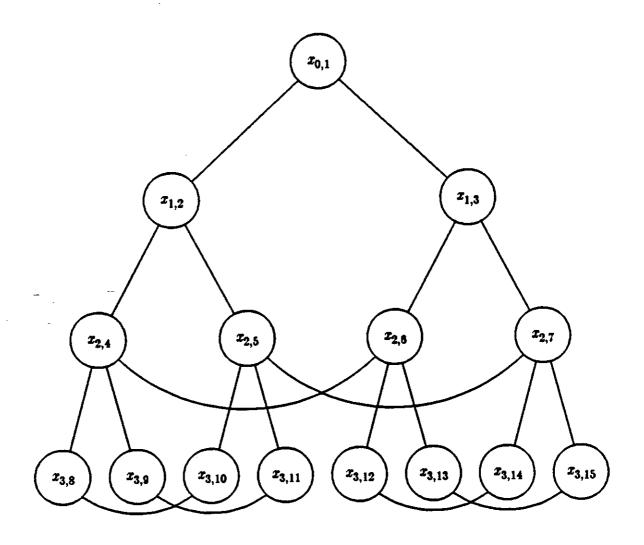

| Figure 6.1: A T <sub>2,4,1</sub> 1-FT Symmetrical Hierarchical Tree      | 155 |

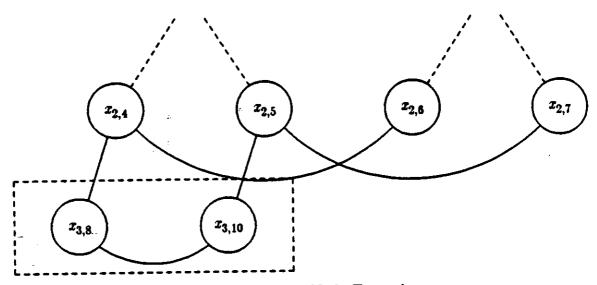

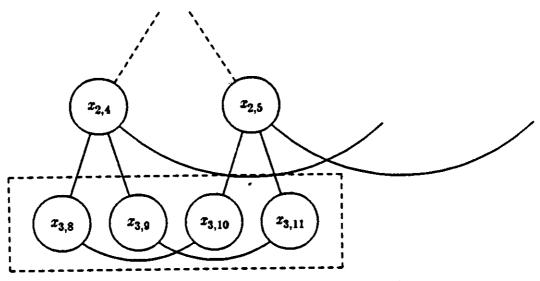

| Figure 6.2: Two ways to extend $T_{2,4,1}$ trees                         | 161 |

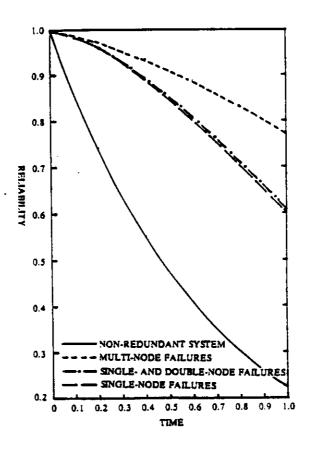

| Figure 6.3: System reliability under different failure assumptions       | 167 |

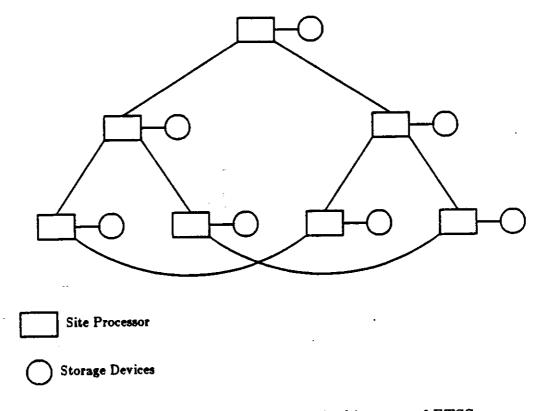

| Figure 7.1: Conceptual Hardware Architecture of FTSS                     | 174 |

| Figure 7.2: Object Block Location Hierarchy                              | 182 |

| Figure 7.3: Object Update Using Multiple Versions                        | 185 |

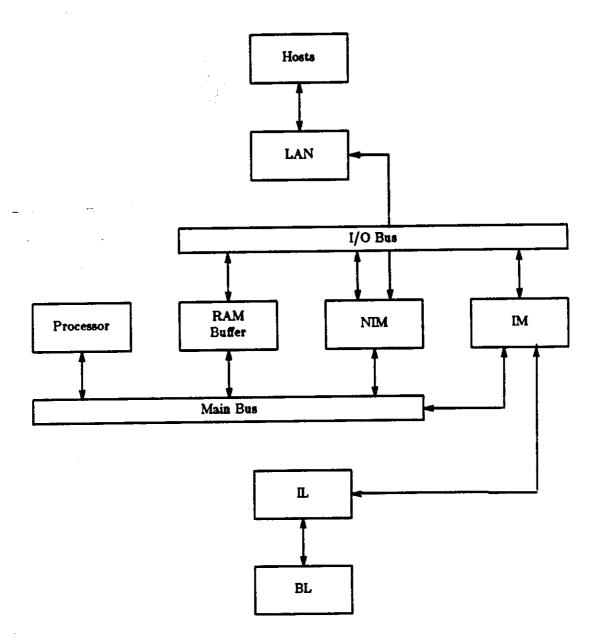

| Figure 8.1: Logical Organization of the Top Level                        | 209 |

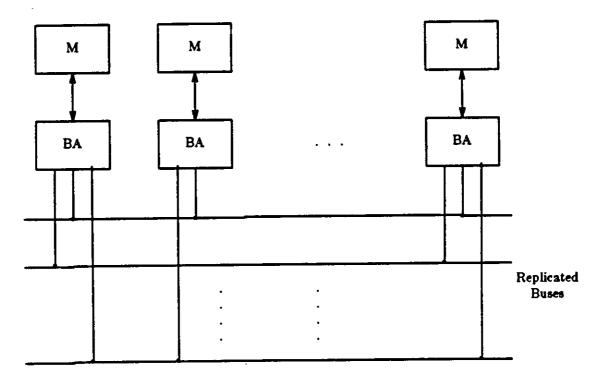

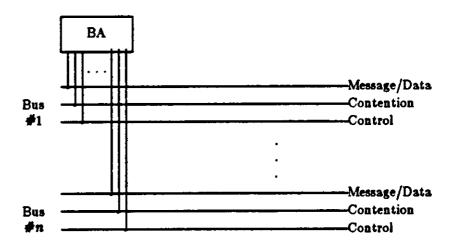

| Figure 8.2: A fault-tolerant busing structure based on distributed buses | 214 |

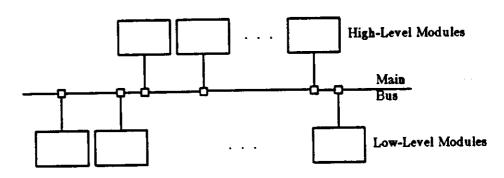

| Figure 8.3: A fault-tolerant bus architecture based on monolithic buses  | 215 |

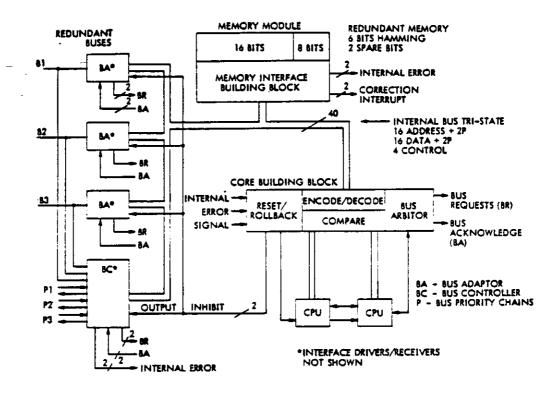

| Figure 8.4: FTSS Main Bus Architecture                                   | 218 |

| Figure 8.5: Processor Module Hierarchy                                   | 221 |

| Figure 8.6: Self-Checking Processor Module                               | 223 |

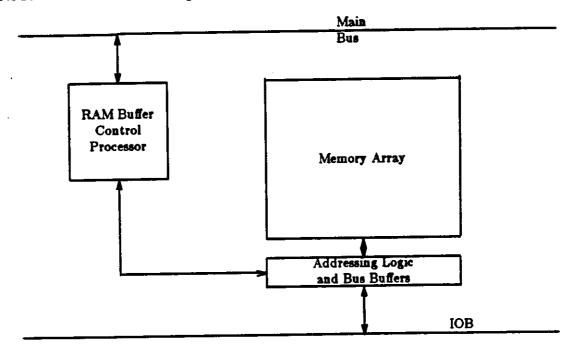

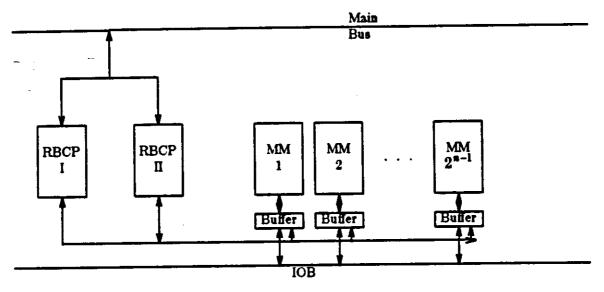

| Figure 8.7: Logical Architecture of the RAM Buffer                       | 224 |

| Figure 8.8: Modular Organization of the RAM Buffer                       | 228 |

| Figure 8.9: Logical Architecture of a Storage Site                       | 234 |

| Figure 8.10: Storage Site Architecture                                   | 235 |

| Figure 8.11: Logical view of the distributed SMS                         | 244 |

| Figure 9.1: Block Diagram for Simulation Model                           | 249 |

# LIST OF TABLES

page

| Table 5.1: ARIES Parameters for the Processor Subsystem                                      | 12   |

|----------------------------------------------------------------------------------------------|------|

| Table 5.2: ARIES Parameters for the Storage Subsystem                                        | 12   |

| Table 5.3: Time-Dependent Availability for a Bus Network                                     | - 13 |

| Table 5.4: Steady-State Availability versus Replication Factor                               | 13   |

| Table 5.5: ARIES Parameters for Site Dependencies                                            | 13   |

| Table 5.6: Steady-State Availabilities for Various PRC Partitions                            | 13   |

| Table 5.7: Availability for Multi-Connected Topology                                         | 14   |

| Table 6.1: Reliability of a T <sub>2,4,1</sub> Tree                                          | 10   |

| Table 6.2: Reliability Improvement of T <sub>2,4,1</sub> Tree                                | 10   |

| Table 6.3: Mission Time Improvement of $T_{2,4,1}$ over Non-Redundant Tree                   | 1    |

| Table 6.4a: Fault Coverage and Failure Rate at each Level                                    | 1    |

| Table 6.4b: T <sub>2,4,1</sub> Tree with Different Failure Rates and Coverages at Each Level | 1    |

| Table 9.1: Simulation Model Variables                                                        | 2    |

| Table 9.2: Baseline Simulation Values                                                        | 2    |

| Table 9.3: Baseline Simulation Results                                                       | 2    |

| Table 9.4: Effect of LAN Bandwidth on Response Time                                          | 2    |

| Table 9.5: Effect of IL Bandwidth on Response Time                                           | 2    |

| Table 9.6: Effect of Processor Bandwidth on Response Time                                    | 2    |

| Table 9.7: Effect of RAM Buffer Bandwidth on Response Time                                   | 2    |

## **ACKNOWLEDGMENTS**

This dissertation is the result of the encouragement, support, and dedication of many individuals. Although it is not possible to acknowledge them all here, they have my heartfelt thanks. The following people I would especially like to thank.

Many thanks to my dissertation advisors, Prof. David Rennels and Prof. Algirdas Avižienis who have guided me through the delicate pathways of fault-tolerance. My gratitude is also extended to the other members of my dissertation committee, Prof. K. Baker, Prof. D. S. Parker, and Prof. H. Borko. I am especially grateful to Prof. Rennels who generously gave of his time through many technical and philosophical discussions.

All the members of the Research in Distributed Processing group and the other Research Assistants with whom I have had the pleasure to work, deserve special thanks for all the assistance and support they have provided.

I am deeply indebted to my parents who motivated me to study abroad, and provided me with mental and financial support in those critical moments. Without their help, this would not have come to pass.

## **VITA**

October 3, 1950 -- Born, Kingston, Jamaica

1973 -- B.S., Northrop University, Inglewood, California

1978 -- M.S., Northrop University, Inglewood, California

1975-1981 -- Assistant Professor

Electronic Engineering Department

Northrop University, Inglewood, California

1981-1983 -- Associate Professor, Chairman

Computer Science Department

Northrop University, Inglewood, California

1983-1985 -- Post Graduate Research Engineer

Department of Computer Science

University of California, Los Angeles

## **PUBLICATIONS**

[Grey84] B.O.A. Grey, A. Avižienis, and D. Rennels, "A Fault-Tolerant Architecture for Network Storage Systems," in Proceedings 14th International Conference on Fault-Tolerant Computing, Kissimmee, Florida: June 1984, pp. 232-239.

## ABSTRACT OF THE DISSERTATION

FTSS: A Fault-Tolerant Storage System

Supporting High Availability and Security

in a Distributed Processing Environment

by

Baron Octavius A. Grey

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 1985

Professor David Rennels, Chair

In this thesis, a new approach to the design of reliable shared storage systems for local computer networks is presented. Traditional approaches have achieved reliability for the information stored in the system via replication, storing multiple copies at different sites in such a way that site failures will not immediately lead to unavailability. Other traditional approaches provide specialized file server systems and backend networks which attempt to provide higher reliability and performance through dedicated hardware and software. Our approach is quite different. We provide high reliability through the application of hardware fault-tolerance, high performance through the use of a specialized hardware architecture, and simple information management mechanisms through the use of centralization. In the system developed here, which we call FTSS, information is stored as objects, and accessed via capabilities which

are managed independently by the system.

FTSS is intended to be used in environments where fast access to large volumes of information is required. This can range from mainframe systems that only need to use it as a repository from which data is downloaded for local access when necessary, or at the other extreme, simple workstations that do not possess any online storage of their own. FTSS provides facilities that allow each host to independently define a storage environment tailored to the characteristics of its local operating system. It is arbitrarily extensible so that more storage can be added as needed. Information is automatically managed in a user-transparent way; an object is stored or accessed without any regard for its actual location or device-dependent characteristics in the system.

An important motivation for the development of FTSS is the need to provide reliable and easily-accessible storage for large numbers of distributed workstations, especially given the current trend towards workstations in engineering and office automation. FTSS portends to be an important means of allowing machines of widely differing storage and computational requirements to share an important resource with all the cost benefits that accrue from economies of scale.

#### CHAPTER 1

#### INTRODUCTION

As the cost of computing and computers decreases, there is more demand for local autonomy by system users. This has partially resulted in a proliferation of distributed processing systems consisting of a set of autonomous nodes or computing sites typically interconnected with a high-bandwidth communication subsystem over which the nodes may communicate and share information. As this decentralization takes place, new problems arise which require novel solutions in order to provide high performance and a reasonably efficient level of service to the user.

The need for decentralization is driven by many factors. Traditionally, computing resources have been provided in a centralized computing facility independently managed by some central authority. The reasons for this centralization was primarily the cost benefits of sharing expensive resources and the high performance that resulted from large mainframe computers. Decentralization was an effort to allow diverse users the opportunity to control and manage their own resources autonomously. Despite the decentralization of resources, there is still a need for information and resource sharing; hence, the interconnection of the computing sites in local computer networks.

Despite the trend towards decentralization, there are still cases where resources are so expensive that they must be shared. One such case is in the processing capabilities of the system. It is often the case that an autonomous processing site does not possess the capability to execute processes either because of the inherent size or the speed of the processor. In such cases, it is common to establish mechanisms whereby a processing site may execute its processes at another site, either directly (that is, with a priori knowledge of the mechanisms) or indirectly. Another case is in the storage capacity of a site. Often processing sites do not possess enough reliable online storage for the semi-permanent repository of information. In such cases it is common to share storage between several sites. Perhaps the most important reason for shared storage is the requirement for large online databases; such databases usually have constraints on size and performance which precludes their implementation on the existing computing sites. The unreliability of storage often results in mechanisms whereby information is replicated at several sites in the hope that storage-related failures will not make information unavailable for long periods of time.

The need to share storage system resources is even more important when one considers the recent trend towards workstations. Workstations are low-cost high-performance computing nodes that, because of their small physical size, are ideally suited for decentralized resource management. Since it is not usually cost-effective to provide large amounts of online storage for each workstation, there is an evolution towards diskless workstations which, of necessity, must obtain their storage by sharing from some centralized repository.

The decentralization of computing resources has brought about a need for information sharing which requires techniques not found in centralized facilities. Primary among these techniques are mechanisms for managing shared storage distributed among several computing nodes. This thesis examines these mechanisms and proposes alternative solutions to those that have been developed in the past. The primary issues are storage system reliability and availability, and information security. The solution proposed is to centralize storage system resources and to provide high reliability by using fault-tolerance design techniques for a storage system architecture. We propose a storage system architecture based on both file-server and backend network principles. Security is provided by extending existing techniques for the design of secure operating systems using the notions of objects and capabilities.

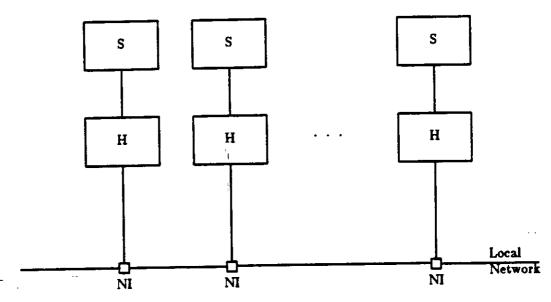

## 1.1 The Problems of Distributed Storage

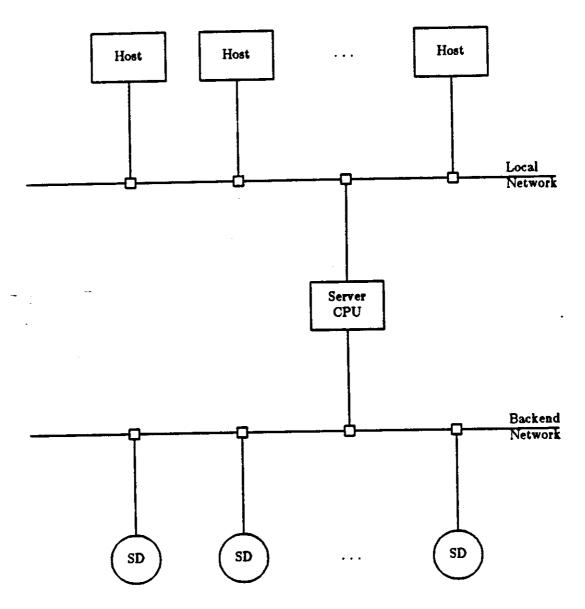

The problems associated with distributed storage are best illustrated by considering Fig. 1.1 which shows a typical local network architecture of autonomous computing sites. Each computing site consists of a Network Interface (NI), a Host Processor (H), and a Storage Subsystem (S). The storage sites are interconnected with a high-speed contention-based bus to facilitate information sharing. By distributed storage we allude to the fact that if information is to be shared between the various computing sites, each host must take part in this sharing for that portion of the information which is stored in the storage subsystem under control of the host. For example, if a host wishes to access information which is stored at another site, not only must the "local" host be involved, but the host at the remote site as well. If one imagines the sum of all the information stored in each storage site as the totality of information in the

Figure 1.1: Distributed Local Network Architecture

system, it is easy to see the nature of the distribution of storage - each physical storage subsystem S represents a (distributed) part of the system's information. It is the very nature of this physical distribution of storage in distributed processing systems that lead to a plethora of problems not encountered in centralized storage systems.

## 1.1.1 Availability

In general, users would like their stored information to be available a high percentage of the time, if not ALL the time. If we consider a single computing site for the moment, it is interesting to note that the reliability of information in the storage subsystem S is lower than the reliability of either NI, H, or S. The reason for this is because NI, H, and S are in series as far as reliability is concerned. Thus, the reliability of information in S is the product of the reliabilities of NI, H, and S. The significance of this is the fact that informa-

<sup>&</sup>lt;sup>1</sup>At least, not to the same extent.

tion in S can become unavailable either because of a failure in NI (due to hardware or software), a failure in H (either due to hardware or an operating system crash), or a failure in S itself (again due to hardware, such as a disk controller failure, or software). If information is not replicated in other computing sites, then the availability of this information is clearly a function of the reliability of the site components, assuming that system repair is not immediate.

One way to obtain higher availability in the presence of unreliable site components is to replicate information at two or more computing sites; if a site fails, there is some non-zero probability that the desired information can be accessed from another site. This, of course, depends upon the replication factor, and on the probability that not all the sites at which a replicate is stored will fail simultaneously. However, replication introduces the problem of maintaining consistency among the replicates. Several novel schemes have been proposed for maintaining data consistency in the face of site or component failures and network partitioning. However, these schemes depend to a large extent on the compatibility of storage system architectures between the storage sites. If, in the worst case, each host H has a unique storage system architecture, then it is virtually impossible to store information remotely at another site. Since we naturally expect a diversity of processor types in any autonomous network, the success of replication as the sole means of achieving high availability is questionable.

## 1.1.2 Extensibility

One of the key requirements of any storage system is the ability to easily extend the amount of online storage without perturbation of the system or loss of availability. This is not easy to do with a distributed storage architecture. The problem is caused by the close coupling of the storage subsystem S and the host processor H. In general, the capacity of S is a function of the host processors' operating system. That is, once the capacity of the operating system to address online storage is reached, there is no possibility of extending the storage subsystem's capacity without significant hardware and software modifications. In view of the trend towards autonomous workstations, it does not appear that distributed storage architectures are practical in view of their lack of extensibility.

## 1.1.3 Complexity

Distributed storage architectures require complex storage management mechanisms which offer little opportunity to optimize or "tune" for performance and efficiency gains. If information is being shared between two computing sites, it is necessary to provide mechanisms at both sites that must cooperate in information transfers. Assuming that the hosts run identical software processes, there is a fixed processing overhead which cannot be avoided; each computing site will observe a degradation in performance which is the overhead of remotely accessing this information. Said in another way, there is no way in which a remote access can appear to have been performed locally to a host processor. While it has been argued that the incidences of

<sup>&</sup>lt;sup>1</sup>Some systems solve this problem by simply adding another compatible computing site to the network and sharing storage with it.

remote access are few, there are applications in which the overhead of a remote access is a high price to pay indeed.

The added complexity in the storage management components of host operating systems is contrary to the philosophy that simplicity often leads to improved reliability. It would seem logical that schemes for offloading storage management responsibilities from host processors in local computer networks should be pursued in order to allow higher reliability in operating system software.

## 1.1.4 Functionality

In any computing system, there is a need to provide automatic archiving and incremental backup as a means of preserving the state of the system. These tasks are complicated by a distributed storage system in which naming and location are local to each site; this necessitates complex intersite protocols for mapping names to locations.

Besides the sharing of physical resources, it is useful in a distributed processing system to share application programs as well. For example, large database management programs can be shared, resulting in a significant savings in the use of system resources. Another possibility is the ability to perform dynamic load balancing by automatically migrating processes between homogeneous hosts. Again, these services are not easy to implement in a system in which naming and location mechanisms are not centralized.

### 1.1.5 Cost

Unlike the case for centralized computing centers, distributed storage architectures do not allow one to take advantage of the benefits of the economies of scale possible through resource sharing. Since each autonomous processor might use resources which cannot be directly used by other sites, there is no advantage to "pool" resources economically - this is often dictated by the requirements of the host operating system for resources with prespecified characteristics. Because of the decreasing cost per bit of online storage, it would seem that every effort should be made to take advantage of the economies of scale in storage system configurations.

## 1.2 Centralization as a Solution

There are two possible solutions to the problems of distributed storage architectures. The first is to create a logically centralized storage system on top of the distributed storage. Storage management is distributed among the computing sites in such a way that the naming and location of information in the storage system is transparent to the host processors. That this is not an elegant solution is immediately obvious when one realizes that all the attendant problems of distributed storage remain, only the details are hidden from the user. This approach has been taken by several researchers because it is relatively easy to retrofit in existing distributed systems.

The second solution is to create physically centralized facilities for storing and managing information. This approach allows one to unbundle storage from the host processors at the computing site and to manage this storage as an independent entity. By centralizing storage system resources in this way, it

is possible to either eliminate or significantly reduce most of the problems associated with distributed storage systems. There are two major directions that have been taken by researchers in this area: The first gives rise to what are called *File Server* systems, and the second to *Backend* systems.

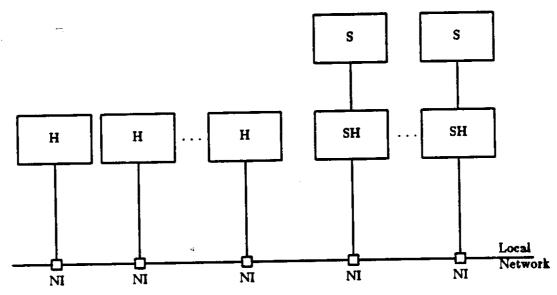

The attributes of file server systems is the unbundling of storage from host processors to specialized servers attached to the same communication network. This is illustrated in Fig. 1.2.

Figure 1.2: Distributed System with File Servers

Each file server is a series connection of NI, Server Host (SH), and storage S. The set of file servers in the network can indeed be treated as logically centralized from the rest of the network. Thus, host processors no longer need to take part directly in storage management (they simply make requests to the servers). The file server approach has some disadvantages however. First, storage is still isolated from the network by the SH's and NI's (a failure in either will lead to unavailability). Second, it is common practice to use off-the-shelf computers as SH's (at times, the same types as the host processors to take

advantage of cost benefits); there is therefore very little opportunity to improve the overall reliability of the system except by either replicating information in several servers, or to replicate the entire host processors if they should prove to be a reliability bottleneck. In short, it is difficult to apply reliable design in file server systems. Third, they do not completely solve the problems of extensibility, functionality, and cost although they do represent a significant improvement over the distributed storage case.

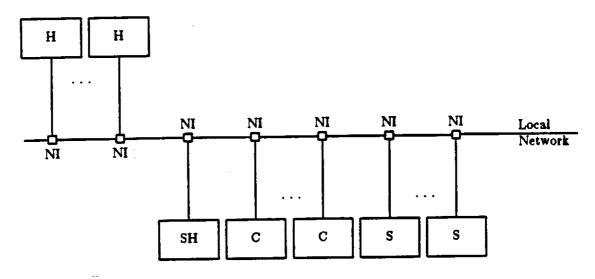

Backend storage systems are in the same spirit as file server systems they unbundle storage from the host processors so that the hosts do not have to perform global storage management. The significant difference between the two approaches is that backend systems attempt to optimize the performance, extensibility, and functionality of the resulting storage system by distributing functionality in such a way that critical functions are relegated to specialized hardware components; these components are then directly connected to the network. An example of this structure is shown in Fig. 1.3 where SH represents Server Host processors and C the specialized backend components. It is typical, for example, to have specialized components such as authentication and directory servers, Random Access Memory (RAM) buffers, job allocators, and so on. Storage components S are connected directly to the network via NI's. The primary advantage of this organization is the ease with which the system might be extended since new system components can be directly attached to the network (possibly without perturbing existing components or resulting in loss of availability). There is a disadvantage in this particular organization however: it stems from the fact that since all components are connected directly to the network, network bandwidth is consumed whenever the components must com-

Figure 1.3: Backend System with Distributed Storage System Components

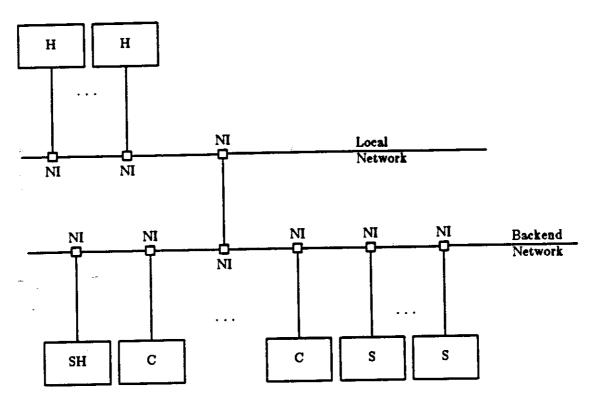

municate. Since backend storage management implies significant communication overhead, this might lead to some compromise in the bandwidth requirements of the computing sites. Since, in most contemporary local network architectures, there is a limited bus bandwidth, some effort should be made to minimize the impact of the storage subsystem upon bus bandwidth. One scheme for achieving this is illustrated in Fig. 1.4.

The compromising of network bandwidth is avoided by providing an independent busing structure for the backend components. This structure has all the advantages of the previous structure, and more, since it permits arbitrary extensibility and performance tuning without affecting the ability of the host processors to meet critical intersite communication requirements.

Much of the work that has been done on file server systems is applicable to backend systems, particularly in the software processes needed for storage management. We present in a later portion of this thesis an architecture which

Figure 1.4: Backend Storage System with Independent Communication Subsystem

is somewhat of a cross between a file server and a backend system. It uses the organizational principle of Fig. 1.4 along with established storage management principles developed for file server systems.

## 1.3 The Need for Fault-Tolerance

The goal of any shared centralized storage facility is to provide an environment in which human, software, and hardware resources can intercommunicate and be shared in a coherent way. Because of the centralized nature of the storage, there is a greater need for reliability and availability since unavailability of the facility affects all hosts (this was not the case for distributed storage where a failure at one or more sites might affect only a few hosts). Certainly, in the case where the hosts are autonomous workstations that depend

upon the availability of storage, it is important that the facility maintain a high steady-state availability.

There are two approaches to achieving high availability in a distributed system. One is to use components that never fail, and the other is to provide some form of redundancy. Since it is impossible to design systems that never fail, given a finite amount of time and resources, the latter approach is universal. One approach to the application of redundancy in reliable design is through the use of fault-tolerant design principles.

The approach taken to achieve high availability in distributed and file server systems is to replicate information in locations which have independent failure probabilities for the classes of faults expected. If a failure occurs, information may be accessed from one of the replicated sources until the failed unit is repaired, at which time an effort is made to reconcile any inconsistencies that resulted from updates during the failure interval. The fallibility of this approach is that it is not always easy to perform these reconciliations when information is spread out over multiple computing sites. The technique, however, works well for those classes of failures in which information is not lost during the failure interval (as, for example, when a host operating system crashes). However, if recovery from hardware failures in which data might be lost is critical to the system's operation, them some form of hardware faulttolerance is required. In this thesis we shall investigate an approach to the design of a Shared Centralized Fault-Tolerant Storage System (FTSS) that can be used to realize the benefits of information sharing in a centralized repository.

### 1.4 Related Work

A number of works have markedly influenced the direction taken by this research. First, the choice of a centralized architecture was directly related to our first-hand observation of and experiences with our own distributed system LOCUS [Pope81]. LOCUS, however, espouses a logically centralized file system built on top of a distributed system of autonomous machines, each of which manages a portion of the file system. LOCUS is an excellent example of the importance of transparency; it has also influenced our approach in the organization of the Storage Management System in chapter 3.

Our choice of an object model in chapter 3 was heavily influenced by the implementations of Hydra [Wulf81], the IBM System/38 [IBM78], and iMAX [Khan81], and the excellent work by Jones [Jone73] on protection in operating systems. Various backend and file server systems have influenced our implementation approach to FTSS. Notable among these are Swallow [Svob81], the Cambridge file system [Dion80], the early work done at Xerox on WFS [Swin79], and the Octopus network at Lawrence Livermore [Thor80]. Our approach to fault-tolerance using off-the-shelf components where possible, and the use of self-checking designs is influenced by the work of Avižienis [Avi78] and Rennels [Renn80]. Finally, the material on capability sealing in chapter 4 is derived from the works by Redell [Rede74] and Gifford [Giff82].

# 1.5 Organization of the Thesis

The rest of this thesis is organized in the following way. Chapter 2 discusses some key issues relating to the hardware and software architecture of shared centralized storage systems, with emphasis upon software issues; the

discussion is followed by the presentation, in chapter 3, of a kernel-based software architecture based on the abstraction of objects and capabilities, which we find to be ideally suited to the requirements developed in chapter 2. This material sets the stage for the description of a hardware architecture suitable in meeting the requirements of the abstract system developed in chapter 3; this we present first in Chapter 6, and then again in chapter 8.

The issue of protection and security in shared storage systems is sufficiently important that we have addressed the topic exclusively in chapter 4. Here we extend extant protection and security mechanisms to meet the unique requirements of our abstract model. Chapter 5 explores issues relating to information availability in distributed processing systems; it is both an experimental and analytical study of the role of information redundancy in meeting the availability goals of shared storage systems. The results of this study sets the stage for a hardware implementation of our abstract model from chapter 2.

In chapter 6 we develop a class of fault-tolerant architectures that are eminently suitable for implementation of centralized storage systems. Much of the resulting hardware discussions in the rest of the thesis is based on these architectural concepts. One might say that this chapter represents the beef of this thesis, for it is here that fault-tolerance is applied, in a way which is both cost effective and functional; cost-effective because it makes use of a natural form of redundancy, and functional because it provides the necessary functionality of a centralized storage system in a very stylized way.

Chapter 7 extends some of the abstractions developed in earlier chapters by discussing low-level mechanisms in terms of the fault-tolerant architecture developed in chapter 6. The algorithms developed impose certain constraints on the implementation of the architecture, a task which we undertake in chapter 8. Chapter 9 discusses various issues relating to system performance, largely based on our implementation approach. Chapter 10 presents a summary, with conclusions we have been able to draw from our research, and offers many suggestions for further research.

## CHAPTER 2

### ARCHITECTURAL DESIGN ISSUES

This chapter investigates and discusses various issues fundamental to the design of a shared centralized storage facility. Key among these is the need for fault-tolerance since it is required to provide adequate reliability and availability in a resource shared by many people. As work progressed it became clear that, given highly reliable hardware, many new services could be made available, simplifying operating system functions in host processors, and providing orderly mechanisms for security and for sharing information between hosts in the network. This is, of course, an intelligent storage system which applies fault-tolerant design principles in the design of the storage system itself. This added digital logic is expected to be relatively inexpensive in comparison to the shared secondary storage devices, and allows us to create unique services that can only be made available in a centralized facility of this type.

This chapter discusses the services which should be performed in the storage system. It is used to derive a set of requirements and a basic implementation approach used in the remainder of this thesis.

#### 2.1 Introduction

As described in Chapter 1, the goal of a shared centralized storage system is to provide an environment in which human, software, and hardware

resources can intercommunicate and be shared in a coherent way. In meeting this goal, there are many requirements imposed upon the logical architecture of such a system. Experiences with the design of Backend Storage Networks (BSN's) [Wats80] and File Server (FS) systems [Svob82] point out the need for:

- A logical separation of policies and mechanisms so that users can build new services out of existing ones, or define their own storage management policies.

- Application support, so that users may make use of facilities that they do not inherently possess.

- Host software minimization, so that the storage management component

of host operating systems can be effectively removed to the storage system, resulting in less costly and more reliable host operating systems.

- Multiple-host support, so that several users may access the system simultaneously, each observing an environment which is unique to a particular host.

- Reliability and availability, so that the system has a high probability of performing a particular operation to successful completion without interruption, and that it has a high probability of being able to perform a particular operation at some arbitrary time in the future.

- Extensibility in both hardware and software, so that the capabilities of the system can be increased arbitrarily with little or no perturbation upon its existing operations.

- Security, in order to prevent the unauthorized disclosure of information

among users of the system.

- Resiliency, so that the system has a high probability of performing an operation which results in a consistent state irrespective of hardware or software failures.

- Efficiency, so that the system can perform operations in a manner which makes it appear to be local to the host making the request.

In the following sections we will develop these requirements more fully, discussing as we go along various issues that are significant in their application to autonomous shared centralized storage systems.

# 2.2 Separation of Policies and Mechanisms

The first requirement we shall discuss is the need for a dichotomy between what is considered a policy, which is subject to arbitrary interpretation by a user, and a mechanism which is an inflexible entity provided by the system. Experience with the design of operating systems show this to be a powerful tool in allowing a relatively simple system to meet a diverse set of user needs and/or requirements [Wulf81, Ritc74]. Such a concept is ideally suited for a shared storage system where each user might (and usually does) have different policies regarding the way information is stored and accessed. Instead of trying to satisfy all policies a priori, a mechanism which allows each user to define his/her policy is eminently more suitable. Of course, the provision of such a mechanism should in no way constrain the user as to what kind of policies might be implemented.

The principle of separation of policies and mechanisms applies to the centralized storage system in the following way: Since the system is designed to support multiple users with diverse requirements, what is needed are mechanisms with which each user can define those policies that apply to the way in which one's information is to be accessed and manipulated. The mechanisms need to be quite general so that an arbitrary number of policies can be in effect simultaneously. One such mechanism which has proven to be quite useful in operating systems and in programming languages is the notion of abstract data types [Lisk74]. An abstract data type mechanism permits a user to define a new operation, and to specify the rules that govern the use of the operation. By providing an abstract type mechanism, users can define new operations that implement their own policy decisions. This is an important concept which is used to satisfy several of the other requirements, and is developed more fully (from an implementation point of view) in the next chapter.

# 2.3 Application Support

A centralized storage system not only permits the sharing of hardware resources, but application programs as well. By having a centralized storage system which permits the management of information in a coherent way, it is possible to provide services for users that would either be very difficult or impossible to provide otherwise. This is particularly true when there is a mix of host types in the network. Experiences with distributed operating systems supporting data transparency show that added services can be provided by judicious use of system resources [Pope81]. For example, a process may be migrated from site to site without concern for the data which the process mani-

pulates, since this data is globally accessible from any site. This allows the establishment of special *Process Servers* on the network to which host processes can be automatically migrated and serviced. This would not be possible if the location of a process is site-dependent. As another example, text files can be shared between dissimilar host types by providing automatic mapping structures in the storage system to convert between various host formats. Therefore, a user need not be concerned with the origin of a text file, as long as it can be accessed.

In a similar way, application programs can be shared by providing automatic mapping functions which are transparent to the hosts. For example, several users might share a common database without any particular knowledge of the physical location of the database, or even how the information in the database is actually represented. It is also possible for inhomogeneous hosts to share executable program modules transparently. For example, there might exist a host on the network with a specialized language translator; other hosts may make use of the translator simply by referencing it through the storage system and providing the necessary input data. The storage system could take care of all the work necessary to perform the translation and pass the appropriate results back to the user. It is not particularly difficult to provide the necessary functionality in the storage system to meet these needs. Conceptually, all that is required is the mechanism to generate the necessary mappings when they are needed—this can be easily accomplished by a data abstraction mechanism.

<sup>&</sup>lt;sup>1</sup>Process migration implies that the process migrates among sites that are capable of executing the process.

Besides the direct sharing of application programs, a centralized autonomous storage system allows hosts to augment their capabilities by making direct use of storage system facilities. For example, a host might implement a more capable file management system in the storage system than would normally be possible given the limited resources of the host.

# 2.4 Host Software Minimization

One of the important objectives of centralizing resources is to minimize the impact of resource management on hosts. This is true not only for the hardware, but the software as well. If hosts do not need to know the details of storage management, then a significant portion of the host's operating system mechanisms dealing with storage management can be removed. For example, since a host no longer needs to know the details of mapping between logical data structures and physical storage devices, device drivers can be orders of magnitude simpler. One goal of this centralized storage system is to remove the burden of storage management from the hosts, thereby making their operating systems simpler.

One approach to the solution of this problem is to provide a mechanism in the storage system with which each host can interface in such a way that host storage management primitives can be mapped into storage system primitives in a user-transparent way. For example, if a host has a primitive called read\_file which reads the contents of a file in a host-specific format, this could be passed directly to the storage system where it is mapped into equivalent storage system primitives. Normally, the host would define these mappings to ensure that the correct operations are being performed. Again, this can be

satisfied with a data abstraction mechanism.

#### 2.5 Multiple-Host Support

In order to provide as much generality as possible to meet the diverse requirements of various host systems, it is desirable to design the storage system in such a way that it can support several host types. This can range from a mix of simple diskless workstations to large mainframe computers which simply use the storage system to augment their own mass storage systems.

In view of this requirement, at issue here are the ways in which this support should be provided. The main problem is: how does one provide an environment in which multiple autonomous hosts may share a centralized storage system in a coherent way using a minimum of interface mechanisms? This problem stems from the autonomous nature of the hosts; each host type requires a unique interface with the centralized storage system. If there are a large number of such types, and if each type requires unique protocols to communicate with the storage system, the diversity of the resulting mechanisms can lead to designs which are not easy to modify or extend. Ideally, what is needed is a single mechanism upon which can be built the interface requirements of the workstations.

One approach to the solution of the problem is to use a data abstraction mechanism which permits each host to define a virtual machine in the storage system which maps host commands into storage system primitives. In principle, a host would define an abstract type, which we call a subsystem, using primitives provided by the storage system. In communicating with the storage system, the host communicates with its defined subsystem through a suitable

subsystem interface. The advantage of this approach is that only a single mechanism (data abstraction) provided by the storage system is required. Using this mechanism, several virtual machines can coexist simultaneously, each defining exactly the interface that each host type requires (note that it is not necessary to have more than one virtual machine for each host type in the network).

# 2.6 Reliability and Availability

Reliability and availability are quantitative terms used to specify, respectively, the probability of successful completion of an operation given that it was successfully started, and the probability that it will be possible to start some operation at some arbitrary time in the future. It is always desirable to have both high availability and high reliability in any storage system, whether it be centralized or distributed. There is, in fact, no reason to believe that distributed systems are any more reliable or available than centralized ones, or vice versa. Although distributed systems evolved primarily because of the need to share resources, it soon became evident that this was also a natural approach to higher reliability because of the inherent redundancy of distributed resources. The important point is not distribution, but redundancy.

While it is possible to achieve high reliability and high availability through fault-avoidance, it has been consistently demonstrated that fault-tolerance through redundancy is both a viable and cost-effective methodology of doing so [Avi78, Renn80]. The reliability and availability, then, of centralized or distributed storage systems are specified in exactly the same way; it is only the application methodology which might differ.

The application methodology in an autonomous centralized storage system of the type we are proposing is not necessarily easier than in a distributed storage system, but it is certainly less constrained. In a distributed storage system, one is constrained by the characteristics of extant storage resources, and by the network configuration itself. This is not the case with a centralized facility where one is more-or-less free to choose an architecture and the devices which are used for storage. In chapter 6 we avail ourselves of this right by proposing a fault-tolerant architecture which we believe to be ideally suited to the requirements of network storage systems. This architecture espouses the principle of redundancy while being arbitrarily extensible at the same time.

#### 2.7 Extensibility

With respect to shared storage, extensibility implies the ability to increase the level of service that the storage system provides for the users, in a transparent way. The issue of transparency is an important one. It should be possible to change the physical configuration of the system (for example, adding disks and processors, or removing hardware for repair) without disturbing ongoing services. As another example, we would like the user to be able to create new services (or perhaps new policies for existing services) in a more-orless arbitrary manner. Therefore, there is a need for both hardware and software extensibility.

## 2.7.1 Hardware Extensibility

Hardware extensibility is achievable through architectures that permit online hardware modifications. For example, hardware can be designed in such a way that replaceable or new components are electrically isolated from existing components, achievable through the use of transformer coupling or optical isolation. This requirement is particularly important in view of the highavailability requirement of the system; if a component fails, it should be replaceable without resulting in system downtime.

# 2.7.2 Software Extensibility

One way to achieve software extensibility is to provide an environment in which users can define their own abstractions. This is commonly referred to as abstract data typing, or simply typing. A user creates an abstract data type (or simply, a type) by defining an operator and the rules governing the use of that operator — the operations of the type. By allowing users to create (or delete) abstract data types at will, software extensibility is achieved. What is therefore needed are mechanisms that will permit this dynamic creation and destruction of abstract data types.

Data abstraction alone is not sufficient to provide true software extensibility. The software must in fact be designed to be easily modifiable and upgradable. It is desirable for example to be able to install software updates online while the system is still in operation. Furthermore, if the software is distributed throughout the system, with each component communicating with others over communication links using a protocol, it is necessary to design the protocols so that new services can be added or deleted without requiring protocol revision. One approach to meeting these needs is modularity. By designing the software as a set of modules with well-defined interfaces, new modules can be added or the internal details of a module changed without significant perturbation on the overall function of the system's software.

#### 2.8 Security

In an environment where multiple users must share a common resource, the prevention of unauthorized access of information is vitally important. There has recently been much furor over the security of information in online systems such as banking and military systems. There is no reason to believe that systems such as that proposed in this thesis will not find applications in these areas. Therefore, security mechanisms should be an integral part of the system's design.

There are two aspects to security: information security, and physical security. Information security pertains to the unauthorized disclosure of information in a computer system, while physical security concerns the susceptibility of the system to physical attacks. Although the notion of centralization tends to support physical security, since the storage devices can be kept under common surveillance, we do not consider aspects of physical security in this thesis. On the other hand, information security must be given serious consideration because of the inherent properties of contemporary computing systems. Because of the need for high performance in information management, the density of information on storage devices is continually increasing. As this density increases, the possibility of data interaction between independent users increases, particularly when failures manifest themselves. However, interactions due to failures are not the only threats to security. As pointed out in [Denn82], information security can be subverted by eavesdropping, tampering, browsing, searching, inference, wanton or accidental destruction, collusion and masquerading.

In an autonomous centralized storage system, what is ideally needed is a single security mechanism whereby arbitrary security policies can be implemented. One of the biggest problems with designing secure systems is the diversity of security mechanisms that are used; each such mechanism requires independent verification in addition to the complexities of interfacing them. It should be possible for each autonomous host to use this mechanism to extend those security mechanisms already extant in the host, or alternatively to use the mechanism of the storage system to augment that already provided. In chapter 4 we show how a single mechanism based on access controls can be used to implement arbitrary security policies.

#### 2.9 Resiliency

Resiliency is concerned with the consistency of information in the storage system. It introduces the notion of atomicity which has the property that either an action is performed to completion, or its effects are not observable in the system [Lamp81]. There are two conditions under which information consistency is desirable: 1) whenever software failures occur (such as operating system crashes in either the hosts or the storage system), and 2) whenever hardware failures occur. What is therefore needed is a mechanism which will, with high probability, provide for consistency under the specified conditions. One useful paradigm for providing consistency under these conditions is the notion of a transaction.

# 2.9.1 The Transaction Paradigm

The classical model of a transaction, as described by [Gray78], defines a mechanism for constructing reliable database systems. In this model, transactions are defined as arbitrary collections of operations, or actions delimited by two markers: Begin\_Transaction and End\_Transaction, and have the following special properties:

- Either all or none of a transaction's operations are performed. This property is usually called failure atomicity.

- If a transaction completes successfully, the system state always satisfies its invariant predicate. This property is usually called internal consistency.

- If a transaction completes successfully, the system state corresponds to external perceptions of it. This property is usually called external consistency.

- If a transaction completes successfully, the system state reflects, as closely as possible, the correct response to external stimuli. This property is usually called *congruity*.

- If a transaction completes successfully, the results of its actions will never subsequently be lost. This property is usually called permanence.

- If several transactions execute concurrently, they affect the database as if they were executed serially in some order. This property is usually called *serializability*.

An incomplete transaction cannot reveal results to other transactions, in order to prevent cascading aborts if the incomplete transaction must subsequently be undone.

If a transaction is performed successfully, it is said to have committed; if it was started but failed, then it is said to have aborted.

Transactions are extremely useful in the design of any system since they reduce the burden on application programmers by simplifying the treatment of failures and concurrency. The property of failure atomicity guarantees that when a transaction is interrupted by a failure (operating system crash or hardware failure), its partial results are undone. Serializability insures that other concurrently executing transactions cannot observe any inconsistencies brought about through the temporary violation of consistency constraints by programmers. Prevention of cascading aborts limits the amount of effort required to recover from a failure. If it were possible to design a generalized transaction mechanism in a centralized storage system, issues relating to concurrency control, sharing, and failure recovery of information could be handled by a single mechanism [Spec83]. has studied some of the requirements for the applications of transactions in general-purpose distributed systems, and a large portion of the significant results are applicable in this context. The reader is referred to that work for a more in-depth discussion of the transaction methodology in distributed systems. Svobodova [Svob82] discusses the importance and design issues of transactions in file server systems, but not in the context of a generalized mechanism supporting abstract types; it is however, a useful report since it discusses various approaches to the application of transactions in contemporary file server systems (some of which have been actually constructed).

#### 2.10 Efficiency

Centralizing storage resources should not unduly impact the performance of the network. In fact, it would be desirable to design the system in such a way that accesses appear to be local to each host so that the system is essentially transparent (from the user's viewpoint). There are several potential bottlenecks to performance in these kinds of systems. First, the need to transport information across a shared network could be a bottleneck, depending upon the bandwidth of the network, and the characteristic and volume of the offered traffic. Second, the performance of the storage system itself; especially so in view of the need to maintain interfaces for each host which are largely implemented in software. In chapter 8 we propose hardware and software architectures which are meant to provide a system which will meet the performance requirements of a wide range of host systems.

#### 2.11 Summary

In this chapter we have investigated a number of issues important in the design of autonomous shared storage systems. In some cases we proposed approaches which provide viable solutions to an issue. In the remainder of this thesis, we explore these solutions in more detail. In the next chapter we develop a system model and propose the implementation of a storage management system which meets all of the software requirements discussed in this chapter.

# CHAPTER 3 SOFTWARE SYSTEM MODEL

In this chapter, the goal is to describe a software architecture for a Storage Management System (SMS) that attempts to meet the requirements discussed in the previous chapter. In so doing, we first postulate a strawman hardware architecture which serves as a framework for the development of the software architecture. A generalized software model is discussed, after which we present a software design overview, and finally an implementation of the architecture.

## 3.1 Strawman Storage System

In general, it is very difficult to structure a software architecture without some knowledge of the hardware on which it will eventually run. This is true for such areas as memory management, process management, and I/O. However, it is still possible to base the design on abstractions which can be mapped onto whatever hardware is chosen in the final implementation. It is normally the case, however, that hardware peculiarities will severely impact the software architecture. For example, the design of the paging mechanism in Hydra [Wulf81] and the I/O mechanism of the UCLA Data Secure Unix [Pope78] were direct consequences of the underlying hardware. PSOS [Neum77], on the other hand, appears to be an operating system which was designed with very few hardware dependencies; one suspects, however, that its

implementation was not without compromise, for reasons of efficiency.

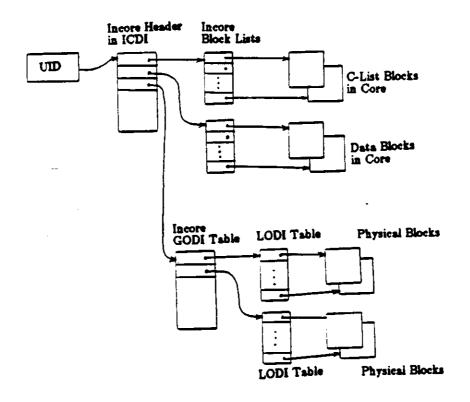

The approach we will take, is to postulate a strawman hardware architecture on which to specify the software architecture. This hardware architecture hides many of the detailed fault-tolerance techniques and multi-computer implementations which will be developed later, but it is idealized in such a way that the software architecture can be transferred to the detailed design in later chapters. This architecture is shown in Fig. 3.1.

The strawman storage system architecture as shown in Fig. 3.1 consists of a set of hosts connected to a local network, and the storage system connected to the same network. All connections to the network are assumed to be via a suitable network interface. We assume the network to be of the "ethernet" variety [Metc80], with whatever transmission speed is needed to do the job. We assume that such a network and its interfaces provide perfectly reliable communication at the link level, assuming that low-level fault-tolerance to be added later will not have a major structural or functional impact on the software architecture. Furthermore, we assume that the storage system proper consists of a server computer to which is attached a number of high-capacity disk storage units. This computer is assumed to have as high a speed as is needed and is fault-free. The disk units communicate with the server CPU via a very high rate fault-free communication subsystem. Each disk unit is managed by a single fault-free processor which resides logically between the communication subsystem and the unit. These processors will be used primarily to manage the information stored at each disk unit. The one thing that we do not assume to be fault-free is the disks. They may fail, but we impose the requirement that whenever such failures occur they must be detected by the

Figure 3.1: Architecture of SMS

processors which will prevent damaged data from propagating. The need to replicate information on independent disks and the ability to recover is a fundamental requirement of the SMS which must be dealt with in the strawman design to be transferable to the final architecture.

#### 3.2 A Generalized Software Model